提高功率密度和性能,同时降低成本,从来都是功率半导体技术的前进方向。本文指出,在可预见的未来,这个趋势还将继续下去,并且新型半导体材料的发展甚至会加剧这一趋势。传统的硅材料与诸如碳化硅(SiC)和氮化镓(GaN)等新材料的一个共同发展趋势是,提高电流密度,并且需要逐步实现高达200℃的更高工作温度。主要受要求高得多的负载和温度循环能力的限制,如今的封装技术尚不能处理高于200℃的温度。另一个共同发展趋势是,各种新老材料的半导体都致力于加快开关速度,以降低器件内部损耗,从而提高电流承受能力。本文还表明,朝着这个方向发展,降低开关损耗的潜力巨大(约7倍),并且阐述了在低电感连接技术方面,封装和系统设置面临的挑战。

1.功率半导体行业的基本原则

自功率半导体问世以来,始终只有一条创新和优化途径:提高功率密度和性能,同时降低成本。其推动力一直源于半导体本身,封装和安装技术,和通过日益缩小体积和不断降低功率损耗来实现新功能的全新系统设置。提高性能和降低成本是其永恒的结果。

这貌似一条与宇宙熵理论相呼应的基本原则。在一个封闭系统中,熵只能增大:

E → ∞. (1)

从非严格科学意义上讲,功率半导体的发展趋势也是如此:

p/c → ∞, (2)

其中

p = 性能(就经济优势而言)

c = 器件成本

性能的每一次提升都有其用武之地。在具体的应用中,性能提升转化为系统优势,创造出相应的经济效益。如果性能提升意味着增加成本,那么其带来的经济优势必须要超过增加的成本。另一条途径只能是,在保持性能不变的情况下,不断降低成本。这意味着技术水平滞足不前,只能持续较短的时间。

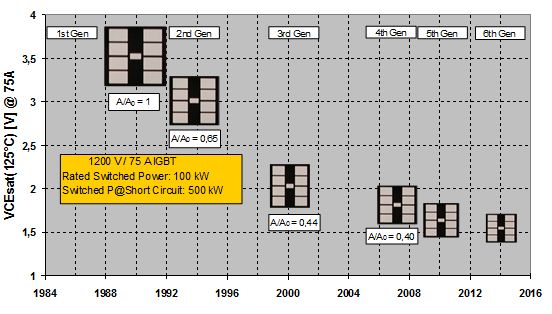

2.功率器件的微型化之路

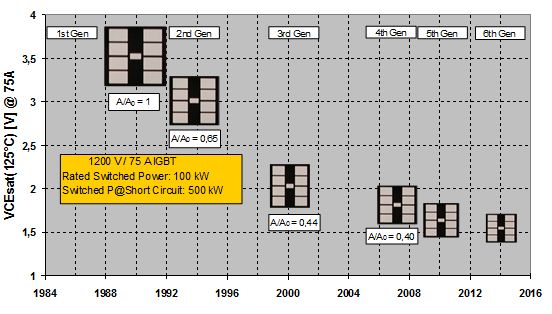

遵循这条原则,在器件的额定电流和电压不变的情况下,功率半导体的尺寸和体积大幅缩小。如图1所示。

图1:各代1200V-75A IGBT器件在恒定开关功率下的通态损耗

qHBednc

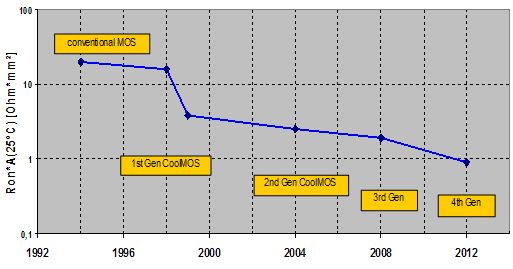

如今的IGBT同第一代IGBT一样,以1200V/75A和100kW开关功率运行,但不同的是,其尺寸缩小了五分之三。单极性器件的体积缩小幅度甚至更大,如图2所示。

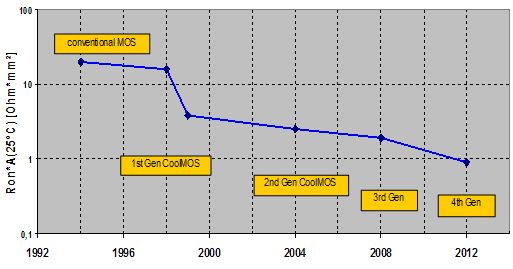

自1993年以来,600V MOSFET的尺寸缩小了十倍(按特定Ron*A计算),这意味着如今仅需十分之一的有效面积,就能实现相同的Ron。

图2:各代600 V MOSFET器件按Ron*A的有源区

qHBednc

仅使用相同的材料——硅,但通过采用更加先进的补偿技术,单极性器件和双极性器件都可以实现这样的性能提升。下文将对此进行说明。

《电子设计技术》网站版权所有,谢绝转载

{pagination}

3.材料的物理功能以及如何利用硅技术克服其弊端

3.1 补偿原理——MOSFET双极器件

电流垂直流通的标准功率MOSFET的通态电阻,通常取决于其阻断电压以及所需漏极区掺杂级和厚度。根据这种依赖关系,可以推导出电压与Ron之间的简单关系[3]

Ron ~ Vbr2,5. (3)

也就是说,对于特定阻断电压,Ron存在一个固有限值。所有材料都不能突破这一限值,只不过每种材料的固有限值各不相同。只要材料中包含均匀掺杂,就必然产生这种关系。多年来,这一直是一个无法逾越的界限。但是,一旦实现彼此相距足够近的N型掺杂区和P型掺杂区交替排布的掺杂结,相应的耗尽层将对提高电压(低于临界击穿场强)进行补偿,那么,这种关系将变为纯粹的正比关系

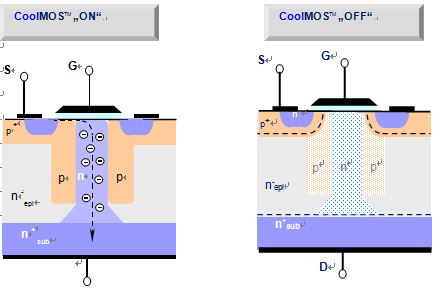

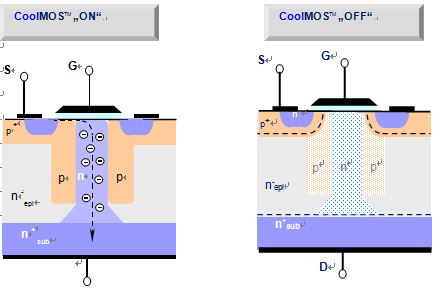

Ron ~ Vbr. (4)

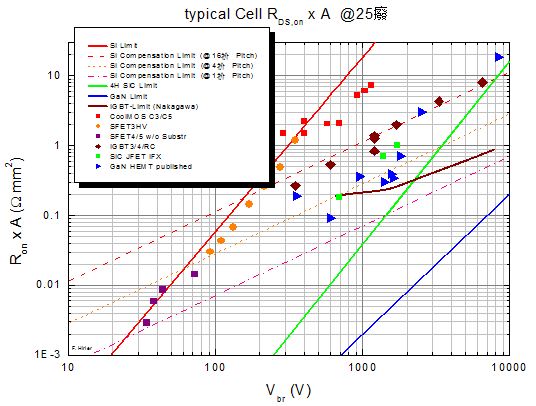

CoolMOS?器件的补偿原理如图3所示[4]。在导通状态下,重掺杂N型区充当电阻极低的导体,在关断状态下,并行的N型和P型掺杂区完全耗尽,仿佛具备矩形场强曲线的本征区(当正电荷与负电荷相等时)。图5用边界线(实线和虚线)表明了现有的采用硅、碳化硅、氮化镓等材料的MOSFET器件以及双极性IGBT器件(@额定电流)中存在的关系(3)和关系(4)[5]。可以看出,基本上所有补偿性器件都服从关系(4)。从这个意义上讲,双极性IGBT器件也被算作补偿性器件,因为在导通状态下,空穴-电子对在等离子体中得到理想补偿。

图3:CoolMOS器件的补偿原理

qHBednc

(1)导通状态下:重掺杂区在漂移区内构成“短路”;(2)关断状态下:如果施加了VDS,空间电荷区扩散整个外延层=> 无自由载流子 =>高击穿电压

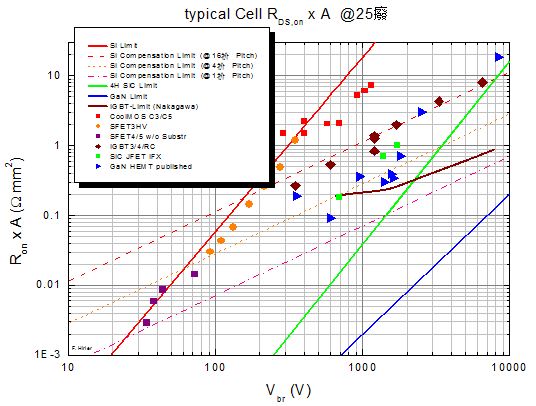

图5:采用硅、碳化硅、氮化镓等材料的MOSFET器件以及双极IGBT器件(@额定电流)的设计阻断电压与Ron*A的关系

qHBednc

显然,代表硅器件的红色实线,被代表CoolMOS和低压MOSFET(SFET器件)的点超越,并且也被代表16μm沟道间距的IGBT器件超越。它的界线由红色虚线所代表。代表碳化硅器件的绿色界限线,与代表硅器件的实线呈恒定系数的位移关系。实际的碳化硅JFET器件仍与该界限相距系数5,这表明即使未进行补偿,其潜力依然巨大!新近报告的(水平)氮化镓器件与水平器件的理论界限(蓝色实线)相距甚至更远!

3.2新材料——更多挑战

从图1和图2以及上文的讨论,可以显而易见地推断出,半导体功率器件早已踏上微型化之路,并将沿着这条道路继续走下去,就连硅器件也将沿着这条道路前进(Nakagawa线[6],图5中的棕色实线)。

随着硅器件的电流密度日益提高,并且碳化硅或氮化镓器件的电流密度变得更高(如果1200V硅器件的电流密度为200 A/cm2,那么,碳化硅器件的电流密度将是其两倍或三倍,而氮化镓器件的电流密度则甚至更高),一些问题变得越来越严重,现有的封装和连接技术已无法应对。

包括:

- 低阻抗连接(电阻和电感)挑战

- 芯片的更高热阻(和更低热容)要求更高芯片温度和更好的热连接

- 处理封装的更高电流密度

- 消散更小尺寸的器件所产生的同样热量

当然,更先进的半导体技术有助于降低功率耗散,但是,由于不能摆脱关系(2)的限制,不论过去、现在还是将来,这个方法的收效甚微。

4.微型化器件提出封装微型化挑战

4.1封装的微型化之路

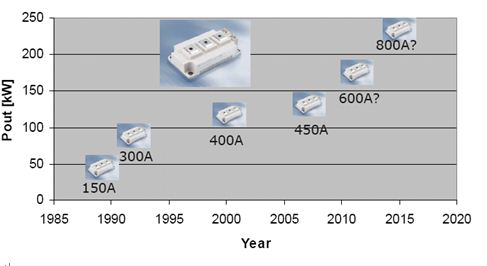

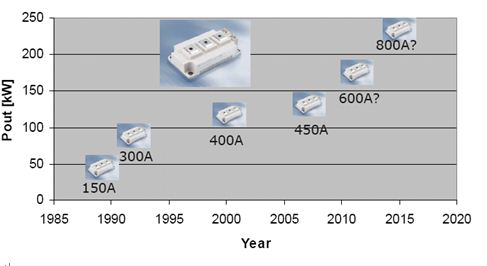

过去25年,制定了若干适用于高功率双极性开关的封装标准,其中最重要的可能是34 mm和62 mm标准。首先是34 mm的2x 50 A开关和62 mm的2x150A开关。然后,新一代芯片提高了现有封装的电流。封装的微型化之路如图6所示,带问号的电流值表示未来的预测值。

图6:采用3个1200V 62 mm半桥模块的换流器的输出功率的变化

qHBednc

微型化的另一条途径是,缩小封装尺寸,并在更小的封装中实现相同的额定电流,如图7所示。

图7:在尺寸更小的封装中实现相同额定电流(功率输出)的微型化之路

qHBednc

《电子设计技术》网站版权所有,谢绝转载

{pagination}

4.2要求改善散热性能和提高结温——对功率循环能力提出挑战

在上述所有芯片和封装的微型化历程中,改善散热性能始终是最大限度地缩小器件尺寸所遵循的准则。随着半导体器件的额定电流越来越高,仅仅降低损耗(通态损耗和开关损耗)不能完全满足改善散热性能的需求。

过去,采用了多种封装技术来充分提高芯片的电流承受能力:

- 使用可支持更高结温的绝缘材料

- 使用更薄的绝缘材料(满足节省散热材料的需求)

- 使用液冷技术(水、喷水、散热管)

- 直接在DBC上连接散热器

- 采用双面散热设计

- 使用更先进的连接技术

- 改善更高芯片工作温度条件下的电流性能

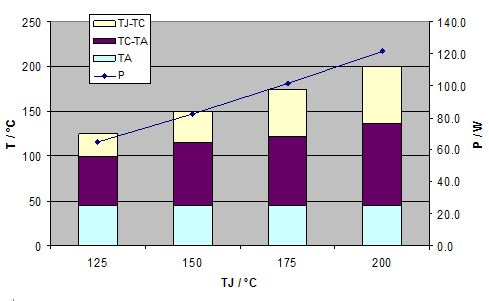

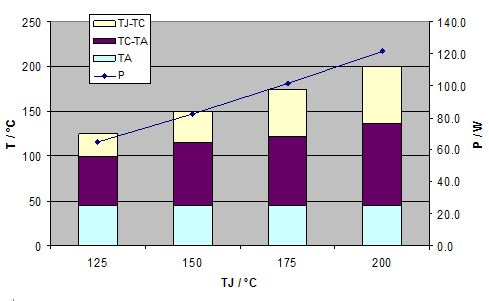

如今,上述所有方法都已得以应用,但是,这些方法各有长短,应用范围各有限制。不过,未来有些技术可能得到进一步发展,实现更好的性能。特别是,提高芯片工作温度Tjop,是非常有希望同时提高输出功率和缩小芯片尺寸的一举两得的方法。2008年PCIM大会上的一篇主题演讲已对此详加阐述[7]。对于现有的封装,风冷散热系统的性能如图8所示。如果连接技术保持不变,将Tjop从150°C升高至200°C,可使功耗增加40%,从而提高输出功率。

硅芯片已经可以实现这样高的Tjop,并且采用新型碳化硅材料的芯片甚至可以更加容易地实现这样高的Tjop,但其局限性是连接系统的功率循环寿命[7]。温度摆动越大,焊接线越容易更早断开。将Tjop从150°C升高至200°C,意味着互连系统的循环能力需要提高10倍。必须在芯片的正面和背面都采用新的连接技术,以实现这一点[7]。

图8:在风冷散热系统中通过提高Tjop提高功率密度(以EconoPACK 3为例)

qHBednc

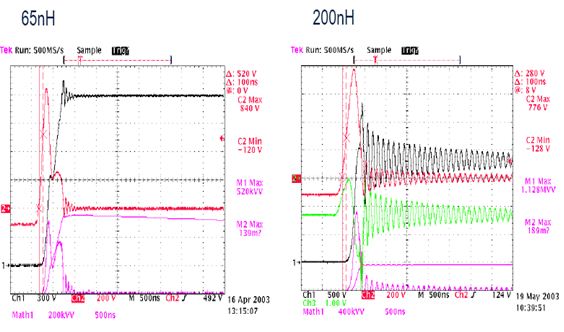

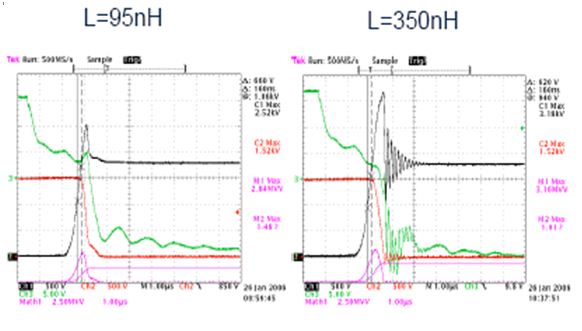

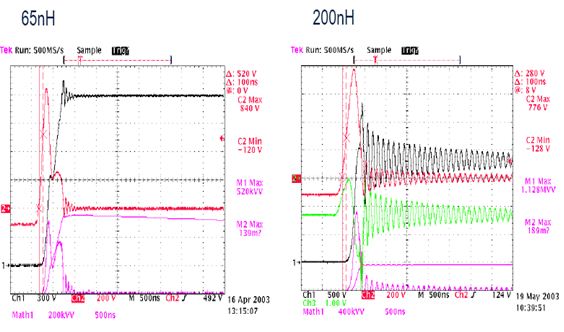

4.3要求低阻抗连接

芯片的电流密度越高,每条焊接线上流过的电流越大,循环能力的问题,以及所产生的寄生电感中的电流变化率(di/dt)问题就越严重。当然,只要芯片上有足够大的空间,可以使用多条焊接线,但事实上,芯片上的空间是极其有限的,特别是电压级别较低的芯片。但是,高压芯片也存在高电感连接,特别是系统中的高杂散电感,会引起严重的电压过冲和振荡问题,如图9所示。

图9:在采用低拖尾电荷二极管的1200A/3,3kV模块中,IGBT开通状态及其寄生电感对反向恢复的影响

qHBednc

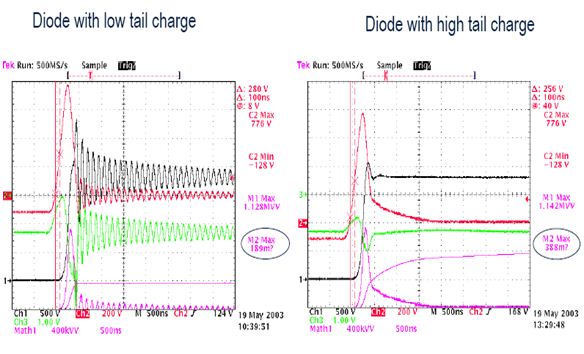

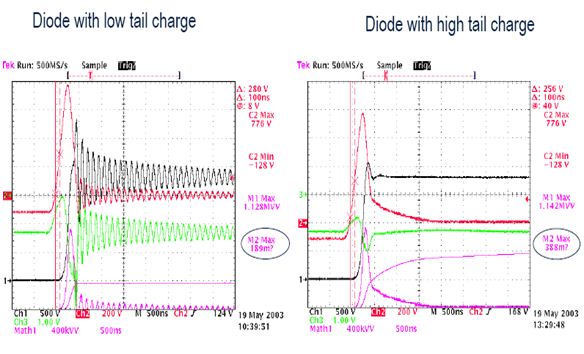

高电感会造成电压过冲,使得深入二极管的等离子体区,过早释放电荷,以至于在随后的拖尾阶段没有电荷,因而产生很高的电压过冲和严重的振荡。使用具备较高拖尾电荷的二极管能有所助益,但这会增加损耗,如图10所示,损耗增加了一倍。当然,总是可以使用具备较高拖尾电荷、较高米勒电容和较大栅极晶体管等等的速度较慢的开关器件,来减弱振荡。但所有这些措施无一例外地都会导致器件的损耗增加,加大半导体器件的散热难度。

图10:IGBT导通状态:借助高二极管拖尾电荷来补偿高杂散电感——损耗加倍(下方的粉红色线条)

qHBednc

图10:IGBT导通状态:借助高二极管拖尾电荷来补偿高杂散电感——损耗加倍(下方的粉红色线条)

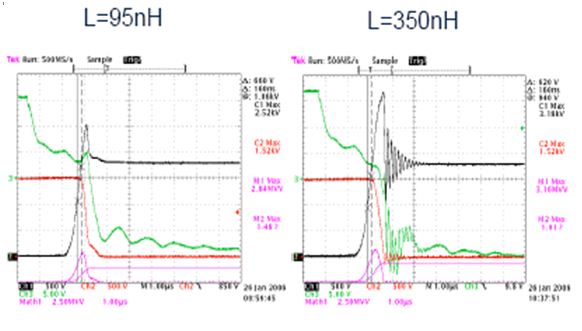

关断状态下,杂散电感使开关器件产生了很高的电压过冲,如图11所示。

图11:不同寄生电感条件下的的IGBT关断状态(3,3kV/1200A模块)——过冲电压限制了可用低压范围并增加了损耗

qHBednc

过冲电压限制了可用工作电压,通常通过使用具备较高额定电压的器件来补偿——当然相应的成本更高,损耗也更高!

此外,也可以使用负反馈回路来抑制振荡和电压过冲,但是,在大多数情况下,这同时也会导致损耗增加。

要降低在所有运行条件下的损耗和振荡,唯一最好的办法是,像如今的普通模块和系统设置通常所做的那样,大幅降低杂散电感。

《电子设计技术》网站版权所有,谢绝转载

{pagination}

5.硅半导体以及未来的碳化硅和氮化镓半导体的开关速度将越来越快

新一代硅器件,不论其电压等级如何,都日益要求低阻抗的模块和系统设置。当然,在仍需要较高电流的情况下,电压越低,越需要降低模块和系统设置的阻抗。特别地,对于直流连接电压高达450 V,最高电流在600安培左右的全混合电动汽车和纯电动汽车的逆变器设置,更是这种情况。在这种应用中,如果未能将模块和系统设置精心设计到杂散电感低于25 nH,很快就会达到600 V器件的阻断电压(600A开关电流保持达100ns,仍会导致150V峰值!)。

同样地,解决办法是使用阻断电压较高的器件和/或开关速度较慢的器件,但是,这些方法都会增加静态和动态损耗。

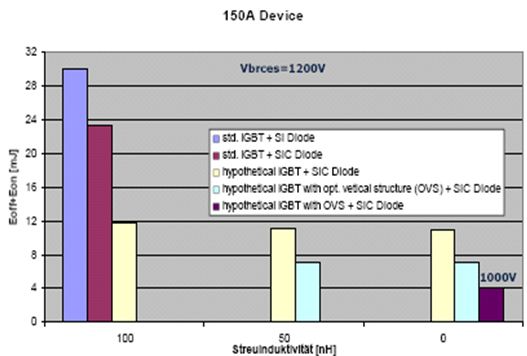

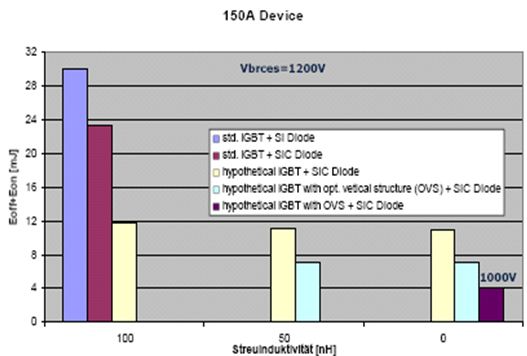

使用碳化硅二极管来代替双极二极管,可以显著降低导通损耗和电压过冲。反向恢复电荷被减至仅剩二极管耗尽层中的极低容性电荷。其结果是降低开通损耗(IGBT和二极管),如图12所示。图中以总杂散电感为100 nH 的1200V/150A器件(对应于上文提到的电流为600 A左右时的25 nH杂散电感)为基础,模拟了当今的标准器件组合IGBT +双极二极管(左侧组,蓝色柱)与IGBT +碳化硅二极管对(左侧组,紫色柱)的开关损耗(Eon+Eoff)。由于碳化硅二极管中没有反向恢复电荷,仅降低了开通损耗,使得总损耗降低了20%(另请参阅[8])。

图12:1200V / 150A IGBT(相同Vcesat)模拟总开关损耗比较

qHBednc

多种不同的杂散电感条件下,标准IGBT与硅PN二极管(左侧组,蓝色柱)、标准IGBT与碳化硅二极管(左侧组,紫色柱)和未来的高速开关IGBT与碳化硅二极管(左侧组,浅黄色柱)

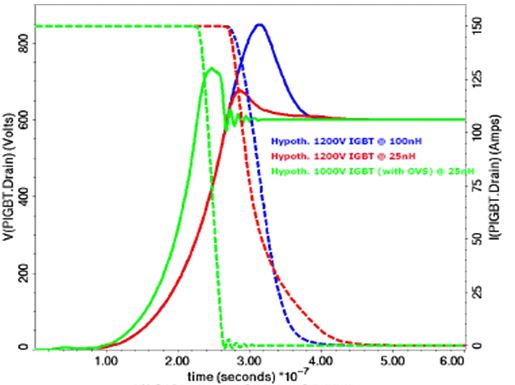

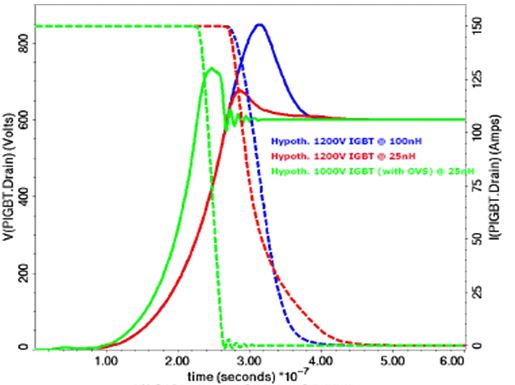

在这样的配置中,IGBT可以得以优化,实现高速开关(仍在恒定Vcesat条件下)开通和关断。假设器件(左侧组,浅黄色柱)便是这种情况,其总损耗仅比标准器件降低40%。此外,通过降低杂散电感,以及额外实现垂直器件优化(OVS)以减少储存电荷(仍在相同Vcesat条件下),可以进一步将损耗再降低40%。

由于电流为150A时,杂散电感仅为50 nH(对应于电流为1000 A时杂散电感为7.5 nH),因此最高直流连接电压为800V的应用,不再需要使用1200V阻断电压器件。如果该器件的额定阻断电压仅为1000V,那么,损耗还可再降低40%。最终,总共可将开关损耗降低7倍以上!

图13:图12中的模拟IGBT二极管组合的关断波形,表明优化器件以实现具备极低杂散电感的高速开关的潜力

qHBednc

要让像JFET或MOSFET这样的碳化硅有源器件,或未来的氮化镓器件充分发挥其潜力,必须实现所有这些优化措施——当然,必须始终遵循关系(2)!

6.展望

正如已在第3节和第5节中讨论的,诸如碳化硅和氮化镓等新型半导体材料的潜力是,一方面可以实现高速开关,另一方面可以实现极低的Ron*A,而没有像IGBT和双极性二极管那样的阈值。其次,另一个优点是可以支持更高温度,不过这一点并不实用,因为目前的封装技术尚不足以充分利用硅材料可支持的200°C温度,甚或碳化硅或氮化镓可支持的更高温度!因此,要说新材料的优势在于温度方面,其实很牵强。

要充分发挥新材料所具备的更好电气特征,绝对有必要开发出具备更出色的散热和电子性能的封装技术,以实现极低杂散电感,并将温度摆动更大条件下的负载循环能力提高10到20倍。未来的硅器件也需要走同样的优化道路。

依照关系(2),在碳化硅JFET器件中集成二极管,以实现与碳化硅肖特基二极管相当的性能,大有裨益。这有助于快速将碳化硅器件用于较早体现出关系(2)的应用,也就是说,可以在尺寸较小的模块中实现较高可用电流密度,从而提高特殊应用的功率输出。

本文采用了英飞凌科技工业与多元化市场(IMM)业务部开展的多项测试和模拟的数据。特别地,我与F. Pfirsch和T. Raker就他们开展的模拟,以及与R. Bayerer就封装和封装技术的未来前景展开的讨论,给了我很多启发,在此谨向他们表示诚挚的谢意!

《电子设计技术》网站版权所有,谢绝转载

最前沿的电子设计资讯

最前沿的电子设计资讯