本文提出了一种新的方法来实现双向闭锁箝位。通过在形成箝位器件两个引脚的高掺杂有效区域确定互补“T”形和孤岛,高电平注入再生反馈期间的电子驱动或空穴驱动小载荷电流增益得到了优化。

一、引言

恶劣条件下工作的集成电路(IC)不断将越来越多的功能合并,这就需要改进器件与电路设计策略,以便提升鲁棒性,并尽可能缩减IC面积。由于受到更严格的设计、封装和成本限制,面向FlexRay [1]、局域互连网络和控制区域网络收发器[2]等应用的保护架构也在进行重新设计,以便将额外保护元件数量降至最低,同时提供所需的鲁棒性。这些鲁棒性要求包括严格遵守上电静电放电 (ESD) 和电磁干扰抗扰度要求。要实现更优的收发器架构,最好选择紧凑及具有高电流处理能力的双向闭锁电压箝位器件。在0.18 μm以下的先进高压技术中,这是一项挑战。此外,这些电压箝位器件的闭锁电压必须略高于±45 V,可变通态保持电压通常在±(25–40) V范围内。

用于高压双向工作的保护器件在精密通信基础设施接口开发中的重要性越来越明显。具体而言,单芯片二维控制箝位器件具有低保持电压、高品质因数 (FOM) 比(FOM指单位面积内的最大100 ns传输线脉冲 (TLP)),消费类应用文献中还提出了自定义双向闭锁条件[3]、[4]。目前的双向导通器件存在限制,很难在高应力条件下既调整双向通态保持电压,又不显著降低响应时间和箝位器件的性能。人们已经尝试通过大幅增加器件引脚间距(如NPN晶体管中发射极和集电极的间距)来调整通态保持电压,以满足严格的上电ESD/EMI要求[5]。理论上,双极性晶体管的阶跃恢复保持电压会随着电流增益的减小而增加。这种设计调整通常用于采用传统智能电源技术制造的保护器件[6]。另一方面,增加器件引脚间距会对箝位性能造成负面影响,会使得箝位变慢、面积增加,还会导致寄生器件对基板意外击穿。一种改进后的方法可有效用于汽车IC系统化器件优化,优化的重点是对箝位双极性闭锁特征进行二维技术计算机辅助设计分析[7]。这里介绍一种新型三维导通控制技术,用于在器件通态响应期间进一步优化平衡载荷注入,有助于理解这种方法。

本文提出了一种新的方法来实现双向闭锁箝位。通过在形成箝位器件两个引脚的高掺杂有效区域确定互补“T”形和孤岛,高电平注入再生反馈期间的电子驱动或空穴驱动小载荷电流增益得到了优化,同时还没有增加期间两个引脚的间距,从而获得了紧凑的双向高压闭锁箝位器件,保持电压在±25和±40 V之间,同时还具备高电流处理能力。

二、保护箝位器件定义

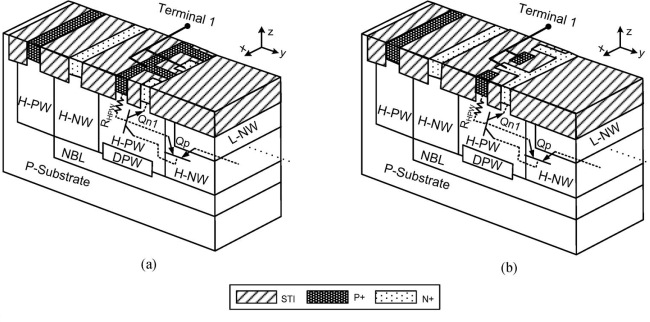

图1 (a) 和 (b) 分别显示双向空穴增强传导性 (BHEC) 与电子增强传导性 (BEEC) 箝位器件的部分透视图。两种结构中还显示、标注了简化原理图。箝位器件的第二个引脚(未显示)通过在“y”正向创建对称镜像来构建,处在H-NW和L-NW形成的浮动式n型区域接口处。高掺杂n+和p+有效区域具有“T”形三维透视图阵列,可以实现空穴驱动或电子驱动小载荷再生反馈的最佳电流增益调整和器件启动时进行高传导性调制。

图1,(a) 保持电压≥ ± 40|V与 (b) 保持电压≥ ± 25|V时双向箝位器件的部分透视图与简化原理图。

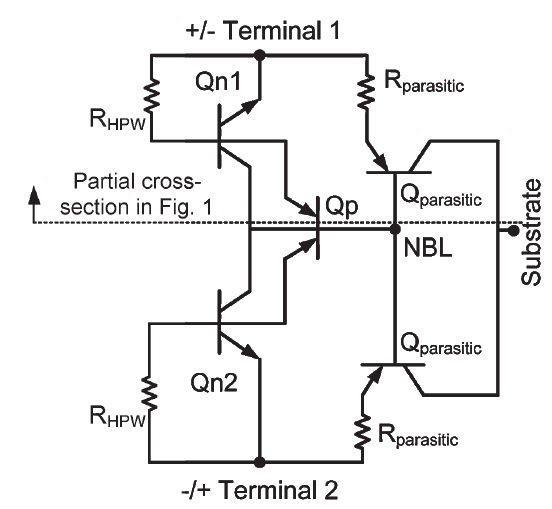

图2,双向闭锁电压箝位器件等效原理图虚线上方部分是图1中部分视图的等效原理图。

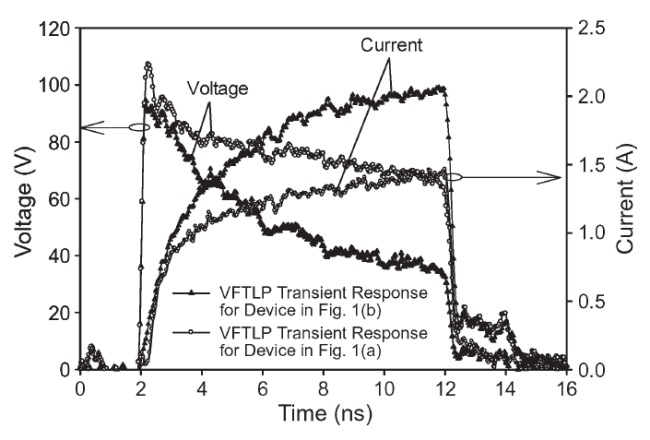

图3, 140 V极快TLP施加到受测器件时,图1(a)和图1(b)结构的电压与电流波形对比。

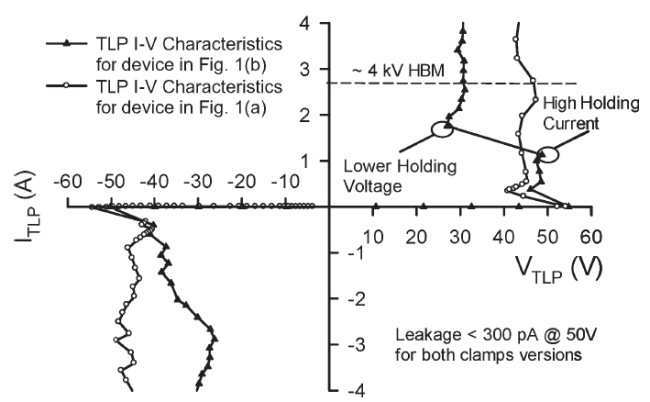

图4,.图1(a)和(b)结构的准静态100 ns TLP双向I–V特性。

-

微信扫一扫

一键转发 -

最前沿的电子设计资讯

最前沿的电子设计资讯

请关注“电子技术设计微信公众号”

- 用“老古董”电荷泵将电压减半,使电流“效率”加倍 本文展示了一个Vout=Vin/2、Iout=Iin*2的示例泵,它是围绕着古老的xx4053系列三重CMOS SPDT开关构建的……

- 做信号链,你需要了解的高速信号知识(二) 做高速的工程师最头疼的问题就是抖动和眼图测量Fail。抖动和眼图测量就像是一个照妖镜,任何一个设计不当,都可能会导致抖动和眼图结果的恶化,而要解决抖动和眼图问题,工程师往往无从下手……

- 电力电子科学笔记:PN结的热行为 在之前的文章中,我们讨论了决定pn结反向饱和电流随温度变化而呈上升趋势的物理机制。在本文中,我们将研究所有极化的热效应。

- 用于电路分析和设计的Spice仿真指南-第11部分:初始条件 SPICE中最有用的指令之一就是允许您为瞬态分析指定节点的初始条件的指令···

- 用于电路分析和设计的Spice仿真指南–第10部分:蒙特卡 蒙特卡罗分析是电子仿真中使用的一种技术,用于使用随机参数进行一系列仿真。

- QSPICE:导入电子元件的外部模型(第7部分) 在本文中,我们将了解如何使用QSPICE导入第三方模型。

- 做信号链,你需要了解的高速信号知识(一) 为什么要使用LVDS或JESD204B标准?

- 宝座易主,Claude 3超越GPT-4成为全球最强模型 Claude 3系列的旗舰模型Opus在本科水平专家知识(MMLU)、研究生水平专家推理(GPQA)、基础数学(GSM8K)等多个测试中均超越了OpenAI的GPT-4和谷歌的Gemini 1.0 Ultra,并在复杂任务上表现出接近人类水平的理解力和流畅性···

- 实现示波器同步以获得更高通道数时需要考虑的三件事 要增加测试系统中的示波器通道数量,常见的方法是将多个组合在一起。多通道测量适用于各种场景,例如捕获复杂的粒子物理实验数据、测量大量电源轨以及分析三相电源转换器。

- Cadence 扩充 Tensilica Vision 产品线,新增毫米波 单个 DSP 用于嵌入式视觉、雷达、激光雷达和 AI 处理,在性能提升的前提下,带来显著的面积优化、功耗和成本的降低;针对 4D 成像雷达工作负载,新增的雷达加速器功能可提供高度可编程的硬件解决方案,显著提升性能;专为多传感器汽车、无人机、机器人和自动驾驶汽车系统设计中的传感器融合处理而设计~

- 电力电子科学笔记:PNP晶体管的输入特性 在本文中,我们将分享用于评估PNP晶体管输入特性的实验室实验结果···

- 电力电子科学笔记:半导体中的Wannier-Mott激子 激子学是固态物理学的一个新分支,主要研究半导体以及更普遍的绝缘体中电子-空穴束缚态(激子)的行为。

- 3月第2周新能源周销量,油车继续低迷 2024年第11周(3月11日-17日),乘用车总销量33.7万辆 ,同比上涨11.4%……

- 2024蓝牙音响市场趋势全解读 在本文中,我爱音频网将对 2023 年的蓝牙音响行业进行市场数据梳理分析,并对全年的技术趋势进行回顾性总结,帮助

- 特斯拉的4680锂离子电池的电特性 特斯拉4680锂离子电池的性能和特性。通过三电极分析、电学和热学特性的表征,上一代的4680并没有达到设计目标

- 智能接口大发展,USB-C十周年回首 USB-C接口自推出以来,带给行业翻天覆地的变化,虽然看似只是简单的接口迭代,牵扯的却是设备连接、充电等重要拓

- 拆解报告:石龙富华35W PoE电源适配器 石龙富华这款PoE电源适配器支持35W输出功率,在机身两侧设有固定孔,可以固定在墙壁或者机架上。适配器采用八字

- YAMAHA雅马哈YH-E700B头戴式降噪耳机拆解 YAMAHA雅马哈YH-E700B头戴式降噪耳机外观上采用了全新设计,能够更好的适应不同头型的舒适佩戴需求。在功能配

- 让电池测试变得简单 早在蜂窝电话诞生之时,各个厂商就开始用电池为手机供电;而随着 21 世纪初期智能手机的问世,蜂窝电话真正迎来

- 拆解报告:罗马仕10000mAh 67W超级快充移动电源 罗马仕这款超级快充移动电源为充电器+充电宝二合一设计,内置的氮化镓充电器支持67W快充输出,移动电源为10000m

- 花了大价钱的激光孔设计性能竟然不如普通通孔? 我们都知道,激光孔的性能不至于那么差,只不过是使用它的方法在这个场景上是真的不对,单纯从PCB设计上来看,你可

- EDIFIER漫步者ComFo Fit开放式耳机拆解 漫步者ComFo Fit开放式耳机支持双MIC ENC通话降噪,能够有效分离与消除环境噪音,提供清晰通话效果;支持游戏模式

- 古老的物理量如何在今天产生新的应用 光的频率和相位作为基本参数,它们支撑着我们对光的波动性的理解。进一步深入研究非线性光学,我们发现了光的行

- NVIDIA发布“封杀令”:CUDA转译将被禁止 英伟达最近发布了一项禁令,不允许在其他GPU上运行CUDA软件。这一举措引发了关于CUDA兼容禁令的讨论,以及对国

- 东芝在其电机控制软件开发套件中新增位置估算控制技术,旨在简化电 现在提供“MCU Motor Studio Ver.3.0”和新的“电机参数调整工具”···

- 意法半导体发布先进的超低功耗STM32微控制器,布局工业、医疗、智 新旗舰产品,超低功耗,物超所值···

- SynQor®发布适用于MIL-STD-1275的军用级直流输出功率调节器(MPC- SynQor ® 是一家领先的电源转换解决方案供应商; 近期宣布为直流输出浅机架军用级电源调节器系列推出一款

- Arteris 扩展面向 Armv9 架构 CPU 的汽车解决方案 Arteris宣布了其与 Arm 持续合作的首批成果,以加速基于最新一代 Arm® 汽车增强型(AE)技术的汽车电子创新

- ENNOVI推出汽车10Gbps+以太网连接器解决方案 采用基于鱼眼端子压接技术的USCAR接口,成为市场上首个定制化以太网连接器解决方案···

- 意法半导体高性能微控制器为智能家居和工业系统新创新扫清障碍 STM32H7R/S微控制器将嵌入式应用性能提高到一个新水平,适合新一代智能工厂、建筑、基础设施和健康监测设备·

- Arm 宣布推出全新汽车技术,可缩短多达两年的人工智能汽车开发周 Arm 控股有限公司今日携手生态系统合作伙伴推出最新的 Arm 汽车增强 (AE) 处理器和虚拟平台,让汽车行业在开

- 康佳特推出aReady.COM新产品家族—aReady. 战略的第一个关键阶 嵌入式和边缘计算技术的领先供应商德国康佳特,推出全新aReady.COM产品家族,这是其创新的aReady. 战略的第一个

- Vishay的新款80 V对称双通道 MOSFET的RDS(ON) 达到业内先进水 节省空间型器件所需PCB空间比PowerPAIR 1212封装分立器件减少50 %,有助于减少元器件数量并简化设计

- 思特威推出1600万像素手机图像传感器新品SC1620CS 思特威推出1600万像素手机图像传感器新品SC1620CS

- 嘉楠基于RISC-V的端侧AIoT SoC采用了芯原的ISP IP和GPU IP 将芯原像素处理IP组合集成到高精度、低延迟的K230芯片中

- Vishay推出升级版TFBS4xx和TFDU4xx系列红外收发器模块,延长链路距 器件符合IrDA®标准,采用内部开发的新型IC和表面发射器芯片技术,可以即插即用的方式替换现有解决方案···