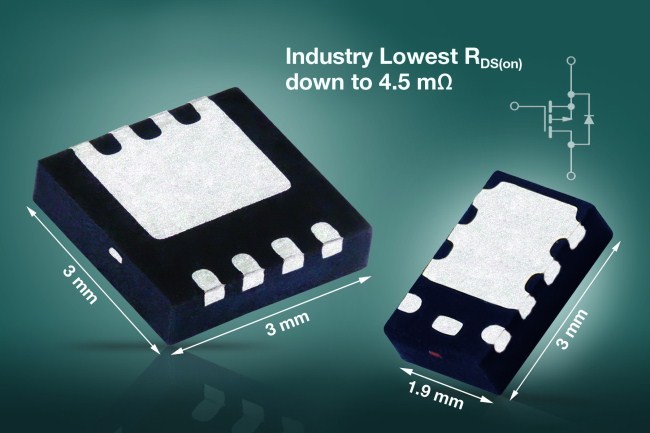

Vishay P沟道Gen III MOSFET具有业内最低导通电阻,-12V和-20V器件采用PowerPAK ChipFET和PowerPAK 1212-8S封装,3.0mm x 1.9mm x 3.3mm的占位体积。

日前,Vishay Intertechnology, Inc.宣布,推出采用PowerPAK ChipFET和PowerPAK 1212-8S封装的新器件,扩充其TrenchFET P沟道Gen III功率MOSFET。今天推出的Vishay Siliconix MOSFET可提高便携式计算和工业控制设备中的电源效率,是-4.5V和-2.5V栅极驱动下具有业内最低导通电阻的-12V和-20V器件,占位面积为3.0mm x 1.9mm x 3.3mm。

Si5411EDU、Si5415AEDU和SiSS23DN适用于智能手机、平板电脑、笔记本电脑、工业传感器和POL模块里的电源管理等各种应用中的负载、电池和监控开关。器件的低导通电阻使设计者能够在其电路里实现更低的电压降,更高效地使用电能,延长电池使用寿命。

Vishay P沟道Gen III MOSFET

Vishay P沟道Gen III MOSFET具有业内最低导通电阻

上一篇:

ST发布最新的ST33安全微控制器

-

微信扫一扫

一键转发 -

最前沿的电子设计资讯

最前沿的电子设计资讯

请关注“电子技术设计微信公众号”

- 锂离子电池之后,下一代的电池技术可能是什么? 随着锂的开采和产量不断增长,锂已成为自人们认知到气候问题以来最值得关注却又矛盾重重的全球市场之一,那么哪些替代选择是最为可行的呢?

- 嵌入式产品的持续交付到底有没有意义? 持续部署嵌入式软件一开始听起来不错,但您真的想持续向客户部署新软件吗?如果您正在制造汽车ECU、医疗设备,甚至微波炉或家用电器,您的客户真的需要频繁更新吗?

- Transphorm发布两款4引脚TO-247封装器件,针对高功率服 新推出的氮化镓场效应晶体管可作为原始设计选项或碳化硅(SiC)替代器件

- 美光率先上市基于LPDDR5X的 LPCAMM2内存模块,变革PC用 LPCAMM2 内存模块以更高性能、更低功耗、更小的外形规格助力笔记本电脑实现更快速度、更小巧尺寸和更强续航,并通过模块化设计为升级和维修提供便利

- Vishay为其高性能红外接收器模块推出升级版 器件可提供即插即用方式替换现有解决方案,降低更宽电源电压范围内的供电电流,提高抗ESD可靠性、黑暗环境灵敏度和DC强光直射性能

- 大联大诠鼎集团推出基于Innoscience产品的1KW DC/DC 大联大控股宣布,其旗下诠鼎推出基于英诺赛科(Innoscience)InnoGaN ISG3201和INN040LA015A器件的1KW DC/DC电源模块方案。

- 与英特尔、英伟达和AMD三位CTO的独家对话 笔者采访了英特尔、英伟达和AMD三家公司的CTO,请他们就行业的演变和发展方向发表了见解。

- 利用土壤发电的燃料电池?MFC为物联设备提供新能量源 美国西北大学的研究团队开发了一种新型燃料电池,可以从生活在污垢中的微生物中获取能量,该燃料电池不仅可以在潮湿和干燥条件下工作,而且其功率也比同类技术高出120%,可以为精准农业和绿色基础设施中使用的地下传感器提供能量···

- 混动车宣传续航1200公里实际打五折,CLTC标准惹的祸? 据国内媒体报道称,消费者孙女士家里刚买了一辆插电式混合动力商务车,品牌方宣传续航有1200公里,在行驶了三千多公里后,一次从宁波到杭州的高速行程却显示,续航只能跑600公里。众所周知,新能源汽车主流的续航标准有三个,分别是CLTC标准、NEDC标准、WLTC标准以及EPA标准。从严格程度上来说……

- 清华开发“熔化-重凝”新方法,成功获得高均匀二维TMDC 清华大学的研究团队开发了一种采用“熔化-重凝”的硫单质前驱体的化学气相沉积方法,通过提高硫族元素供应的稳定性,实现了高质量和高均匀性的TMDC生长···

- 大联大友尚集团推出基于onsemi产品的3KW高密度电源方 大联大控股宣布,其旗下友尚推出基于安森美(onsemi)NCP1681和NCP4390芯片以及SiC MOSFET的3KW高密度电源方案。

- 全球首款民用原子能电池即将面市,无需充电续航五十年 最近,据贝塔伏特官网消息,北京贝塔伏特新能科技有限公司成功研制出首款可供民用的微型原子能电池BV100,该产品融合镍-63核同位素衰变技术和中国第一个金刚石半导体(第4代半导体)模块,成功实现了原子能电池的微型化、模块化和低成本···

- 2024年1月第3周新能源周销量 本周我们还是关注我们芝能热点品牌的情况,我们罗列了品牌和重点车型的情况···

- 与健康息息相关的分子马达(二) 细胞是一个包含多种分子马达的复杂系统,分子马达功能各异,协作完成细胞活动。但分子马达的功能异常或表达异常

- 拆解报告:酷态科10000mAh 30W快充移动电源 酷态科这款移动电源内置两节21700电池,总容量为10000mAH,体积小巧便携。移动电源两侧分别设有USB-C和USB-A接

- 华为FreeClip开放式耳机全球首拆 HUAWEI华为FreeClip开放式耳机在外观方面,采用极简主义几何设计,兼具了全天候舒适佩戴和时尚佩饰属性。在功能

- 神通552125软包电芯评测 这款神通552125软包电芯,我爱音频网分别在0.2C、0.5C以及1C三种倍率下进行测试,充电方面,1C倍率充电能在1小时2

- 华为FreeClip开放式耳机首发评测 作为华为旗下首款开放式耳机,FreeClip 采用了少见的「夹耳式」结构,整体呈 C 型,通过夹耳廓的形式固定在耳朵上

- 生物生命活动驱动者,与人类健康息息相关的分子马达(一) 分子马达由生物大分子构成,能够将化学能转化为机械能。分子马达作为具有特定结构的蛋白质,能够通过自身的运动

- 人形机器人之关键触觉传感器:刚性到柔性 触觉传感器是机器人进化的核心需要解决的问题,芝能科技将带你逐步了解触觉传感器的技术原理、技术路线、发展

- 拆解报告:美富达65W 2C1A氮化镓快充充电器 美富达这款65W充电器具备2C1A输出接口,并配有美标折叠插脚。充电器机身上没有标注任何产品信息。实测充电器

- 详细解读ACLR和ACPR 今天射频学堂将和大家一起抽丝剥茧一个射频指标——ACLR。

- 消失的她,GERBER失踪之谜 Gerber格式是线路板行业软件描述线路板(线路层、阻焊层、字符层等)图像及钻、铣数据的文档格式集合。明明有图

- OpenAI进军芯片行业 OpenAI,这个人工智能行业的当红小生,正积极探索半导体市场的机会。OpenAI首席执行官Sam Altman已开始与中东知

- Wi-Fi Alliance选用RUCKUS Wi-Fi 7平台作为Wi-Fi CERTIFIED 7互 RUCKUS Wi-Fi 7接入点为Wi-Fi CERTIFIED 7设备制定标准并支持全球互操作性

- 安霸发布前端AI开发者平台:Cooper Cooper开发者平台为工业应用、AIoT、智能视频分析和前端AI计算应用提供高能效解决方案。

- Microchip推出10款多通道远程温度传感器 MCP998x系列是单一供应商提供的最大车规级远程温度传感器产品组合之一

- 罗克韦尔自动化发布《可持续发展2023年度报告》 阐述在可持续发展方面的进展和成果

- Melexis首创Triphibian技术可实现MEMS压力敏感元件革新 Melexis今日宣布,推出首款采用全新专利Triphibian™技术的压力传感器芯片MLX90830。

- 上海首家第三方整车OTA测试实验室携手MVG 填补智能网联汽车测 MVG近日宣布,中国信通院上海工创中心(以下简称“上海工创中心”) 与浙江埃科汽车技术服务有限公司(以下简称“

- Transphorm发布两款4引脚TO-247封装器件,针对高功率服务器、可再 新推出的氮化镓场效应晶体管可作为原始设计选项或碳化硅(SiC)替代器件

- 全国产六核CPU商显板,米尔-芯驰D9360高性能高安全显控方案 今天给大家介绍一款国产厂商(芯驰科技)推出的六核高性能、高安全性芯片:D9-Pro,这款芯片有超强视频编解码能力,米

- 意法半导体与Sphere Studios联合打造全球最大的电影摄影机图像传 该影像传感器专为世界上最先进的摄影系统 Big Sky而定制,能够为拉斯维加斯的 Sphere球幕拍摄超高分辨率影像

- 美光率先上市基于LPDDR5X的 LPCAMM2内存模块,变革PC用户体验 LPCAMM2 内存模块以更高性能、更低功耗、更小的外形规格助力笔记本电脑实现更快速度、更小巧尺寸和更强续航

- 瑞萨推出其首款集成闪存的双核低功耗蓝牙SoC并实现最低功耗 全新DA14592 SoC和DA14592MOD模块支持众包定位等广泛应用,同时带来最低eBoM

- Vishay为其高性能红外接收器模块推出升级版 器件可提供即插即用方式替换现有解决方案,降低更宽电源电压范围内的供电电流,提高抗ESD可靠性、黑暗环境灵敏