锁相环(PLL)是现代电子系统中不可或缺的组件,其功能是产生与输入信号频率相等或数倍于输入信号频率的精确频率输出信号。它主要用于调制器/解调器以及时钟生成/时钟倍频。但是,在混合信号芯片上设计数字通信系统时,数字设计人员因PLL与生俱来的模拟特性,都倾向于避免使用PLL,而模拟设计人员又嫌IDE涉及编码,对其敬而远之。本文将介绍一种设计简单PLL的不同方法。

PLL的基础知识

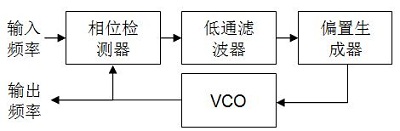

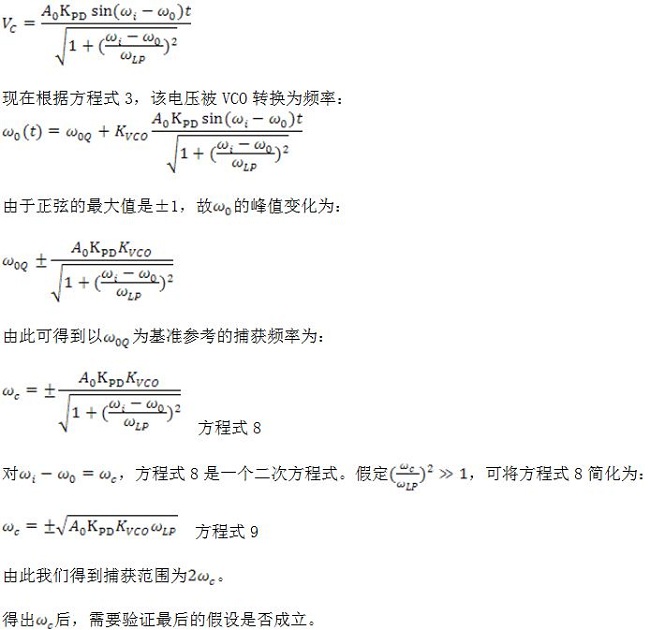

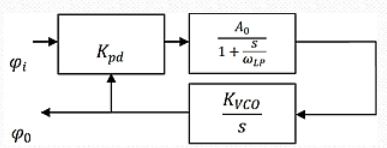

我们先从PLL的原理方框图着手:

图1:PLL的原理方框图

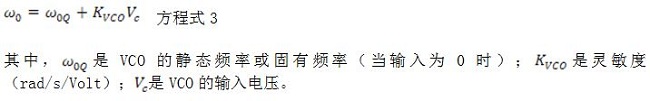

bc5ednc

bc5ednc

bc5ednc

为正常工作,用偏置发生器为该电压添加与频率无关的恒定偏置,然后将该电压输入到VCO。顾名思义,VCO所产生输出电压的频率与输入电压成比例。

bc5ednc

bc5ednc

从较高的层面来看PLL,如果PLL的输入频率与VCO频率不同,相位检测器就会产生电压。经过滤和偏置后,该电压会调整VCO的频率,使之与输入相匹配。

《电子设计技术》网站版权所有,谢绝转载

{pagination}

PLL的参数

PLL的主要参数包括:

1.

类型和阶数:由系统的传递函数决定。

2.

锁定范围:一旦锁定,PLL即能跟随输入频率变化的范围。主要由VCO范围进行定义,并受相位检测器限制。

3.

捕获范围:PLL从非锁定条件开始所能锁入的频率范围。该范围通常小于锁定范围,并取决于低通滤波器的截止频率。

4.

环路带宽:定义控制环路的速度。

5.

瞬态响应:峰值过冲与建立时间。

6.

稳态误差:相位或时序误差

7.

输出频谱纯度:主频相对于边频的强度。

8.

相位噪声:指在特定频带内定义的噪声能量。取决于VCO相位噪声,PLL带宽。

9.

一般性参数:如功耗、供电电压范围、输出幅度。

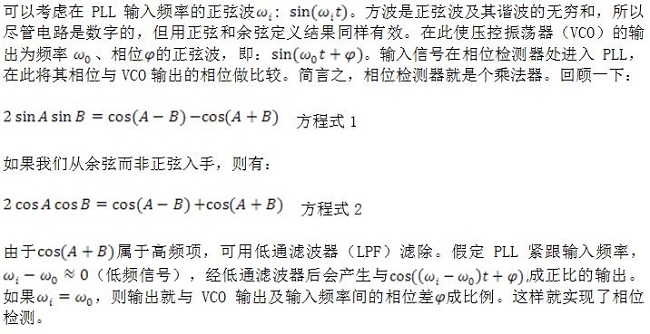

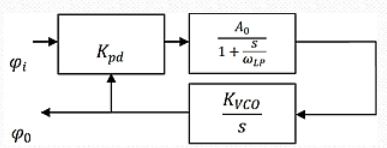

S域表达

为了更好地理解PLL,应深入到低层次细节元素中。可以先考虑一下下列原理方框图中PLL的S域表达。为简单起见,在此省去了偏置发生器。

图2:PLL的S域表达

bc5ednc

假定相位检测器是线性的(对接近静态频率的频率成立),信号流程如下:

bc5ednc

bc5ednc

PLL对各种输入的响应

接下来考察PLL如何针对各种信号做出响应(参见图2)。

bc5ednc

bc5ednc

《电子设计技术》网站版权所有,谢绝转载

{pagination}

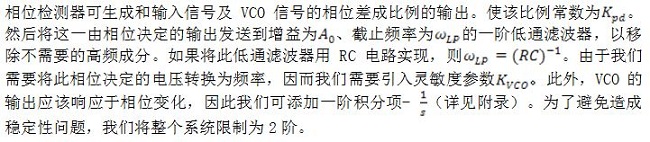

锁定范围的推导

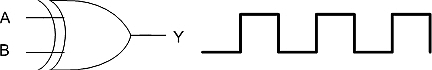

第一个问题取决于相位检测器。假定您使用异或门(XOR)作为相位检测器(参见图3),并假定逻辑电平1为+1V,逻辑电平0为-1V。我们从固有频率开始。VCO和输入信号有90度相移。在图中,当A和B存在90度相移时,输出信号为平均值为0、占空比为50%的方波。

但是,随着相位差超过90度,向180度增加,平均输出值开始以线性增长(如果A!=B,即相移180度,则XOR=1)。类似的,如果缩小A和B之间的相位差,使之接近0度,那么输出值Y就开始降低(如果A==B,则XOR=0)。但在越过0度以后,Y的平均值开始增大(根据异或门运算)。虽然在理想的情况下,由于相位差仍在下降,我们期望平均输出同时下降。与此相似,在超过180度后,虽然Y的平均值本来应该增大,但却开始下降。

图3:将异或门作为相位检测器

bc5ednc

因此,异或门的平均值是该开放式区间(0,180)内相位差的良好指示器。一旦VCO锁定到该输入频率,只有在这个频率范围内PLL才可以工作。这就是通常确定锁定范围的因素(前提是VCO能够命中(0,180)区间内出现的所有频率)。

bc5ednc

bc5ednc

高级设计视图

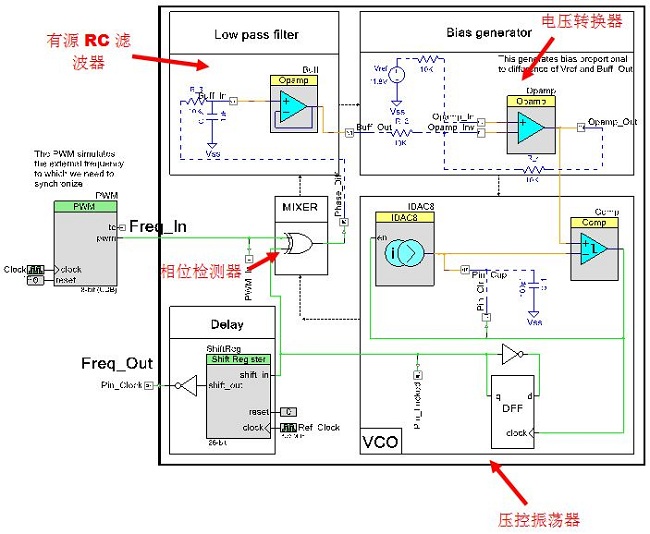

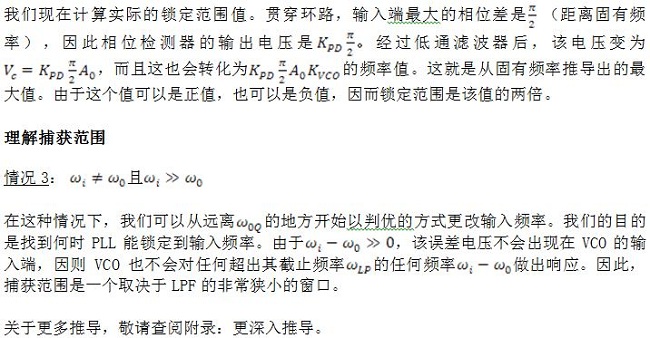

运用该理论,我们现在就能进入设计PLL的流程。下面是一个PLL的实施方案,包含我们在图1中看到的所有模块。具体的构建模块将在下文中逐一解读。

图4:PSoC Creator PLL原理方框图

bc5ednc

《电子设计技术》网站版权所有,谢绝转载

{pagination}

PLL设计的实施

如图4所示,虽然是最简单的原理图形态,但PLL却全面包含了图1中的全部基本模块。任何锁相环的核心均是压控振荡器(VCO)。所以我们从设计VCO开始:

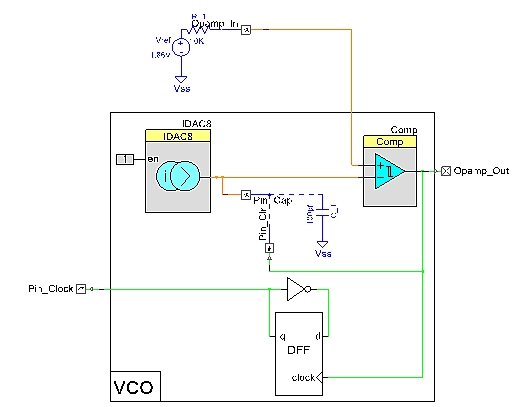

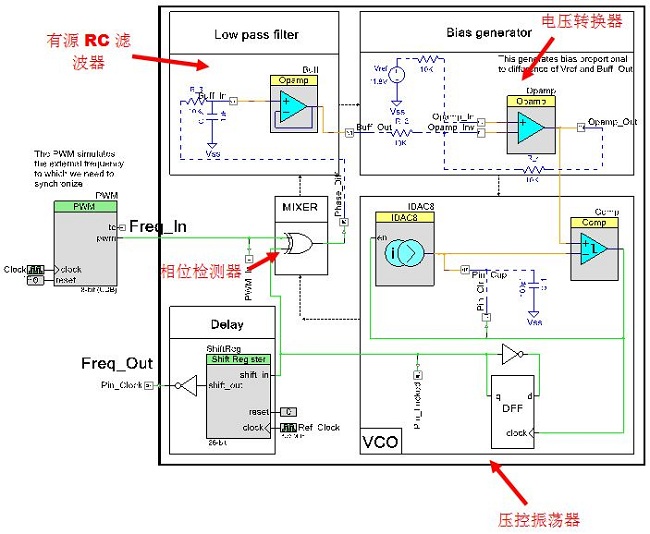

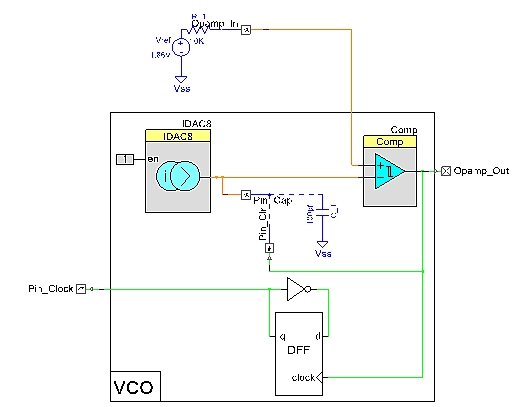

VCO

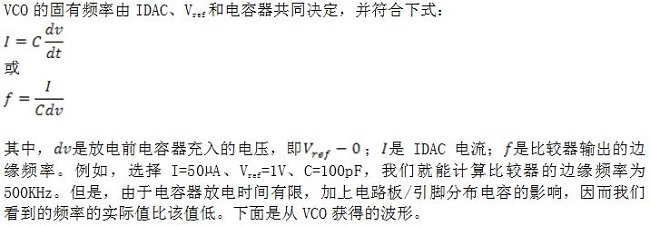

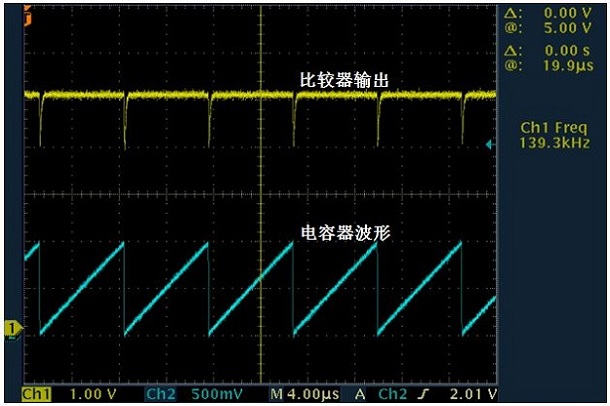

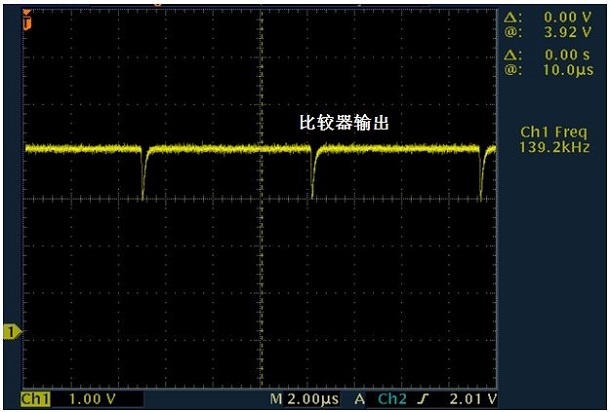

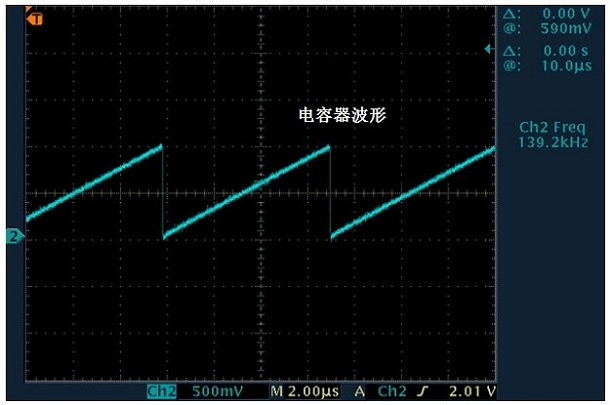

VCO的工作方式简单明了。电流输出数模转换器(IDAC)可为电容器充电,电容器电压呈线性增长。当该电压增大至大于正输入(到比较器)时,迟滞比较器的输出电平降低。这样就会通过Pin_Clr短路电容到地。电容器放电时,比较器的输出再度回升,因此会发送上升沿到DFF(D触发器),并需要重新启用IDAC。DFF随即产生频率为比较器沿的一半、占空比为50%的输出时钟信号。

图5:压控振荡器原理方框图

bc5ednc

bc5ednc

bc5ednc

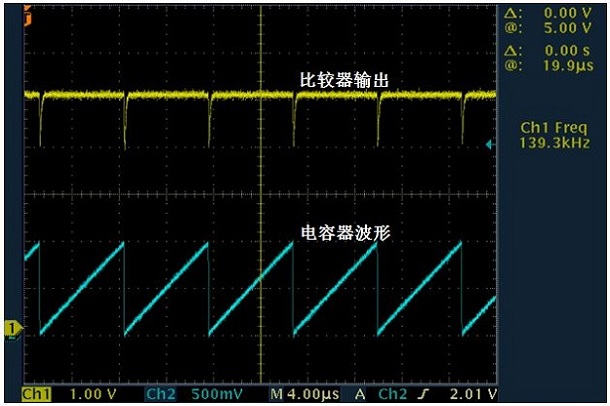

图6:VCO比较器和电容器波形

bc5ednc

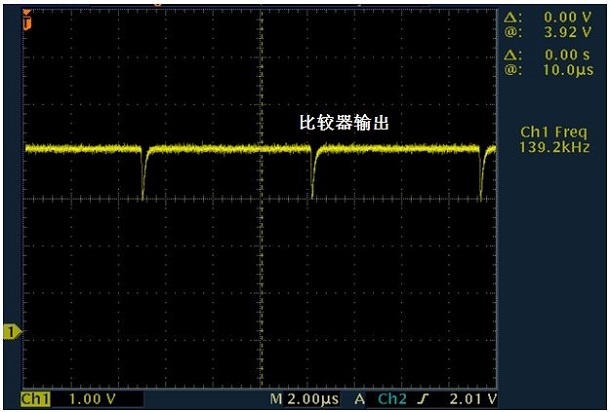

图7:比较器输出

bc5ednc

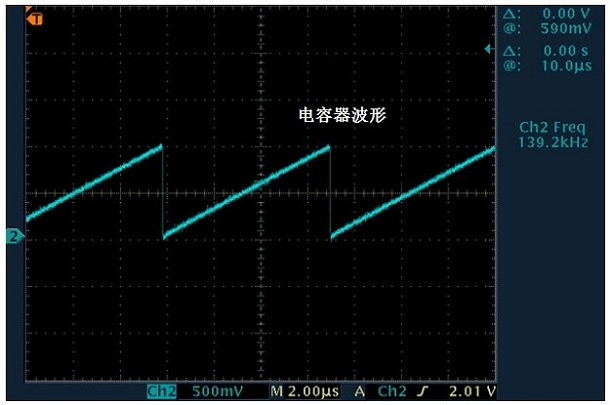

图8:电容器充电和放电

bc5ednc

bc5ednc

bc5ednc

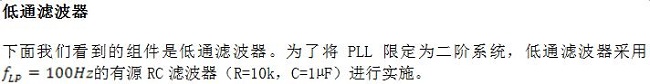

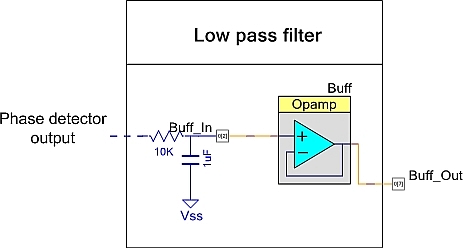

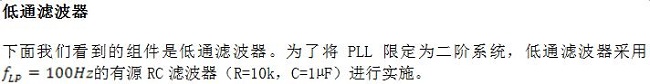

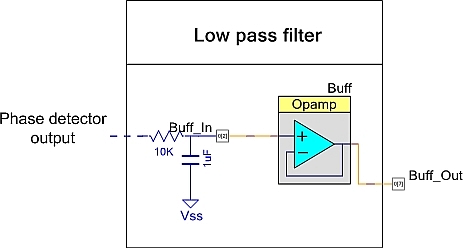

图9:低通滤波器

bc5ednc

《电子设计技术》网站版权所有,谢绝转载

{pagination}

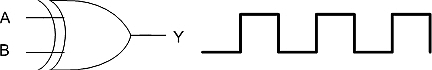

相位检测器和偏置生成器

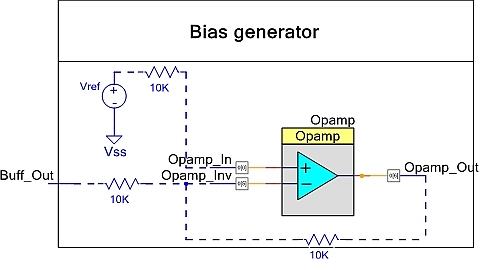

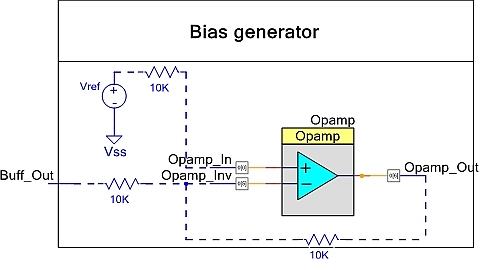

如前文所述,异或门被用作相位检测器。偏置生成器可设定VCO的固有频率,进而是捕获的信号。其采用差分放大器来实现。

图10.偏置生成器

bc5ednc

bc5ednc

bc5ednc

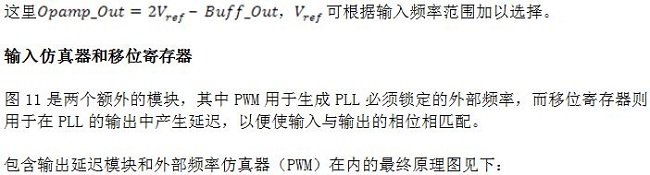

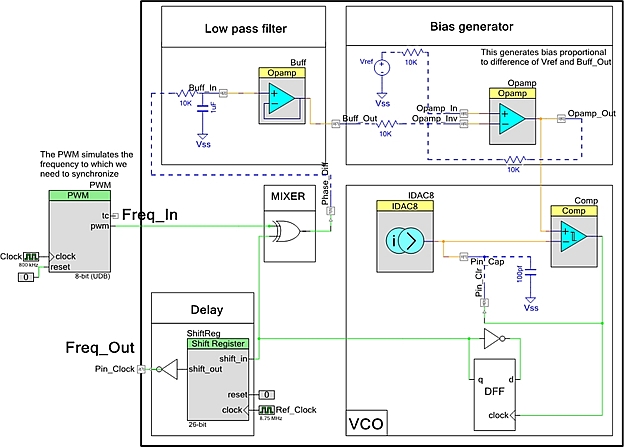

图11:PLL以及延迟和外部仿真器(PWM)

bc5ednc

可将本设计所需的全部模块从参考库中拖入,然后连线。设计人员可根据这个流程的特性进行大致设计、测试,然后再轻松修改原始设计。另外,在本设计中无需编码。因而设计周期得到显著简化。

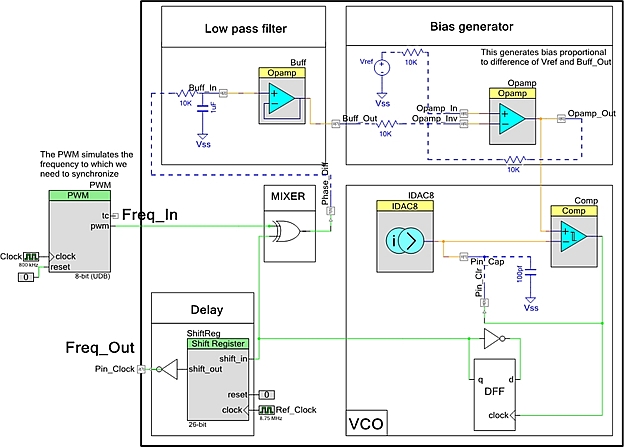

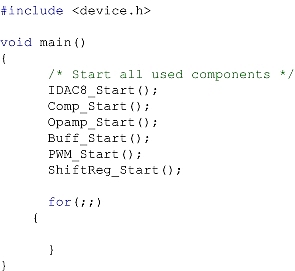

图12:PLL所需的C语言编码

bc5ednc

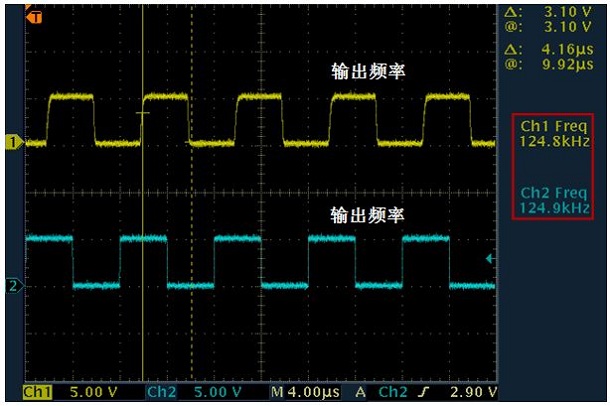

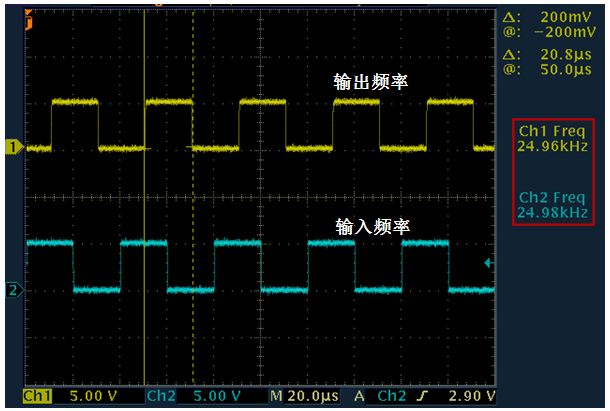

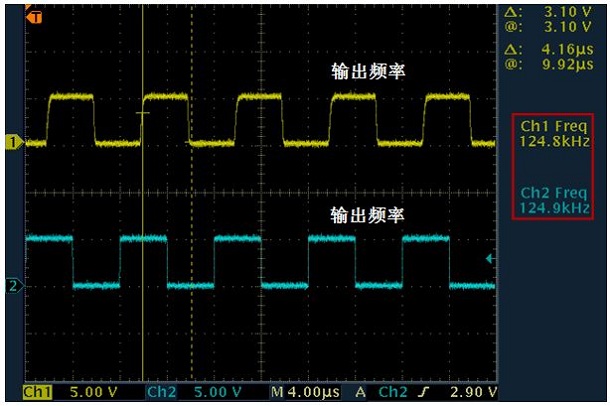

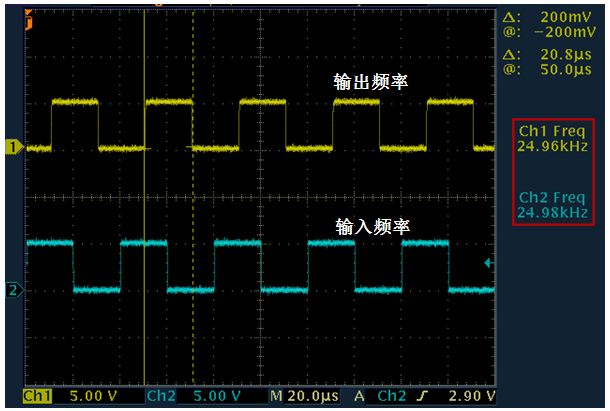

下列的两个示波器截图显示的是125KHz和25KHz两种频率的PLL输出,均在固有频率条件下(90度相移清晰可见)。

图13:PLL输入和输出频率均为125KHz时的示波器屏幕截图

bc5ednc

图14:PLL输入和输出频率均为25KHz时的示波器屏幕截图

bc5ednc

由此我们已看到如何揭开较大型混合信号应用看似令人生畏的模块化子系统设计流程的神秘面纱。请注意,本文设计的PLL还有许多需要优化的地方。

《电子设计技术》网站版权所有,谢绝转载

{pagination}

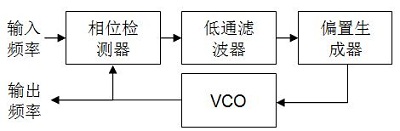

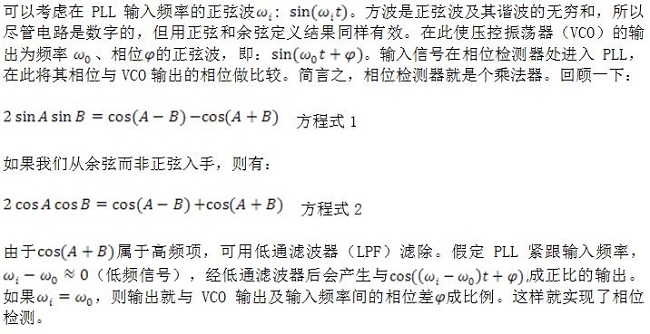

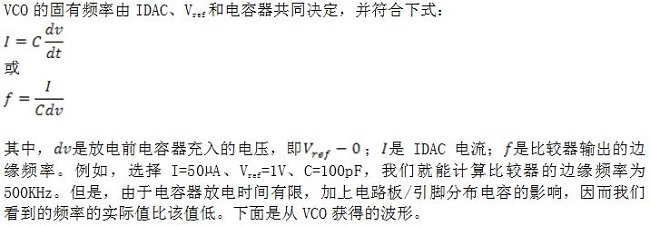

附录:更深入推导

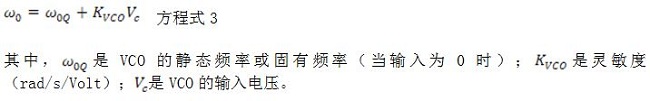

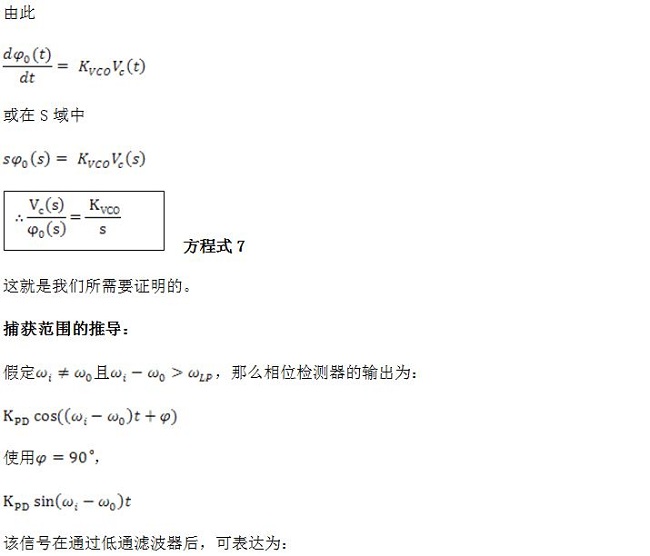

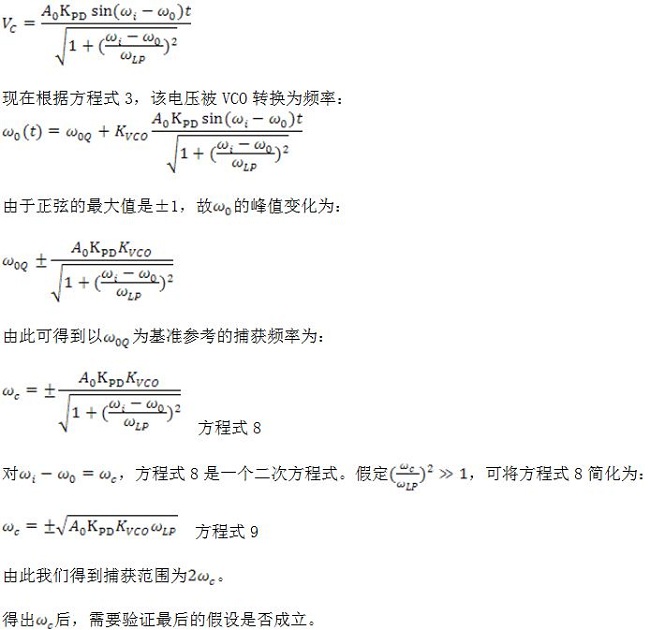

VCO方程式和传递函数:

为掌握S域传递函数间的关系

bc5ednc

bc5ednc

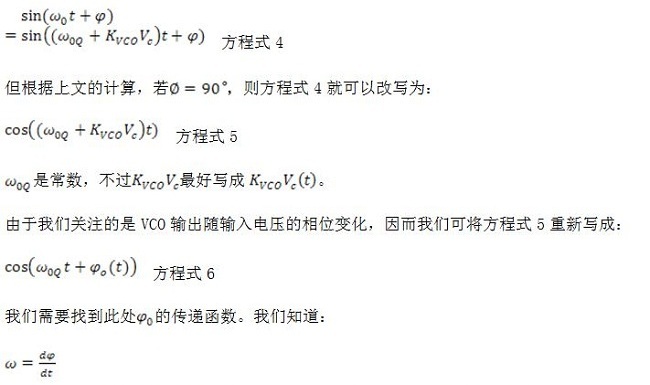

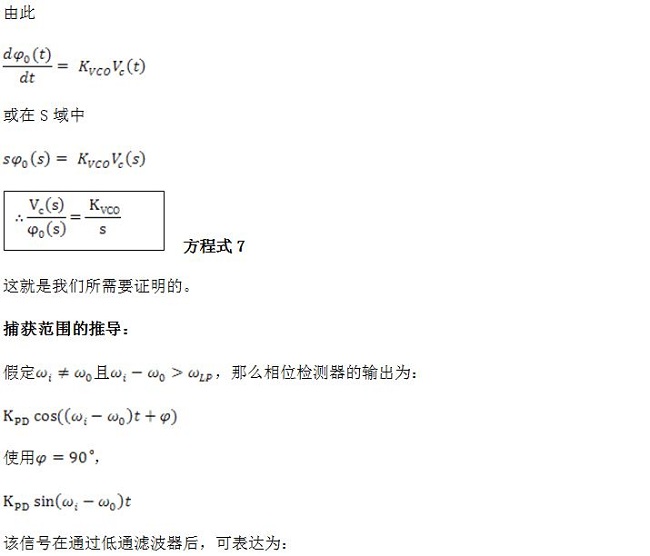

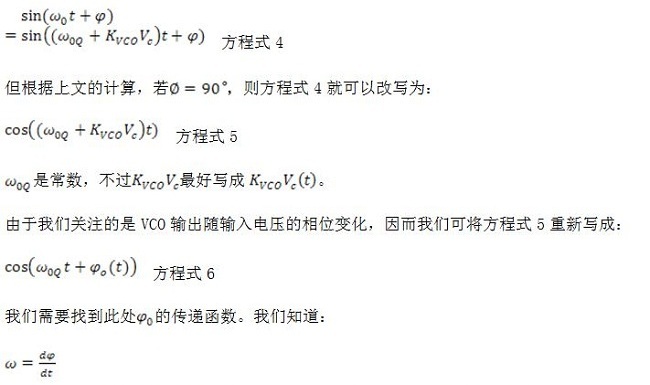

再从方程式3中看K

VCO项,让我们回顾一下模拟的正弦余弦计算公式。VCO的基本作用是在其输出端生成与输入电压成比例的频率信号。这就就方程式3的涵义。由此方程式3中VCO的输出可以写为:

bc5ednc

bc5ednc

bc5ednc

bc5ednc

bc5ednc

bc5ednc

《电子设计技术》网站版权所有,谢绝转载

最前沿的电子设计资讯

最前沿的电子设计资讯