移动计算设备(智能手机、平板电脑等)的使用出现了巨大的转变。除了典型的手机用途外,这些设备现在还被用来玩游戏、看电影或体育赛事。这一转变带来了功耗分析流程中所采用方法的转变。推动这一转变的一个主要因素是,现在复杂的SoC设计需要使用动态应用程序进行验证,这些动态应用程序要求在硬件仿真器上启动操作系统并运行软件应用程序。更有效的方法是,使用在硬件仿真过程中生成的功耗切换动态图将即时切换实时数据传输到功耗分析工具,以评估潜在的功耗问题。

对于具有高分辨率屏幕、要求持久电池续能力的手持和智能设备,甚至是数据中心等设备而言,功耗一直是一个首要关注的问题。使用FinFET工艺技术可减少静态漏电流,但是动态功耗仍是一个挑战。Mentor Graphics在近日发布了Veloce功耗应用程序软件,该软件提供了一种先进的方法可以在系统、RTL和逻辑门级实现精确、及时且高效的功耗分析,支持实现复杂的SoC设计。

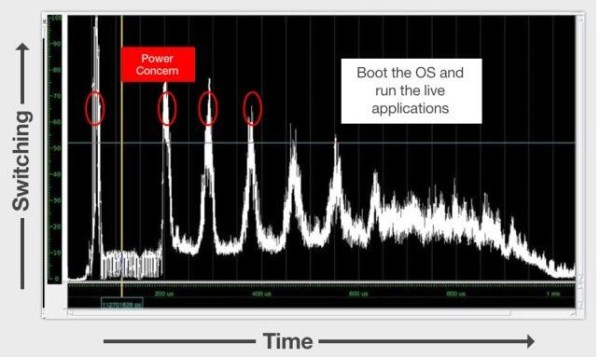

Mentor Graphics产品市场经理Gabriele Pulini指出,传统的功耗分析方法是根据应用场景(功能)编写一个自适应功能测试平台,然后在软件仿真器上运行这个功能测试平台,进行功耗分析。这种方法不能覆盖到设备所有的使用场景,对功耗计算会产生很多偏差,尤其是不能捕获操作系统启动与应用程序实际运行时的真实数据。测试平台可能会将一开始的功耗状况作为功耗峰值来分析,而事实上应用程序运行中,真正的功耗峰值远没那么早到来。

另外,当含有重要软件内容的设计在硬件仿真器上运行时,目前产生电路动态数据的方法会造成文档(如FSDB)过大,生成时间进而读取时间都太长,功耗分析工具几乎无法处理。而FSDB正是描述应用程序活动的功耗平均值和峰值表现,需要一个更快、集成度更高的解决方案。

Gary Smith EDA创始人兼首席分析师Gary Smith表示:“采用新的方法来传输在硬件仿真过程中获取的功耗切换动态数据,这是行业发展的正确方向。”

图1:正确的方法是在长时间的运行状态(启动OS和实时运行应用程序)中识别重点区域的功耗状况。

EXVednc

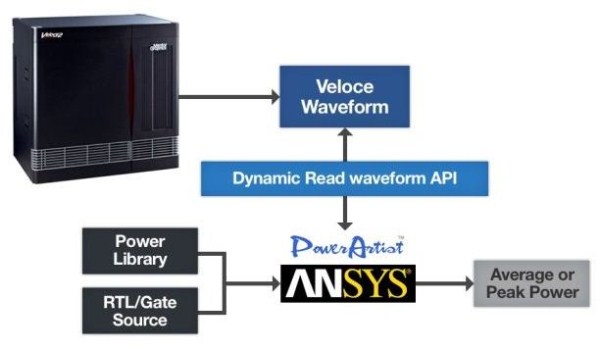

Mentor 的Veloce功耗应用程序通过将一个Dynamic Read Waveform API集成到功耗分析工具中,取代基于文档的功耗分析流程。这一使用Dynamic Read Waveform API的方法可获取来自功耗切换动态统计的信息,并将数据传输到功耗分析工具。这可实现在系统级进行精确的功耗计算,在RTL级进行更好的功耗探测以进行功耗预算和权衡,以及在逻辑门级实现更精确的功耗分析和签收。通过硬件加速仿真平台Veloce功耗应用程序,可以将真正的应用程序运行在硬件加速仿真器上,在设计完成之前(RTL或网表阶段)就可以检测设计是否有问题,可以更精确、全面、快速地进行功耗设计与分析。

【分页导航】EXVednc

第2页:Veloce功耗分析的两种方法EXVednc

《电子技术设计》网站版权所有,谢绝转载

{pagination}

Veloce功耗分析的两种方法

Gabriele Pulini表示,Veloce有两种分析功耗的方法,基于SAIF的平均功耗分析和基于FSDB的平均功耗和峰值功耗分析。“FSDB格式数据量很大,Mentor的新方法通过Dynamic Read Waveform API,工程师可以将Veloce功耗应用程序产生的波形数据及时送到功耗分析工具(第三方)进行分析,就像水流过水管一样,”他表示,“采用这种流数据的分析方式,使得采用FSDB格式进行多种应用场景的分析成为可能,也大大减少了仿真分析用时。”

图1 系统的总体框图

EXVednc

此前的典型方法中,需运行硬件仿真器、创建波形档案、将档案读入功耗分析工具,再运行功耗分析工具。“相比纯软件仿真器,硬件加速仿真器在速度和容量方面有天然的优势,Veloce容量最大可达20亿门,比软件仿真器快1000倍以上。而相比FPGA验证,硬件加速仿真器在设计能见度和信号能见度上又远远胜出,通过Veloce硬件加速仿真器,可以追踪每一个信号的走向,每一个逻辑门的工作状态,提高了芯片内部的可见度,工程师可以针对实际应用对设计进行功耗优化。”

Gabriele Pulini解释说,“新方法的导入相对原先的流程可大幅提升执行时间和性能,有些抢先试用的合作伙伴和客户已经见证了4.5倍运行时性能改善,证明Veloce功耗应用程序能捕获硬件仿真过程中的实时功耗信息,并有效地将其传输到功耗分析工具的新方法更加高效。而且该方法已经通过UPF联盟和IEEE标准组织的低功耗设计认证。”

提供与行业认可的功耗分析工具生态系统的整合,对于重新定义功耗分析流程非常重要。Gabriele Pulini表示首位Veloce功耗应用程序系统合作伙伴是ANSYS with PowerArtist,整合了ANSYS PowerArtist的Veloce功耗应用程序已经限量向两个公司共同的客户供应,完整的正式版计划将于今年第四季度初发布。

Mentor Graphics亚太区技术总监Russell Lee认为,硬件加速仿真平台更重要的是软件的配合,而现在竞争对手仍然是硬件思维上,强调硬件性能。但是例如仿真时,所有的外设都需要降速后再仿真,而Veloce已经将所有的外设与接口虚拟化,无需降速,这样弹性更大,应用场景更广,而且客户的重复投入成本更低。同时,由于将外设和接口虚拟化,Veloce可以进行云端仿真,该平台的最高配置最高可以支持128个客户端同时进行仿真。“真正在设计上做到云端化的,只有我们!” Russell Lee强调。

《电子技术设计》网站版权所有,谢绝转载

如您对EDA分析工具感兴趣,欢迎参加

2015年IIC-China秋季展(8月31日~9月3日,深圳会展中心3号馆)。提前注册抢座,请点击或扫描下面的二维码:

EXVednc

EXVednc

最前沿的电子设计资讯

最前沿的电子设计资讯