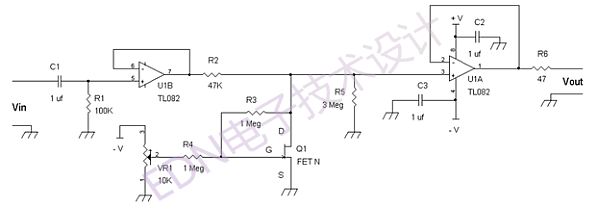

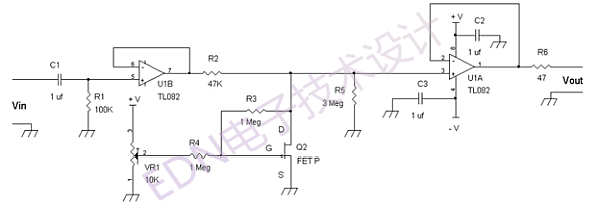

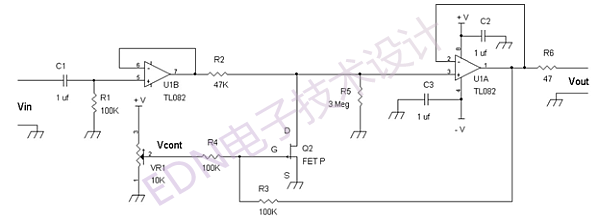

在《如何在电压控制电路中使用FET(第一部分)》中,我们已经分析了FET压控电阻、基本压控电阻电路,以及平衡或推挽式压控电阻(VCR)电路。接下来,让我们看看带反馈的N沟道JFET衰减器电路(见图8)。

图8:反馈电阻R3和R4可减少失真。

我们回到第一部分的图2,对于没有反馈电阻的压控电阻,可以看到通过S1和S2斜率,VDS>0V的电阻比VDS<0V时的电阻要高。

如果图8中的VDS>0V或为正电压,则VDS的一部分(Q1的漏极和源极两端的电压)正电压通过R3被加到栅极电压上。再加上VR1的滑动电压,就使得栅极的负电压减小,这意味着漏极至源极电阻下降。

当VDS<0V时,额外的负电压通过R3施加到栅极,这使得栅极负电压更大,导致Q1的漏极和源极上的电阻更高。

因此,使用反馈电阻网络R3和R4,VDS>0V和VDS<0V的电阻值变得更接近,这将减少失真。

请注意,当R3 = R4时,R3和R4将VDS电压的一半馈送给栅极。我们来看看为什么这有助于消除失真。

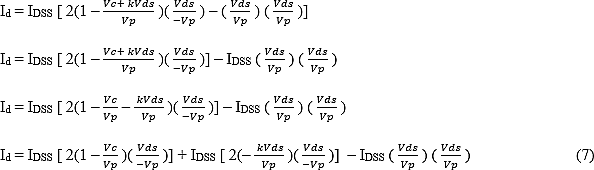

我们来看一下漏极电流公程(1):

![]()

我们希望能够消除(Vds/VP)(Vds/VP)相关项,这样当我们求Id相对于Vds的导数时,电导(gds)只跟Vgs有关。对于线性电导,我们仍然需要漏极电流方程中的Vds项,它将乘以一个常数或与控制电压相关的因子。

令Vgs = Vc + kVds,其中Vc是控制电压,k是反馈因子,0<k<1。

这将得出:

设置最后两项来相互抵消,即:

或者:

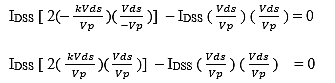

![]()

如果等式两边都除以IDSS,然后两边再乘以(Vp)(Vp),可得到:

![]()

两边都除以(Vds)(Vds),可以得到k:

2k = 1

k = 1/2

对于反馈电阻R3和R4:

k = 1/2 = R4/(R3 + R4)

这意味着在反馈因子k = 1/2时,R3 = R4。

对于Vgs = Vc + kVds:

k = 1/2

k = 0.5

Vgs = Vc + 0.5Vds

现在我们再回到公式(7):

![]()

若k = 1/2,公式(7)的最后两项就抵消了。

对于给定的Vp和IDSS,公式(11)表明,漏极到源极的电阻Rds仅取决于控制电压VC,而跟Vds无关。因此,使用反馈电阻R3和R4可以比较近似地提供一个线性压控电阻器。

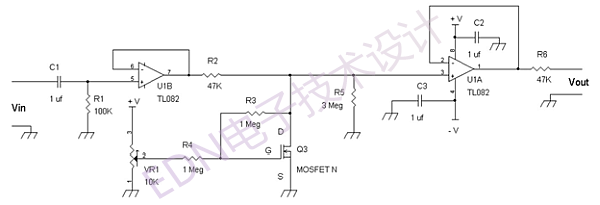

图9示出了一个利用反馈电阻降低失真的P沟道JFET。

图9:P沟道压控电阻电路示例,利用反馈电阻网络R3和R4来降低失真。

请注意在图8和图9中,反馈电阻网络使用高电阻值以便让FET(例如,图8和图9中的Q1和Q2)漏源电阻跟R2一起形成一个分压器。

例如,如果R3和R4 = 22kΩ,那么将会有一个大约44kΩ的电阻与R5以及FET的漏极-源极电阻并联。这个电阻将“清除”一些FET的Rds影响。当R2 = 47kΩ、FET处于截止(例如无限电阻)状态时,输入信号Vin不会无衰减地通过。

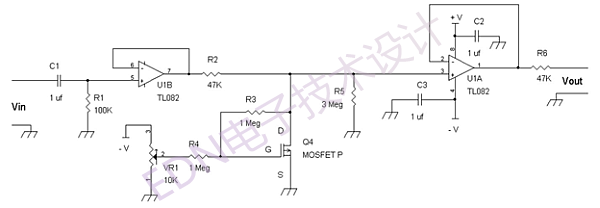

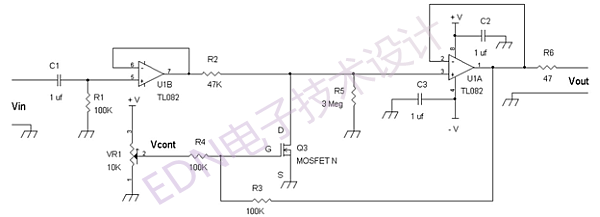

使用反馈网络来减少失真也可用于增强型MOSFET(图10)。

图10:带反馈网络的N沟道MOSFET压控衰减器电路可减少失真。

要消除增强型器件的失真,反馈网络R3和R4应该具有相等的电阻。然而,在某些情况下,使用缓冲放大器(如图14)可以更好地降低失真。

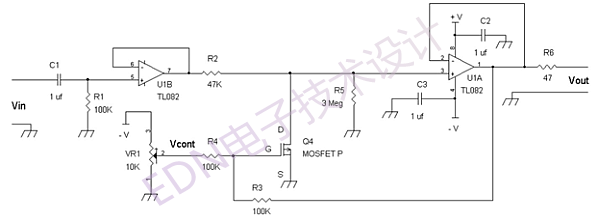

图11示出了一个P沟道MOSFET压控衰减器。

图11:利用电阻网络R3和R4来降低P沟道MOSFET压控衰减器的失真。

图8、9、10和11都是利用反馈电阻网络R3和R4来降低失真,但这种方式也有一些缺点:

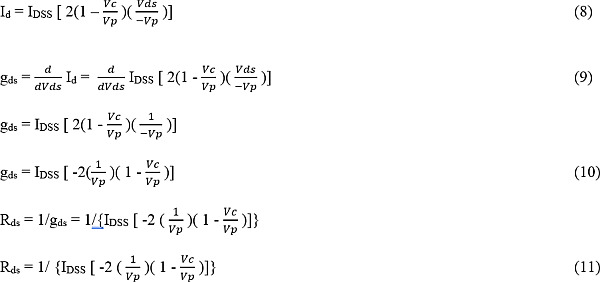

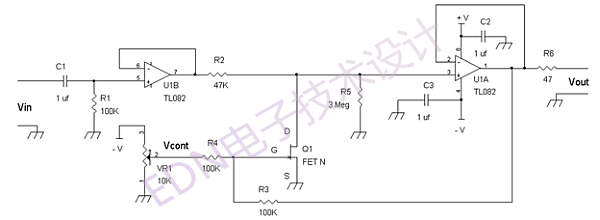

为了改进上面的第一点和第二点,图12、13、14和15利用电压跟随器U1A,将缓冲的漏-源电压反馈到栅极。

图12:通过R3和R4网络减少失真,利用U1A将缓冲的漏-源电压反馈到N沟道FET的栅极。

R3和R4的电阻值可以降低,而不会限制衰减范围。

请注意,这里没有添加其它器件,只使用了现有的输出缓冲放大器U1A。可以看出,电阻R3和R4不会再增加任何直流偏置或控制电压到FET的漏极端子。更重要的是,R3和R4的串联电阻不再与R5并联,也不再与FET的漏源电压控制电阻并联。

还有一个额外的好处,R3和R4可以是阻值较低的电阻器,这样控制电压可以在更高的频率下运行,而不必担心FET的栅源电容会降低频率响应。

类似地,图13显示了一个P沟道JFET的例子,图14和15显示了MOSFET例子。

图13:P沟道JFET压控电阻电路通过缓冲放大器U1A、利用电阻网络来降低失真。

无论信号是否被缓冲,通过反馈电阻网络R3和R4降低失真的效果都很好。但是,至少在MOSFET的一个例子中,缓冲器降低失真的效果要比通过R3连接漏极和栅极更好(图14)。

图14:N沟道MOSFET通过缓冲放大器U1A来减少失真。

对于N沟道MOSFET,比如SD5000 DMOS器件,使用缓冲放大器U1A(或等同产品)可以更好地降低失真,这要比使R3与漏极和栅极连接、R4连接到控制电压和栅极的效果更好。有关P通道示例,请参见图15。

图15:P沟道MOSFET衰减器电路通过电压跟随器U1A以及R3和R4来降低失真。

在图12、13、14和15中,失真减小了,并且反馈电阻R3与FET的漏极隔离。但是,我们应该观察到控制电压Vcont在FET的栅极中衰减了50%。

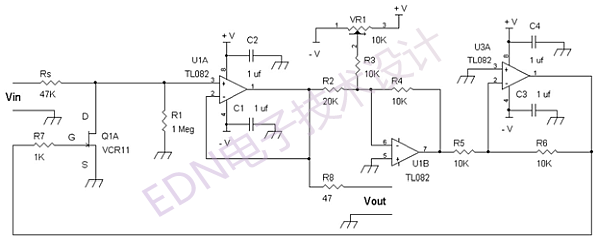

我们可以使用如图16和17所示的求和放大器将整个控制电压传输到栅极,这样就不需要两倍的控制电压。

图16:包含U1B和U3A的求和放大器电路可以避免控制电压衰减到Q1A的栅极。

为了提供从漏极到栅极的失真减少反馈,缓冲放大器U1A将漏极电压耦合到R2。由于U1B的反馈电阻R4(10kΩ)是R2(20kΩ)的一半,所以在U1B的引脚7处增益为-0.5。单位增益反相放大器电路通过R5、R6和U3A将U1B引脚7的相位反相,使Q1A漏极电压的一半发送至栅极。控制电压通过VR1无衰减地发送至Q1A的栅极。这是通过包含U1B和U3A的加法放大器电路完成的。图16示出了一个N沟道JFET Q1A,其中控制电压可从0V变化到–V。如果N沟道JFET变为P沟道JFET,则控制电压将从0V变化到+V。电阻器R7为FET的栅极提供一些保护,因为在电源启动状态下有可能引起栅极正向偏置到源极结点。

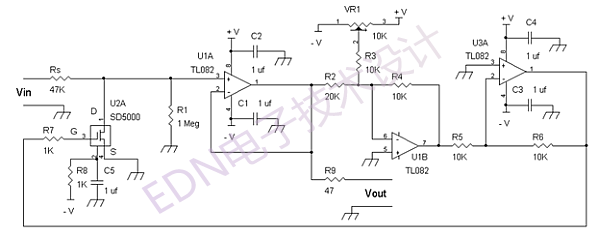

类似地,对于图17中的N沟道MOSFET,有一半的漏极信号电压通过U1B和U3A传输回栅极。R2和R4在U1B引脚7上构成一个50%反相增益放大器。带R5和R6的单位增益反相放大器U3翻转U1B引脚7的相位,使得50%的漏极信号电压耦合到U2A的栅极。VR1通过单位增益放大器,包括带R3和R4的U1B,以及带R5和R6的U3A,将其全控制电压传输到U2A的栅极。

对于N沟道MOSFET,控制电压从0V变化到+V,而对于P沟道器件,控制电压从0V变到-V。

本系列文章的下一篇将介绍通过降低漏源电压来实现FET调制器电路和可变增益放大器。

图17:通过U1B和U3A求和放大器可从VR1传输控制电压而不会衰减。

(原文刊登于ASPENCORE旗下EDN美国网站,参考链接:A guide to using FETs for voltage controlled circuits, Part 2,由Jenny Liao编译。)

《电子技术设计》2018年9月刊版权所有,禁止转载。

最前沿的电子设计资讯

最前沿的电子设计资讯