现场可编程门阵列(FPGA)在众多高性能应用中发挥着关键作用。它们被广泛用于数据中心,工业应用,如广播视频、打印成像、医疗成像、工业控制、相机、会议和协作、数字标牌等等应用。

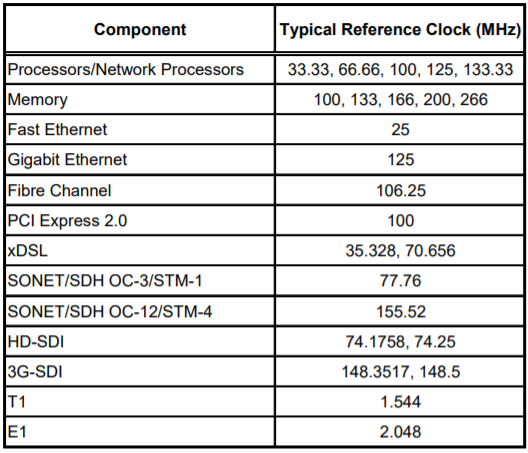

与前几代不同,目前的FPGA需要使用多个参考时钟(图1),这些时钟对精度要求很高,而无法采用某个基准频率时钟,对其进行整除而得到。高端FPGA是片上系统(SoC)器件,内置处理内核,例如ARM Cortex内核,它们具有自己的一套参考时钟,或者,它们具有嵌入式串并转换器(SERDES),为了满足最终应用的误码率(BER)规范,而对抖动具有严格要求。

图1:高端FPGA系统中常见的一些参考时钟频率(图片来源:Silicon Labs)

本白皮书将讨论设计人员如何使用Silicon Labs创新的时序解决方案系列来满足这些新要求,并使用英特尔Stratix 10 FPGA给出了设计实例。

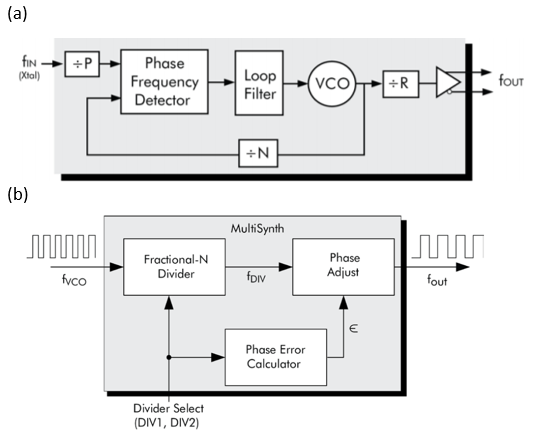

要想在满足严格空间限制和更紧上市时间的同时实现复杂的时钟树,需要使用新的时钟发生器设计方法。如图2(a)所示,传统架构基于简单的整数N分频锁相环(PLL),它以所需频率的倍数产生压控振荡器(VCO)输出;VCO提供一个R分频模块,进而产生最终输出。

图2:(a)传统PLL和(b)MultiSynth时钟发生架构的比较(图片来源:Silicon Labs)

在此架构中,输出时钟频率是输入时钟频率和PLL分频器值的函数,如下所示:

![]()

基于单PLL的传统架构适用于对参考输入实现简单的整数时钟倍增,或基于某个晶振输入来实现时钟生成。然而,高端FPGA需要多个非整数相关的频率:为了支持每个独特的频率规划,必须对晶振频率进行更改。设计人员必须使用一个或多个定制晶振和多个时钟发生器IC来生成一组所需频率,从而导致整体解决方案的成本、复杂性和功耗增加。

如图2(b)所示,Silicon Labs的MultiSynth™小数分频器专利架构解决了这个问题。MultiSynth架构用小数N分频器替换了图2(a)中的R分频模块,该分频器可在两个最接近的整数分频器值之间无缝切换,从而产生具有零ppm误差的精确输出时钟频率。

此过程会产生相位误差:为了消除相位误差,MultiSynth模块会计算小数N分频器时钟与所需输出时钟之间的相对相位差,并动态调整相位以匹配理想的时钟波形。

该技术可以在不牺牲抖动性能的情况下生成任何输出时钟频率。

Multisynth架构在Silicon Labs的时序解决方案组合中得到了很好的应用,其中包括业界最广泛的晶体振荡器、时钟发生器、时钟缓冲器和抖动衰减器系列产品组合。

|

Oscillators |

Clock Gems |

JA Clocks |

|

|

<100fs RMS |

|||

|

100-200fs RMS |

|

Si5341/0 |

|

|

200-500fs RMS |

|||

|

500-800fs RMS |

|

||

|

>1ps RMS |

|

|

图3:Silicon Labs时序解决方案组合结合了频率灵活性与同类最佳抖动性能(图片来源:Silicon Labs)

时钟发生器或抖动衰减时钟可提供多达12个输出,其最大频率为1028MHz,典型抖动低至69fs RMS。一系列输出类型均可支持,包括LVPECL、LVDS、HCSL、CML和LVCMOS。

图3按抖动性能级别划分对该产品组合进行了概要显示:顶部的器件提供最高性能的解决方案,针对最严格要求的最高端应用。

除MultiSynth架构外,时钟发生器还包括多种功能,而有助于降低抖动并节省系统成本。例如,电源噪声是高性能时钟器件中的一个重要问题。它以两种方式影响性能:

1.它会增加时钟信号电压和内部参考电压的噪声。由于交叉点时间是以内部生成的阈值电压为参考,因此该电压噪声会以时序误差的形式而出现在输出中。

2.电源噪声会由PLL中的内部振荡器调制,并导致相位噪声。

基于开关拓扑的电源由于其非常高效,因此是大电流、低电压设计的首选。不幸的是,它们也会产生很大的噪声,因此FPGA系统设计人员必须添加低噪声低压差(LDO)线性稳压器、铁氧体磁珠和众多滤波电容,以便在电源噪声到达时钟发生器之前将其消除。这会增加显著的成本并增加电路板尺寸。

Silicon Labs的器件在芯片上包含多个LDO,从而大大消除了对这些外部元件的需求。

输出缓冲电路的电源采用独立的内部LDO调节,可将时钟输出缓冲电路与电源引脚上的噪声相隔离。内部数字、输入缓冲器和模拟电路的电源还具有独立的内部稳压器电路,可将内部振荡器与外部电源噪声相隔离。

电源噪声抑制(PSNR)比是个关键的数据手册参数:下面讨论的最新器件(如Si5341A和Si5332)的PSNR在25kHz时为-100dBc,在1MHz时为-91dBc。

因此,这些器件每个电源引脚只需要一对滤波电容,从而大大降低了系统成本和解决方案尺寸。例如,Si5332仅需采用18个电容器,而竞争器件需要用到LDO、电容器、铁氧体磁珠、二极管和电阻器等超过100个额外元器件。

ClockBuilder Pro

图4:CBPro软件(图片来源:Silicon Labs)

结合时序解决方案产品,Silicon Labs提供多种软件工具来帮助客户开发快速定制的解决方案。

ClockBuilder Pro(CBPro)是种软件工具,可简化从时钟树规范到可订购器件的工作。CBPro支持Silicon Labs的Si539x、Si5121x、Si5350/1、Si5338、Si5332、Si534x、Si538x和Si539x时钟发生器和抖动衰减器。

该工具使用逐步的GUI格式,其中包含超过175个时钟设计规则,从而减少设计和调试时间。内置时钟布局向导将各个时钟分配给特定输出,从而最大限度地降低串扰的可能性。配置完器件后,即可立即获得具有相位噪声图的定制性能报告。

该软件支持直接连接所有相关的EVB和CBPro现场编程器。CBPro还支持在系统编程,允许系统人员在该系统板上重新配置器件。

CBPro软件包可免费下载。它包括应用程序可执行文件、发行说明、CLI(命令行界面)文档和一般培训信息。

其他软件工具包括相位噪声到抖动计算器,可帮助将FPGA相位噪声规范转换为抖动要求。

开发参考时钟设计包括以下步骤:

以下是一个使用英特尔®Stratix® 10GX FPGA开发套件中默认频率的设计示例。Stratix 10是英特尔最高性能的FPGA系列——Stratix 10 GX最高可达10TFLOPS,收发器支持高达2.8Gbps。

Stratix开发套件中要用到15个参考时钟,如下表所示。它们的范围从50MHz到644.53125MHz,可以发挥各种作用:Stratix 10 FPGA和MAX V CPLD(复杂可编程逻辑器件,一种低成本、更简单的FPGA变种器件)的系统时钟,以及通用通信标准(如以太网、DisplayPort和高速收发器)的参考时钟。

|

Device |

Clock |

Frequency (MHz) |

Level |

Function |

|

REFCLK1 |

155.52 |

LVDS |

Transceiver ref. clock Bank 1D |

|

|

REFCLK_QSFPI1 |

644.53125 |

LVDS |

QSFP ref. clock |

|

|

REFCLK_DP |

135 |

LVDS |

DisplayPort ref. clock |

|

|

REFCLK4 |

156.25 |

LVDS |

Transceiver ref. clock Bank 4E |

|

|

REFCLK_FMCA |

625 |

LVDS |

FMC ref. clock |

|

|

FPGA_OSC_CLK1 |

125 |

LVCMOS |

FPGA configuration clock |

|

|

CLK_ENET |

125 |

LVDS |

Ethernet clock |

|

|

MAXV_OSC_CLK1 |

125 |

LVCMOS |

MAX V CPLD clock |

|

|

CLK_CONFIG |

125 |

LVCMOS |

MAX V CPLD clock |

|

|

CLK_MAXV_50M |

50 |

LVCMOS |

MAX V CPLD clock |

|

|

CLK_FPGA_50M |

50 |

LVCMOS |

FPGA clock |

|

|

PCIE_OB_REFCLK |

100 |

LVDS |

Onboard PCIe ref. clk |

|

|

CLK_HILO |

133 |

LVDS |

HiLo memory clock |

|

|

CLK_FPGA_B3L |

100 |

LVDS |

FPGA clock Bank 3L |

|

|

REFCLK_SDI |

148.5 |

LVDS |

SDI ref. clock |

表1:Stratix 10 GX开发套件中的默认时钟

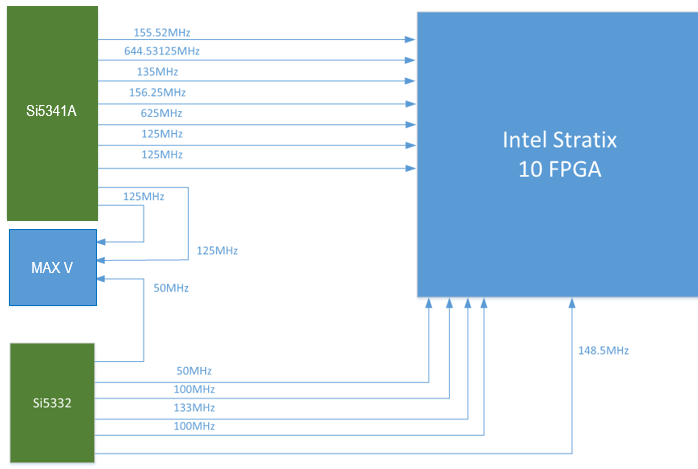

这些时钟仅用两个硅时钟发生器就可提供,如图5所示。

图5:仅用两个Silicon Labs时钟发生器就可为英特尔Stratix 10开发套件提供所有默认时钟(图片来源:Silicon Labs)

该设计中用到了Si5341A和Si5332。为什么选择这些器件?

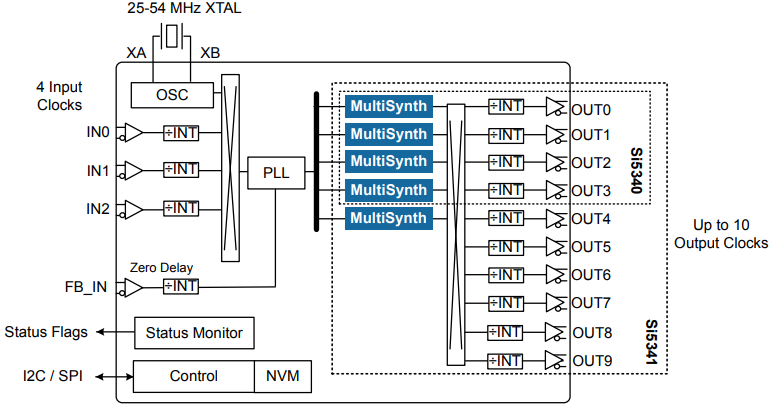

Si5341(图6)可提供10个输出:100Hz-1028MHz的频率范围可用于差分输出,或100Hz-250MHz可用于LVCMOS电平,且抖动仅为90fs RMS。可采用晶振或外部差分输入提供输入频率。输出可配置为满足LVDS、LPECL、LVCMOS、CML和HCSL规范。

图6:Si5341可产生十个独立的参考时钟(图片来源:Silicon Labs)

其余五个输出则由Si5332提供。该器件配有6个、8个或12个输出。输出时钟可达到333.33MHz差分和170MHz LVCMOS,相位抖动低至175fs RMS,足以满足应用需求。Si5332还提供一个嵌入式晶振,从而可进一步降低成本和尺寸。

为高性能FPGA设计设计参考时钟树是一项艰巨的任务,而Silicon Labs的时钟发生器产品组合提供了一种灵活而强大的方法来满足这些严格的要求。得益于ClockBuilder Pro软件工具,设计人员现在可以开发出最佳解决方案并快速评估样品器件。

本白皮书演示了使用Silicon Labs解决方案为英特尔Stratix 10 GX提供时钟。

最前沿的电子设计资讯

最前沿的电子设计资讯