之前讨论的FET电路属于压控信号幅度电路。也就是说,输入信号的幅度可以通过控制信号在输出端改变,该信号可以是DC信号,也可以是调制信号。请注意:输入信号电平应保持在150mV峰峰值以下,以避免图29至32中的失真。尽管图29、30和31显示了压控FET器件LSK489,但VCR11 FET可能会提供更好的失真性能。

我们可以进一步构建一个电路,在输出端提供电压控制相位,或者提供相位调制,参见图29、30、31和32,它们是“全通”相移电路。注意图29至32的Vin具有非常低的输出源阻抗(<50Ω),而且是由诸如运放这样的放大器提供。

对于每一个电路,R17 = R18,这样通过Vout和Vin提供了一条单位增益反相放大的路径。在有C14的另一路径上,FET(图29、30、31中的Q2B,以及图32中的U2A)和R19经由Vphase_mod形成一个压控可变频率高通滤波器。

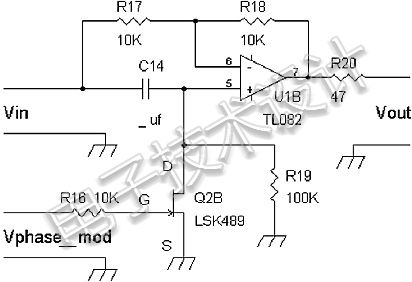

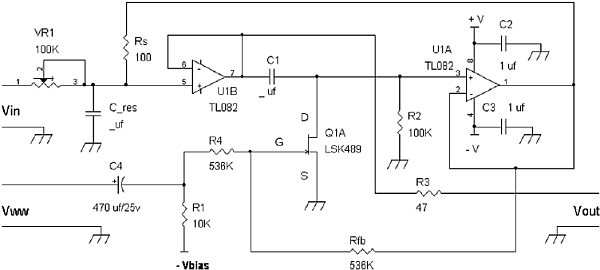

图29示出了JFET电压控制的移相电路。

图29:一个带JFET和Vphase_mod的基本相移电路,通常连接到以地为参考的电压源。

增益|Vout/Vin| = 1,但相位φ是Vout相对于Vin的变化度数:

φ = - [180° – 2arctan(f/fc)]

其中fc = 1/(2πRC),R = Rds||R19且C = C14,Rds是FET Q1B的漏源极电阻。

例如,若f = fc,那么φ = - [180 ° – 2arctan(1)] = - [180° – 2x45°],即φ = -90°。

例如,Vphase_mod = DC偏置电压 + AC调制信号。

在这种情况下,相位调制电压是介于0V与夹断电压Vp之间的负电压。对于LSK489,Vp可能是-3.5V。例如,-3.5V ≤ Vphase_mod ≤ 0V。

输入信号Vin应保持在<500mV峰峰值,以确保图29中的低失真。但如果想要更低的失真,我们可以通过Rfb与FET压控电阻(Q2B、Q2B和U2A)来应用反馈,如图30至32所示。

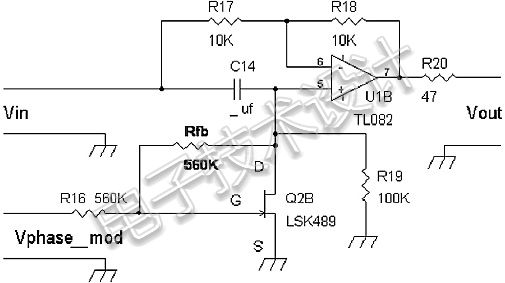

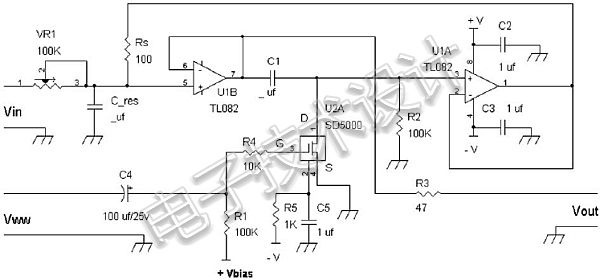

图30:更低失真的相移电路使用了反馈网络Rfb和R16。

增益|Vout/Vin| = 1,但相位φ是Vout相对于Vin的变化度数:

φ = - [180° – 2arctan(f/fc)]

其中fc = 1/(2πRC),R ∼ Rds||R19||(Rfb + R16)且C = C14,Rds是FET Q2B的漏源极电阻。

由于反馈网络将控制电压范围降低了50%,我们必须增加Vphase_mod的电压范围:

2Vp ≤ Vphase_mod ≤ 0V

对于LSK489,Vp可以是-3.5V,或

2(-3.5V) ≤ Vphase_mod ≤ 0V,即:

-7.0V ≤ Vphase_mod ≤ 0V

例如,Vphase_mod = DC偏置电压 + AC调制信号。

虽然反馈网络减少了失真,但它却将Vphase_mod的一部分泄漏到输出Vout。例如,如果Vphase_mod是低频信号,而Vin是较高频率的信号,则Vout不但包括相位调制的较高频率输入信号,还包括与Vphase_mod相关的低频信号。图31和图32中的电路解决了这一馈通或串扰问题。

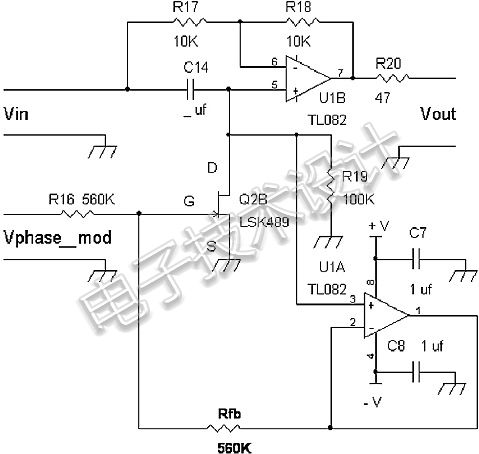

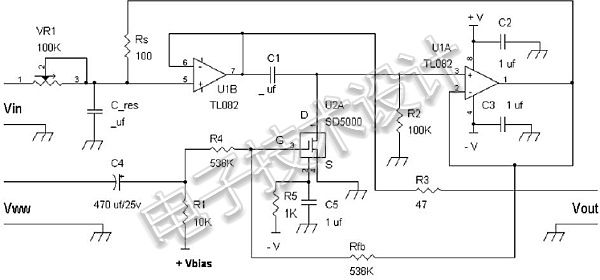

图31:带反馈和缓冲放大器U1A的压控相移电路。

增益|Vout/Vin| = 1,但相位φ是Vout相对于Vin的变化度数:

φ = - [180° – 2arctan(f/fc)]

其中fc = 1/(2πRC),R ∼ Rds||R19且C = C14,Rds是FET Q2B的漏源极电阻。

通过使用缓冲放大器,不仅减少了失真,而且从Vphase_mod到输出Vout的馈通或串扰也消除了。

控制范围再次变为:

2Vp ≤ Vphase_mod ≤ 0V

对于LSK489,Vp可以是-3.5V,或:

2(-3.5V) ≤ Vphase_mod ≤ 0V,即:

-7.0V ≤ Vphase_mod ≤ 0V

例如,Vphase_mod = DC偏置电压 + AC调制信号。

重申一下,对于图27至31,可以通过使用VCR11 FET降低失真。但要提醒的是,在图27至32所示的电路中,输入信号电平应小于150mV峰峰值。

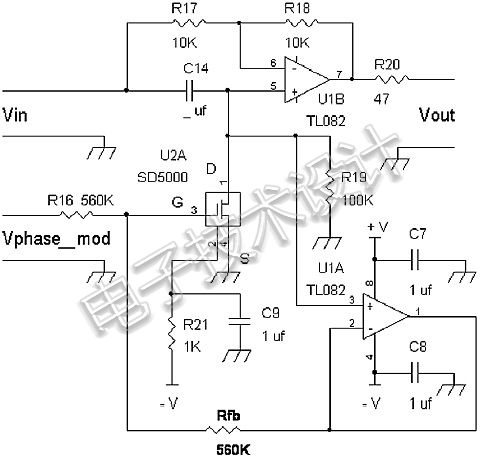

图32示出了一个电压控制的MOSFET电阻器移相电路。

图32:带有反馈网络和缓冲放大器的MOSFET移相电路可以降低失真。

增益|Vout/Vin| = 1,但相位φ是Vout相对于Vin的变化度数:

φ = - [180° – 2arctan(f/fc)]

其中fc = 1/(2πRC),R = Rds||R19且C = C14,Rds是FET U2A的漏源极电阻。

由于MOSFET U2A是增强型器件,所以Vphase_mod > 0V。MOSFET通常在+4.0V导通。然而,反馈网络R16和Rfb有50%的损失,所以我们需要将Vphase_mod的电压范围加倍到8V。也就是:

+0V ≥ Vphase_mod ≥ +8.0V

例如,Vphase_mod = DC偏置电压 + AC调制信号。

再次注意,缓冲放大器U1A防止Vphase_mod与Vout发生串扰。

对于音乐效果,有时反而需要失真,Vin的幅度可以增加到超过500mV峰峰值,以便为图29到32中的Vout增加失真。

Wah-Wah电路的一个基本构建模块是可变频率带通滤波器。通过调制带通滤波器的谐振频率,输入信号将具有幅度和相位变化。使用低频信号可在音乐上产生“哇哇”效果。

对于图35至39所示的电路,Vin输入信号电平应小于150mV峰峰值。

通常,一个并联电感电容(LC)振荡电路会采用固定的电感器L(如100mH到1000mH),而电容器则是可变的,通过米勒电容倍增器效应来改变。这个可变电容Cvar提供了一个可变的谐振频率:

![]()

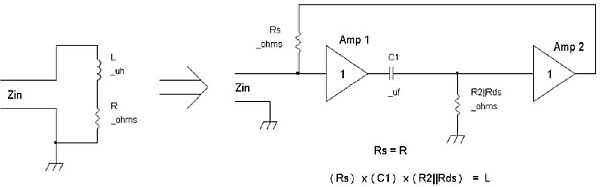

当然,我们也可以用一个固定电容和一个可变电感来制作等效的可变谐振频率电路(见图34):

![]()

图34:左侧电路中的电感器在右侧电路中作为模拟电感器(回转器)。

回转器的电感L = Rs x C1 x R2||Rds,其中R2如图35至39所示,Rds是图35至39中FET的漏源极电阻。Rs是等效电感串联电阻R。

为了解右侧的回转器是如何工作的,我们可以观察电感器在DC(0Hz)和非常高频率下的阻抗大小。

在DC时,电感器的阻抗大小恰好是等效串联电阻R,见图34的左侧。现在让我们来看回转器。在DC时,电容器C1阻止任何DC电压进入Amp 2的输入。因此,在DC频率下,Amp 2的输入接地,这意味着它的输出也接地。这时,回转器的Zin只是一个接地的电阻Rs,因为Amp 2的输出为0V。

现在让我们看一下频率非常高时左侧电感的阻抗。

Zin = R + jωL

其中j是虚数,j = √(-1),即j2 = -1,并且ω=2πf,其中f是频率(单位Hz)。

因为ω=2πf→无穷大,所以Zin→无穷大。

当频率→无穷大时,回转器的表现是否类似?

在右侧,电容器C1的阻抗为1/jωC1。因为ω=2πf→无穷大,所以C1的阻抗→0,或在高频时AC短路。这意味着Amp 1输入端的输入信号电压与Amp 2输入端的电压相同,因为Amp 1的增益为1。并且由于Amp 2的增益为1,因此Rs上端的电压与Amp 1输入端和Rs下端的AC电压相同。由于Rs两侧的AC电压相等,因此没有信号电流流入Rs。这就相当于Rs输入侧有一个开路。因为Amp 1的输入阻抗无穷大,我们发现在Zin点没有AC电流流动,这意味着当ω=2πf→无穷大时,Zin=无限大阻抗。

我们有一个回转器电路,其行为表现类似于在直流和高频时的电感。现在,让我们看一下在带通滤波器中如何使用像电感一样工作且有一个引线接地的回转器(图35)。

注意:对于采用有较高交流信号电流通过的FET作为压控电阻的电路,我们发现图35和图36中VCR 11 FET在失真方面的表现优于其它电路。具有较大夹断电压的FET可以处理更大的信号。通常,输入信号电平应小于150mV峰峰值。

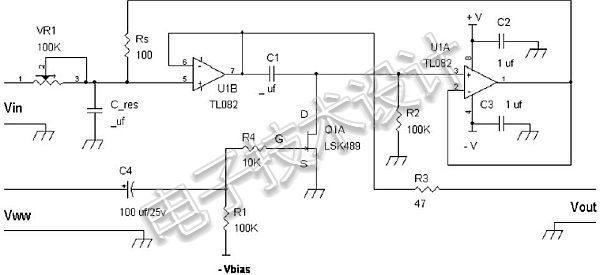

图35:带压控回转器的有源带通滤波电路。

快速浏览图35,可以看出这是一个回转器电路,其单位增益电压跟随器U1B和U1A用于图34中的Amp 1和Amp 2。Q1A的漏源极电阻与R2并联形成图34中的等效电阻器Rds||R2。图35中的Rs=100Ω,类似于图34中的Rs。由于回转器在引脚5 U1B/Rs结和接地端形成一个接地电感,因此通过电容器C_res连接到回旋器和接地而实现了一个并联LC电路。Vin通过可变电阻VR1将串联电阻驱动到并联LC谐振电路,其中L = Rs×C1×R2||Rds,且C1 = C_res。

我们可以在U1B引脚5的LC结处获取带通滤波器的输出,但最好通过引脚7处电压跟随器U1B的输出和输出电阻器R3来获取缓冲输出。这样,输出端的任何负载Vout都不会影响带通滤波器的特性,例如有载品质因数Q或增益。请注意,R3为47Ω,它将运算放大器与容性负载隔离,否则可能导致U1B振荡。

重申一下,在U1B的引脚5和Rs连结处,有一个以地为参考的电感。电感L = Rs x C1 x R2||Rds,电容C_res与该电感并联。

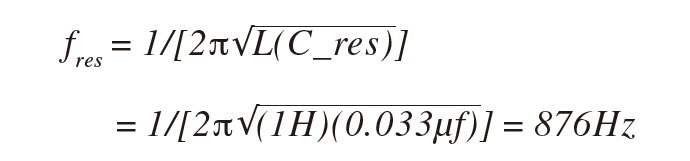

例如,若L = 1H,C_res = 0.033µf,则谐振频率为:

Vin是输入信号(比如音符),Vww是低频(0.5Hz到5Hz)“Wah-Wah”信号,其峰峰值约为1到2V。

Vbias设置FET Q1A的Rds,对于LSK489,这一电压通常在0到-3.5V之间。

在音频频率下,L的典型值约为1H,因此无载品质因数Qu仍然相当高,可达10或更高,它是由L、Rs和频率fres确定的,Qu ∼ 2πfresL/Rs。

例如,若fres = 1000Hz,L = 1H且Rs = 100Ω,那么Qu = 6.28(1000)(1)/100 = 62.8。

无载Qu与频率fres成正比。因此,如果想要一个fres = 500Hz的带通滤波器,那么无载Qu将从62.8下降到31.4。

通常,我们希望无载Qu >> 有载Qloaded。其中:Qloaded = 2πfres RC_res,R是VR1的电阻。

在音频滤波中,通常Qloaded < 10就可以了。

例如,若L = 1H,且C_res = 0.033µf,那么谐振频率:

假设VR1 = 25kΩ = R,那么:

Qloaded = 2πfres RC_res = 2π(876Hz)(25kΩ)(0.033 µf)

Qloaded = 4.54

实际上Qloaded会略低于4.54,因为无载Qu不是无限大的。但只要Qloaded值的偏差在10%或20%之内,近似值是可以的。通过增加VR1的阻值可以提高Qloaded值。因此,改变VR1电阻值即可控制Qloaded。

–3dB带宽是BW-3dB ∼ fres/ Qloaded = 876Hz/4.54,即:

BW-3dB =192.9Hz

因此,让我们选择图35的一些元件值,它们同样也适用于图36至39:

Rs = 100Ω

C1 = 1µf

FET Q1A的Rds = 11kΩ

R2 = 100kΩ

Rds||R2 = 11kΩ||100kΩ = 10kΩ

L = Rs x C1 x Rds||R2 = 100 x 1x10-6 x 10000H = 1H

fres = 1/[2π √ L(C_res)]

当Rds = 10kΩ, Rs = 100Ω, R2 = 100kΩ,fres在不同的频率范围时,我们有:

fres ≥ 700Hz, C1 = 1µf ,L = 1H;

200Hz < fres < 700Hz, C1 = 2.2µf,L = 2.2H ;

fres < 200Hz, C1 = 4.7µf,L = 4.7H。

注意C1应该是薄膜电容,比如聚酯或聚酯薄膜。

市售的额定电流为100mA的2H电感器,其线圈电阻约为175Ω(Hammond 154M)。回转器或模拟电感器在1H时具有等效的100Ω线圈电阻。就电感与线圈电阻比而言,两者非常接近。

我们回过头去看图10,连接到FET漏极的电压跟随器提供缓冲,用于驱动反馈电阻,从而降低漏极到源极电阻的非线性电阻。幸运的是,在图35中,我们有第二个电压跟随器U1A,它是回转器电路的一部分,但也可以用作缓冲放大器来线性化FET的压控电阻(见图36)。

图36:通过反馈电阻Rfb可以得到更线性的压控电阻。

对于更线性化的Q1A Rds电阻,Vin输入电平可以更大。但是偏置电压-Vbias和Wah-Wah信号Vww因Rfb和R4分压电路而需要加倍。

图37示出了一个使用增强型MOSFET的基本压控带通滤波器,它具有与图35类似的特性。但是,请注意N沟道MOSFET U2A的偏置电压为正。同样,再次提醒,对于图37、38和39,Vin应小于150mV峰峰值。

图37:MOSFET压控带通滤波电路。

本质上,该电路类似于图35中的N沟道JFET。但请记住,MOSFET U2A的偏置电压+Vbias将在0到+4V的范围内。

同样,我们可以利用电压跟随器U1A来线性化U2A的漏极到源极电阻(见图38)。

图38:具有线性化漏源极电阻的压控MOSFET带通滤波器。

偏置电压和Wah-Wah信号Vww的范围由于分压电路Rfb和R4而需要加倍。

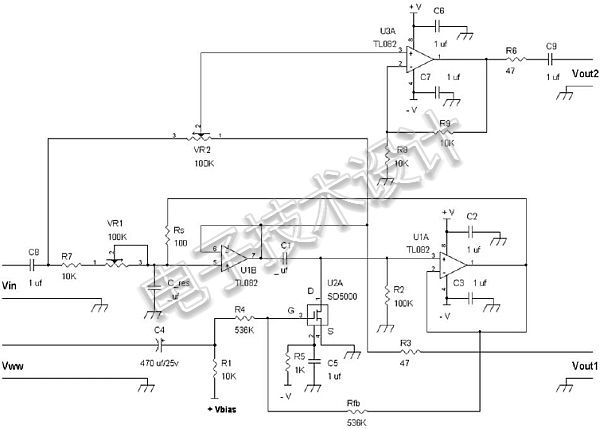

图39示出了一个更完整的压控带通滤波器,它有一个“混合”控制电位器VR2。

图39:混合控制电位器VR2允许将输入信号的一部分与带通滤波器的输出混合。

通过添加VR2,Vout2可提供输入信号和压控带通滤波信号的混合。调整VR2即可通过Vout2输出Vin的全部,或者Vin与带通滤波信号的混合,甚至带通滤波信号的全部。

Vout1仅提供压控带通滤波器输出。

我们现在转而采用更“自动”的方式来偏置FET。与基极-发射极导通电压范围很窄(0.6~0.7V)的双极晶体管不同,无论是耗尽模式下的夹断电压Vp,还是增强模式下的阈值电压Vth,FET都具有更宽的电压范围。

然而,我们可以利用两个(或四个)FET作为偏置参考器件来匹配JFET或MOSFET。

请继续关注本系列文章的最后一部分,我们将讨论用于自动设置的偏置伺服电路,以及一些提示和想法,还有一些非常有用的方程及推导公式。

(原文刊登于ASPENCORE旗下EDN英文网站,参考链接:A guide to using FETs for voltage-controlled circuits, Part 4。)

《电子技术设计》2018年11月刊版权所有,禁止转载。

最前沿的电子设计资讯

最前沿的电子设计资讯