SoC的设计越来越复杂,上市时间、软硬件集成、系统级验证、系统性能、异构、网络安全/功能安全等都是设计人员需要考虑的因素。流片前,设计师能通过仿真软件进行验证,但是流片过程中很多意想不到的结果,需要在流片后仍能被准确的检测出来。

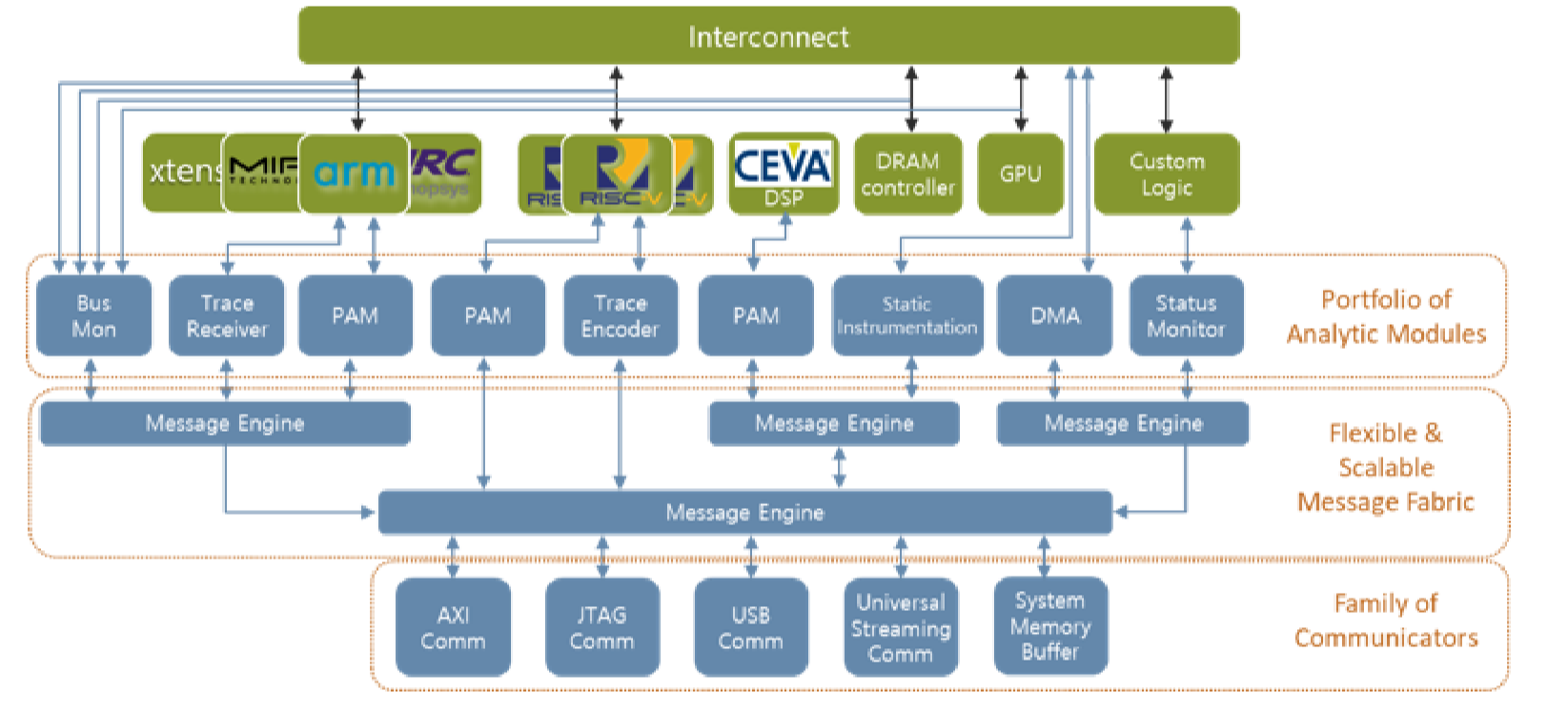

有人就盯紧了这个设计需求,专为SoC提供内部分析及监测技术,在SoC设计过程中,加入该公司的嵌入式分析IP/软件,不仅在流片前、还能在流片后、甚至在这颗SoC的整个生命周期内对SoC提供片上分析,同时发现SoC软硬件问题(以往需要两个软件)。

该技术帮助SoC设计师增加先进的网络安全、功能安全性以及性能微调等特性,可适用于任何主控处理器的SoC内部分析、追踪与监测技术。

这家总部设在英国的公司虽然只有二十几名员工,但有很多是设计界老将,其中Cadence公司的联合创始人Alberto Sangiovanni-Vincentelli现担任UltraSoC的董事长。

近日,EDN电子技术设计的记者参加了UltraSoC首席战略官Aileen Smith女士的午餐会,会上她分享了公司的最新动向。在加入UltraSoc之前,Smith女士在华为技术公司担任战略顾问兼生态系统拓展负责人。

“IC公司的SoC越是复杂,越需要我们的产品。”Smith表示。一年前,该公司还只有7家客户,但现在已增加到17家,包括海思、英特尔、Microchip、中天微C-SKY,以及IT系统集成商Kraftway等。

工程师可以利用UltraSoC的IP,清晰地了解芯片上不同的处理单元、定制化逻辑和系统软件之间的性能表现。

另外,这种嵌入式的解决方案,只进行监测,不干涉,不像使用探针方案可能会带来时序问题。

现在,许多安全标准都要求锁步操作,例如汽车领域的ISO26262、以及IEC 61508、EN50126 / 8/9和CE 402/2013。近日该公司推出的Lockstep Monitor(锁步监测器),通过检查关键系统核心单元的处理器内核是否在可靠、安全、无隐患地运行,显著地提高了其功能安全性。

RISC-V目前在中国热度很高,但其实其整个生态系统目前缺乏对诸如锁步操作等功能安全性和安全防护规则的支持 ,但是它们却是许多全球性标准强制要求的,如ISO26262强调的功能安全性、J3061强调的网络安全,以及IEC 61508、EN50126 / 8/9和CE 402/2013等全球性标准。UltraSoC的Lockstep Monitor锁步监测器支持无论是使用了开源还是商用内核的任何RISC-V系统去集成精密的安全功能。

事实上在2017年该公司就开发了RISC-V处理器追踪技术,并随后很快将其追踪规范提供给RISC-V基金会(RISC-V Foundation),用于基金会标准化工作的一部分。目前与包括晶心科技、Codasip、Roa Logic、SiFive和Syntacore等主要RISC-V内核供应商合作。

虽然UltraSoC支持市面上几乎所有的处理器架构,Smith表示同时也很希望借RISC-V打开更多市场,基于公司嵌入式IP的特性,如果未来还出现新的处理器架构,“我们一样可以轻松监测到。”

最前沿的电子设计资讯

最前沿的电子设计资讯