日前,台积电发布公告称:苹果A13芯片的生产订单被其拿下,且将继续采用7nm制造工艺。(详情:《台积电独揽苹果A13芯片生产,仍用7纳米工艺》)

三星电子早在2018年10月就已宣布其7nm LPP(Low Power Plus)制程也已进入量产阶段,而采用EUV 设备的台积电第二代7 纳米依预期会在2019年量产。

此外,SwmiWiki的创始人Daniel Nenni认为,三星与台积电不同的是,三星的产能一直都不成问题。而作为领跑的两家代工厂,三星在14纳米领先于台积电,在10nm和7nm节点被台积电反超,但是三星拥有业内最好的晶圆价格,在定价方面三星更有优势。

但为何苹果A13芯片的生产订单却是被台积电拿下呢?

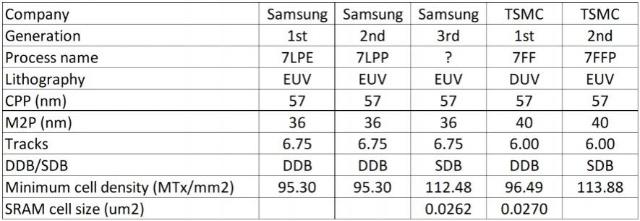

从工艺数据方面,国际公认的半导体专家和IC Knowledge的创始人Scotten Jones 给出的对比如下:

Contacted Poly Pitch (CPP) (接触间距)

- 台积电和三星都宣称7纳米的CPP为54纳米,但对于它们两者而言,我相信它们对电池的实际CPP为57纳米。

Metal 2 pitch (M2P)

三星是36nm,TSMC是40nm。

Tracks

三星最小单元Tracks高度为6.75,TSMC为6.0。

Diffusion break

TSMC光学工艺(7FF)是双扩散断路(DDB),据报道它们的EUV工艺(7FFP)将采用单扩散断路(SDB)。三星7nm有第一代工艺(我相信这是7LPE),是DDB,他们也有第二代工艺(我相信这是7LPP),也是DDB。在今年的VLSIT上,他们讨论了与SDB的第三代流程。很难知道这到底是什么,在10nm,他们的第二代工艺实际上是他们的8nm工艺,所以这可能是他们的5nm工艺,也可能是第三代7nm工艺。

Transistor density(晶体管密度)

TSMC 7FF的最小单元逻辑密度略好于三星7LPE或7LPP。台积电EUV 7FFP略好于三星“ 第三代”7nm。

SRAM cell size(SRAM单元尺寸 )

我认为所有三星三代以及台积电的两代的SRAM单元尺寸是相同的,但我不确定。三星的SRAM单元略小一些。

Scotten 认为,总的来说,这两家的工艺在密度上是相似的,但台积电会在产能提升方面会处于领先地位。

最前沿的电子设计资讯

最前沿的电子设计资讯