任何高分辨率信号链设计的基本挑战之一是确保系统本底噪声足够低,以便模数转换器(ADC)能够分辨您感兴趣的信号。例如,如果您选择德州仪器ADS1261(一个24位低噪声Δ-ΣADC),您可在2.5 SPS下解析输入低至6 nVRMS,增益为128 V / V的信号。

但是,从系统的角度来看,您需要担心的不仅仅是ADC噪声——毕竟所有组件(包括放大器、电压基准、时钟和电源)都会产生一些噪声——这些器件对系统噪声的累积影响是什么?更重要的是,您的系统能够解决您感兴趣的信号吗?

为助您更好地理解系统噪声并将这些知识应用到您的设计中,我最近撰写了一篇名为“解决信号”的技术文章系列。该系列探讨了典型信号链中的常见噪声源,并通过降低噪声和保持高精度测量的方法辅助理解。

以下是该系列中10个最关键的问题和答案,可帮助您开始使用精密ADC进行设计。

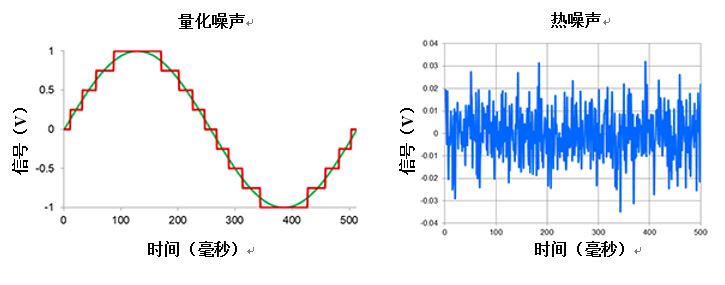

总ADC噪声有两个主要组成部分:量化噪声和热噪声。量化噪声来自将无限数量的模拟电压映射到有限数量的数字代码的过程(图1左侧)。因此,任何单个数字输出都可对应于数个模拟输入电压,这些电压可能相差一半的最低有效位(LSB)。

由于电导体内电荷的物理移动(图1右侧),热噪声是所有电子元件中固有的现象。不幸的是,ADC终端用户不能干涉器件的热噪声,因为它是ADC设计的一个功能。

图 1:量化噪声(左)和热噪声(右)

热噪声和量化噪声是否同样影响低分辨率和高分辨率ADC?阅读第1部分“Δ-Σ ADC中的噪声简介了解相关信息”。

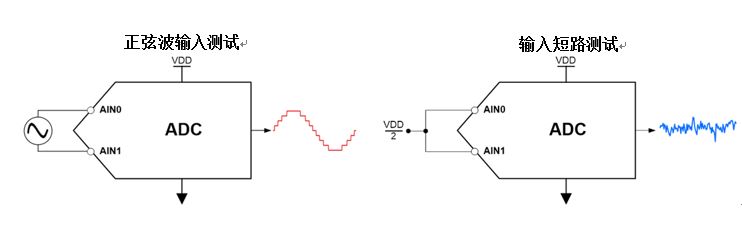

ADC制造商使用两种方法来测量ADC噪声。第一种方法将ADC的输入短接在一起,以测量由于热噪声导致的输出代码的微小变化。第二种方法涉及输入具有特定幅度和频率的正弦波(例如1kHz下为1 VPP)并报告ADC如何量化正弦波。图2展示了这些类型的噪声测量。

图 2:正弦波输入测试设置(左)和输入短路测试设置(右)

每类ADC使用哪种测量方法?请阅读第2部分中有关噪声测量方法和规范的更多信息。

对于ADC噪声分析,我建议使用输入参考噪声。我加粗此短语,因为使用输入参考噪声来定义ADC性能并不常见。实际上,大多数工程师只谈论相关参数,例如有效和无噪声的分辨率,而当他们无法最大化这些值时会深感担忧。毕竟,如果您只是使用24位ADC来实现16位ADC的有效分辨率,感觉就像您在为实际不会使用的ADC性能而买单。

但是,16位ADC的有效分辨率并不一定能告知您ADC将使用多大的满量程范围(FSR)。也就是说,您可能只需要16位有效分辨率,但如果最小输入信号为50 nV,则无法使用16位ADC来解决问题。因此,高分辨率Δ-ΣADC的真正好处是它能够提供的低输入参考噪声水平。这并不意味着有效的解决方案并不重要 - 只是它不是参数化系统的最佳方式。

第3部分使用无噪声分辨率和输入参考噪声定义系统噪声参数的设计实例进一步采用这些要求。哪一种能够实现最快、适应性最强的解决方案?阅读文章发现答案。

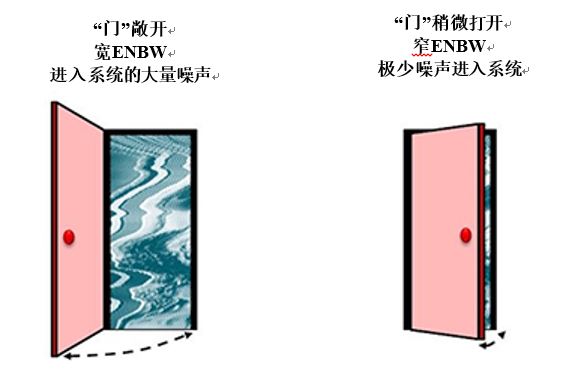

在一般信号处理术语中,滤波器的有效噪声带宽(ENBW)是理想的实际滤波器的截止频率fc,其噪声功率近似等于原始滤波器的噪声功率H(f)。

作为类比,您可考虑一下在寒冷的夜晚您家中的情况。为降低能源成本并节省资金,您需要尽可能地关闭门窗以限制进入的冷空气量。在这种情况下,您的家是系统,您的门窗是滤波器,冷空气是噪声,ENBW是衡量您的门窗是如何打开(或关闭)的。间隙越大(ENBW),进入家中(系统)的冷空气(噪声)越多,反之亦然,如图3所示。

图 3:宽ENBW会产生更多噪声(左);窄ENBW产生更少噪声(右)

哪些系统组件对ENBW有贡献?阅读第4部分以了解更多信息。

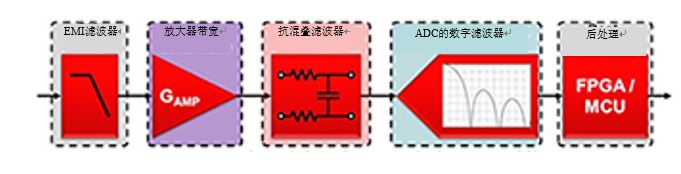

如果您的信号链有多个滤波器组件,则必须通过组合信号链中的所有下游滤波器来计算每个组件的ENBW。要组合滤波器,请将它们绘制为幅度(以分贝为单位)与频率的关系,然后逐点添加。

例如,要计算图4中放大器的噪声贡献,您必须将放大器的带宽与抗混叠滤波器、ADC的数字滤波器和任何后处理滤波器相结合。在这种情况下,您可忽略电磁干扰(EMI)滤波器,因为它相对于放大器位于上游。

图 4:显示多个滤波源的典型信号链

这可能很复杂,请阅读第5部分学习ENBW近似方法以简化分析。

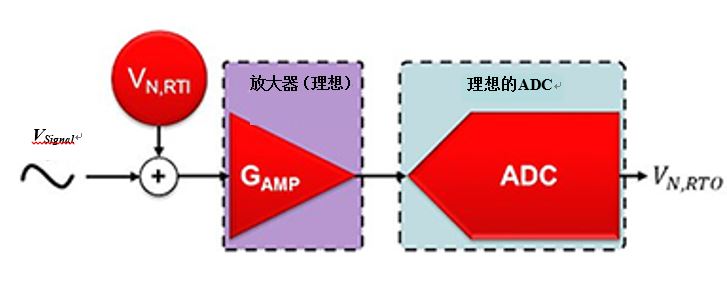

通过将ADC和放大器与各自的噪声源分开可更轻松地进行噪声分析。在这种情况下,您可将系统建模为无噪声放大器和无噪声ADC,前置条件是电压源等于两者的输入参考噪声,如图5所示。

图5:“无噪声”ADC和放大器通过参考输入总噪声前置

不幸的是,测得的输出噪声必须重新参考输入,因为输入参考噪声是大多数ADC数据手册中使用的规范。假设放大器和ADC噪声不相关,请采用两个值的和方根(RSS)来确定总输出参考噪声。您还需要通过放大器的增益GAMP来调整放大器噪声。公式1所示为得出的输出参考噪声:

如何将其转化为输入参考噪声?增益比例因子GAMP的后果是什么?阅读第6部分以了解相关信息。

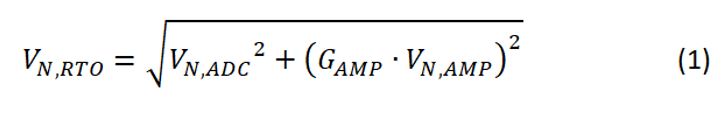

在第七系列文章中,我查看了一个示例,该示例在ADS1261的输入端添加了多个外部放大器,并测量了最终的噪声性能。然后,我使用其集成的可编程增益放大器将这些组合与ADS1261的基线噪声性能进行了比较。为了更容易比较,我在每种组合的不同增益设置下绘制了噪声,这提供了有关将外部放大器添加到精密ADC如何影响性能以及性能如何随增益变化的数个见解。图6描述了该示例。

图 6:根据增益比较不同放大器的噪声性能与和ADS1261的关系

这个示例和图6图表有哪些关键要点?阅读第7部分“放大器噪声对Δ-Σ ADC的影响”了解更多信息。

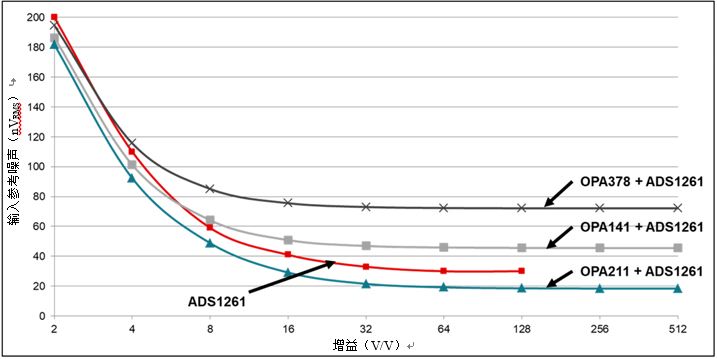

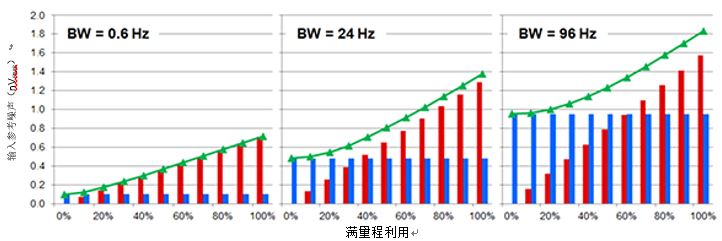

参考噪声最有趣的特征之一是它会随着您使用的ADC FSR的大小呈现线性变化:如果输入信号非常小,则不会观察到太多参考噪声 - 因此可能会使用较大噪声进行参考。或者,如果输入信号大于中刻度,则可预期参考噪声占主导地位。在这种情况下,请始终确保ADC噪声和参考噪声具有可比性。图7定性地绘制了作为FSR利用率函数的参考噪声、ADC噪声和总噪声。

图7:作为FSR利用率函数的参考噪声、ADC噪声和总噪声

这个图上的关键点 - A、B和C代表什么?更改输入信号与更改系统增益如何会影响参考噪声?在第8部分中找到这些问题的答案。

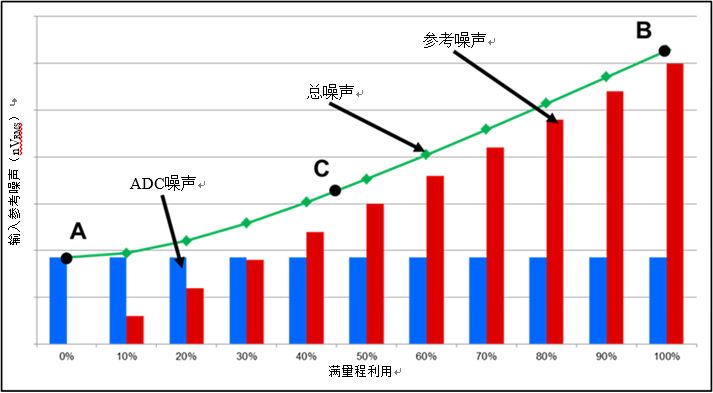

减少传入系统的参考噪声量的一种常用方法是限制系统的整体ENBW,这可通过降低ADC的输出数据速率来实现。图8所示为降低ADC输出数据速率如何同时降低ADC噪声和参考噪声。例如,在ENBW = 0.6 Hz(左)和ENBW = 96 Hz(右)之间,100%利用率下的参考噪声降低了2.3倍,而ADC噪声降低了10倍,远远少于总噪音。

图 8:限制ENBW可降低总噪声:0.6 Hz(左)、24 Hz(中)、96 Hz(右)

阅读第9部分了解参考配置如何减少传入系统的参考噪声量。

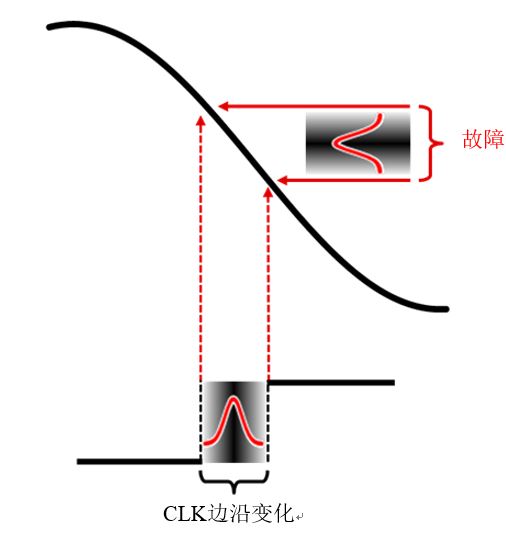

虽然我们期望ADC的采样周期完全恒定,但总会有一些与理想值的偏差。“时钟抖动”是指时钟波形从一个周期到下一个周期的边沿变化。由于所有ADC都使用时钟边沿来控制采样点,因此时钟边沿变化会在采样实例中产生偏差。该偏差导致在转换结果中出现的非恒定采样频率成为另一噪声源。图9所示为正弦输入信号上的时钟抖动引起的采样边沿变化。

图 9:时钟信号显示由抖动引起的采样边沿变化

了解时钟如何导致其他故障,以及降低因时钟抖动引起的系统噪声的方法,请阅读第10部分。

最前沿的电子设计资讯

最前沿的电子设计资讯