在一场于美国硅谷举行之年度半导体微影技术研讨会(编按:SPIE Advanced Lithography)的晚间座谈上,工程师们对半导体技术发展前景忧喜参半;他们认为半导体制程蓝图可再延续十年、达到1奈米节点,但也可能因为缺乏新的光阻剂(resist)化学材料,而在3奈米节点之前就遭遇发展瓶颈。

这场座谈会试图轻松看待早就被预言的「摩尔定律(Moore’s Law)将死」议题,也凸显了令人不安的不确定因素,尽管那都是会在新一代芯片发展过程中不断自然产生的种种挑战。

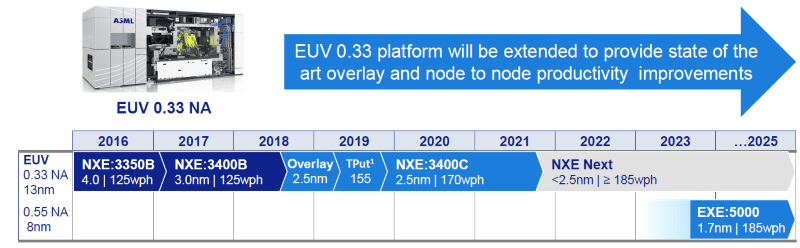

目前三星(Samsung)已经开始使用极紫外光(EUV)微影技术生产7奈米组件,台积电(TSMC)也预计在6月开始量产采用EUV微影的强化版7奈米制程(N7+)。而微影设备大厂ASML希望在今年透过升级其EUV系统(3400C)来服务这两家客户,并承诺达到每小时170片晶圆的生产速率和90 %以上的稼动率(availability)。

ASML计划在今年升级现有EUV系统。(来源:ASML)

接下来的一个重大挑战,是为3奈米节点开发出敏感度更高的光阻剂材料。ASML副总裁Tony Yen表示,现今的化学放大光阻剂(CAR)「对于当前和或许下一代节点来说可用,但我们想要新的平台;」,他指出,CAR的历史可追溯到1980年代的248奈米微影时代:「现在是时候将重点放在分子光阻剂等新平台上了。」

他补充指出,由于这种关键化学材料的市场总值每年不到10亿美元,「商业模式需要改变;技术开发能以竞争前(pre-competitive)研发方式进行,再授权给光阻剂供货商。」

但光阻剂制造商FujiFilm的代表Ryan Callahan不赞同这种方式:「为了确保生意的竞争非常激烈,因为谁能领先、谁就会成功,而其他人就没有机会了...再加上这个市场变得越来越小、有些半导体业者(例如GlobalFoundries)放弃了EUV;因此光阻剂供货商不会组成联盟合作研发。」

为了推动下一代EUV系统使用的光阻剂研发,比利时研究机构imec和专长激光技术的美国业者KMLabs宣布合作建立一个名为AttoLab的实验室,将尝试研究光阻剂如何在皮秒(pico-second)和阿秒(attosecond)单位的时间内吸收和离子化(ionize)光子。

imec首席科学家John Petersen 表示:「我们将研究如何理解辐射化学(radiation chemistry)的细节,并与供货商合作寻找新材料,将我们推向下一个境界...我们也将研究量子现象...这是纯科学,但新技术可能就来自这类研究;」他共同撰写了描述新实验室的报告。

光阻剂是减少半导体制程随机误差(random errors),或称「随机效应」(stochastics)的一种方式;这个老问题随着制程技术朝5奈米节点推进,有越演越烈的趋势。不过ASML的Yen乐观认为该公司能应付这个影响良率的缺陷。

「随机效应问题会比193奈米微影时代更严重,但可以透过更高的(光)剂量来抵消;」Yen表示:「我们的蓝图已经规划至500-W系统,功率更高,而高数值孔径(NA)系统将提供更好的成像质量,因此我们已准备好因应随机效应问题。」

但imec的度量专家Phillipe Leray对此不太乐观。「我们必须在短时间内解决这个缺陷挑战;」他表示:「时间不多了,但我还看不到任何解决方案可能很快出现。」

Arm的研究院士Rob Aitken表示,为了一颗逻辑芯片内的10亿个实体触点之中或许会有一个发生故障的可能性,工程师们正在设法弥补:「已经有几种解决问题的候选方案。」

有鉴于芯片堆栈技术的成功,Aitken是座谈会上呼吁更关注3D架构的与谈专家之一;他认为,这类技术需要一种「新的微架构(microarchitecture),因为3D设计的复杂性很高,除了注意到功率与频率问题会很困难,没有人做更进一步的研究。」

另外,他表示设计工程师已经准备好从12轨和9轨标准单元(standard cells),转向仅使用4轨的标准单元以实现制程微缩:「这在几年前是不可能的,但现在有可能了。」

实际上,相关挑战非常严峻,工程师正将所考虑的解决方案范围,扩大到芯片技术的各个领域。「我们正在看关于先进图形化(patterning)技术的所有面向,」技术顾问Erik Hosler表示,EUV就是从年度微影技术大会中,由目前他协助监督的先进图形化方案讨论小组中诞生。

Hosler原本在GlobalFoundries担任EUV技术专家,他指出:「去年,我们将微机电系统(MEMS)以及微光机电系统(MOEMS)技术纳入讨论,我们将继续扩大范围,使这场会议成为一个提出问题的地方...很多有意义的事情正在发生、也会出现某些突破。」

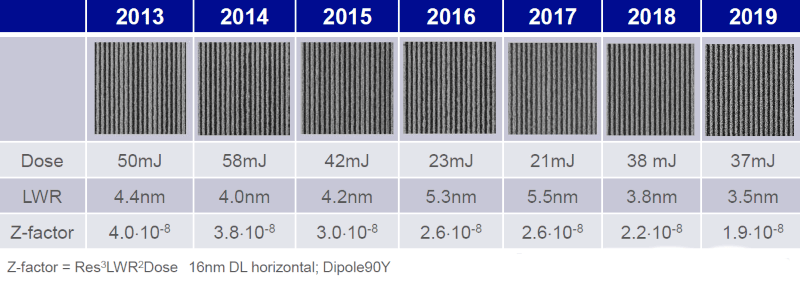

工程师们已经在为EUV提供更好的功能方面取得了重大进展。(来源:ASML)

一直以来,工程师们都在芯片技术蓝图中摸索解决方案;如imec的Leray举例指出,今日的测试系统不能要求准确性,因此他们就专注在一致性(consistency)。他表示:「有鉴于直接检测的困难程度,度量是我最大的恐惧...还有很多波长是我们不曾探索的。」

而所有与谈专家一致认为,考虑到成本和有限的报酬,转向18吋(450mm)晶圆和9吋光罩是少数几个不值得钻研的技术领域之一。美国半导体设备业者Lam Research技术经理Rich Wise表示:「我们在几年前对18吋晶圆技术投入不少精力,但这需要一个完整的生态系统,不然很难推动改变。」

在座谈会最后,两位主持人做出直率且乐观的结论。曾在AMD与GlobalFoundries负责微影技术超过30年的Harry Levinson表示:「我们正在取得进展,但我们推断,当特征尺寸小于硅原子直径,由微影技术所推动的制程微缩也会走到终点。」

「极限确实存在,而绕过它们最好的方法是改变典范(paradigm);」资深顾问和微影技术作者Chris Mack表示:「砖墙通常存在我们自己的脑海,但创新可以移动它,然后我们就可以继续向前迈进。」

(原文发表于ASPENCORE旗下EDN姐妹媒体EETimes,参考链接: Chip Roadmap Looks Dark, Bumpy ,责编:Judith Cheng,EETTaiwan;本文同步刊登于电子工程专辑杂志2019年4月号)

最前沿的电子设计资讯

最前沿的电子设计资讯