从直流精度的角度看,高速放大器的发展过程一直就是在提高精度、提高压摆率——这与大信号带宽(LSBW)相关。电流反馈放大器(CFA)本身有极高的压摆率,却具有相对较差的DC精度。电压反馈放大器(VFA)的压摆率也已经通过许多方法得到了提高,此篇将会介绍这些方法。全差分放大器(FDA)有两种选择类型,其中基于CFA的类型具有非常高的压摆率和较差的DC精度,而基于VFA的FDA利用类似的技术来提高精度,并与核心VFA一样具有较高的压摆率。FDA因为多了共模控制回路,带来了一些新的DC精度考虑因素。本篇是这个系列的第三部分,将介绍几种不同的VFA方法,第四部分将讨论CFA和FDA的DC精度考虑因素。

可实现的DC精度(和噪声)在很大程度上是输入级设计问题。VFA有一些天然优势来降低DC误差。回想一下,VFA的第一级DC误差是三个输入误差项,许多早期参考文献都提到了如何利用它们来计算输出误差。

有时,一些其它误差项和输入失调电压混淆在一起。物理输入误差电压有Vout/Aol项,由于该项与输出信号电平有关,因此可以通过输出的增益误差正确得到。由开环增益(Aol)引起的输入误差电压没有加到静态DC输入失调电压上,而是由LG/(LG+1)所描述的增益压缩项计算,其中LG=Aol/NG,NG=噪声增益。那么,当VFA运算放大器在单位增益、分离平衡电源及接地非反相输入条件下工作时,输入失调电压是多少?由于输出电压工作会非常接近于地,因此在输入差分级内部,误差电压应该非常接近0V。观察到的外部失调电压是输入级不对称所需的补偿电压,使内部实际误差电压达到零。

在20世纪80年代初,典型的VFA增益带宽积(GBP)稳步增长,可是它们的压摆率并没有跟上增长步伐,比如一个典型的单位增益稳定高速Harris运算放大器具有的小信号带宽(SSBW)远超其LSBW。到大约2004年,有了两种主要方法来增加VFA器件的LSBW:使用仿真CFA工作的输入级或提供解补偿放大器。非单位增益稳定、解补偿VFA器件减小了补偿电容值,通常增加了输入级gm(输入级中负反馈R较低,也使输入噪声较低)。因此,对于补偿电容上大致的近似转换电流值,可以得到更大的压摆率。提高压摆率的同时改善DC精度和噪声,也是降低电源电流时要考虑的。在静态电流更大的情况下,总是可能提高压摆率并降低输入电压的噪声。本文提供了在越来越低的静态电流下改善这两项指标的解决方案。

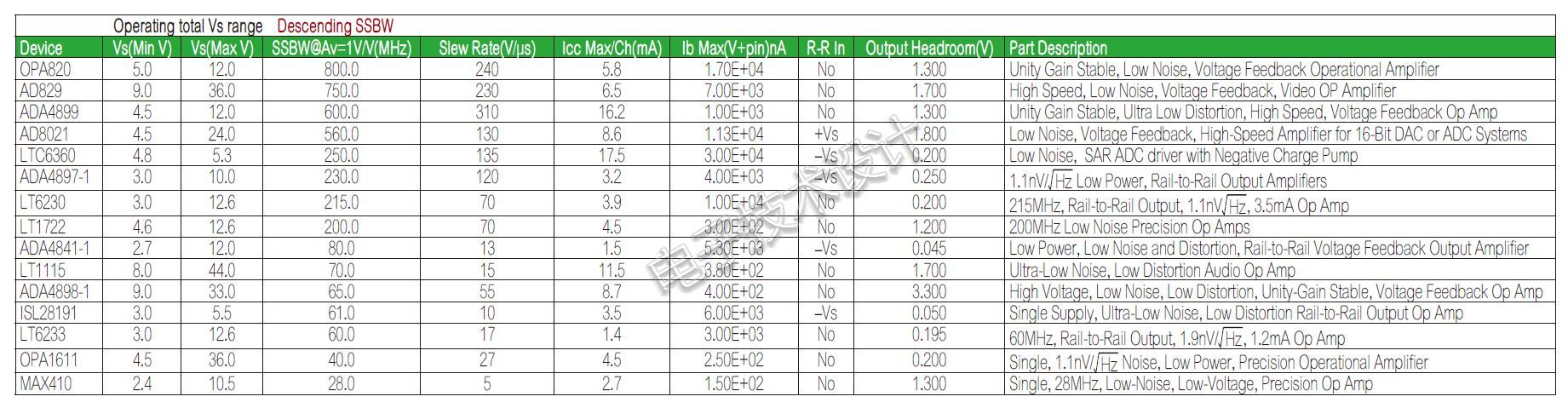

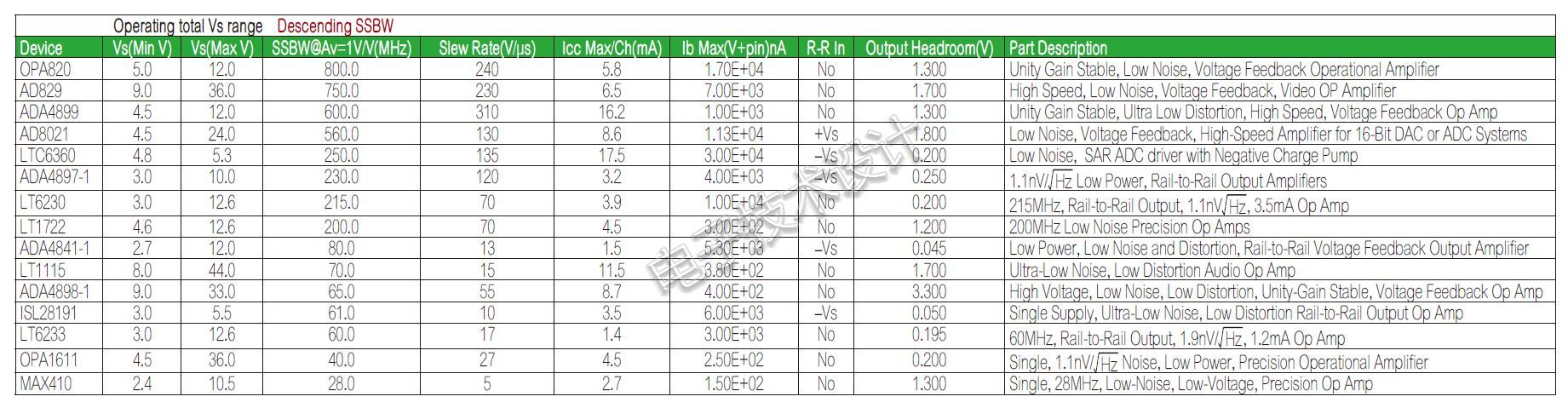

首先,让我们回顾一下单位增益稳定、非压摆增强型高速(>20MHz)VFA选择。压摆增强型单位增益稳定VFA可按LSBW/Icc值的降序排列出来。它们将出现在后面的表中,现在先讨论中等压摆率、低噪声、精密、单位增益稳定的VFA。最近推出的许多VFA包含轨到轨输出(RRO)和负轨输入(NRI),或轨到轨输入(RRI)。一些低噪声器件是非RRIO设计。RRI器件利用交叉网络(x-over network)或内部电荷泵,使输入级偏置超出所应用的电源。为了在整个可用的输入范围内显示更好的直流偏置器件,表1~表3中将不包含RRI器件。单位增益稳定VFA器件长期以来难以提供低输入电压噪声,而最近的几个版本似乎突破了这一桎梏——最初表现出较高的电源电流或低得多的压摆率,但提供了改进方案(见表1)。还有许多低失调、更高速、单位增益稳定的CMOS或JFET输入器件,它们通常显示出更高(>4nV/√Hz)的输入电压噪声,在LSBW/Icc比率时也不够节能。其优点是可以消除输出DC失调计算中的输入偏置和失调电流误差。

表1列出了具有代表性的非压摆增强型、单通道、单位增益稳定VFA器件,它们同时提供低失调电压(≤1mV最大值)和较低的输入电压噪声(<4nV/√Hz)。后面的三个表格显示了通过不同的方法来提高压摆率。这些低噪声和偏置器件都是双极型的。因此,要想获得低的输出失调就需要在设计中使用偏置电流消除电路。如果能正确做到这些,就能减少由于Rf x Ios的输入偏置电流引起的输出DC误差。再次注意,最高速器件需要非RRO设计。此处显示的1SSBW增益通常超过真实的增益带宽积(GBP)。例如,最快的800MHz OPA820实际上显示了240MHz的数据手册GBP。这又是由于LG单位增益交越处的相位裕度<65°,大大增加了闭环带宽。

为了简化单通道VFA表,下面的筛选条件将被遵循:

1. 压摆率>400V/μs

2. 最大Vio>1mV

3. 输入噪声电压>4nV/√Hz

4. 轨到轨输入(RRI)器件(在表4中出现)

5. 1k MSRP(制造商建议零售价)>3.00美元

6. 过时的器件

表1:单位增益稳定、非压摆增强型、单通道VFA器件,按SSBW降序排列。

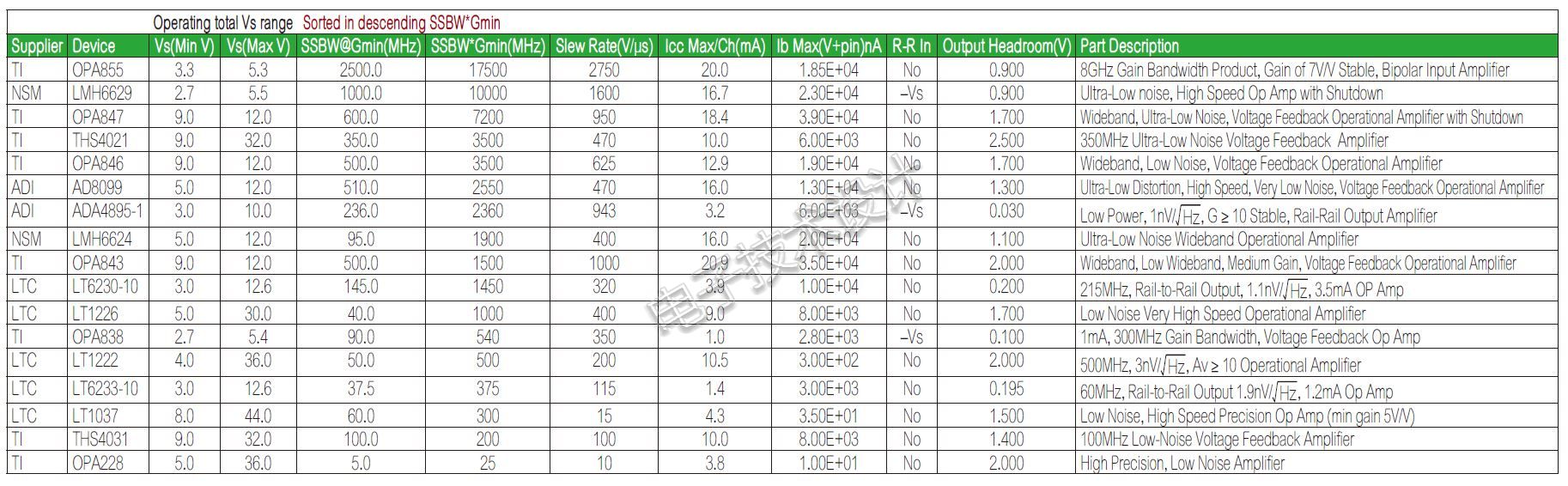

要提供具有较高压摆率的VFA解决方案,最常见的方法是解补偿运算放大器。这种方法限制了VFA在高增益(或跨阻抗)中的应用,但在给定的电源电流范围内可以提供非常好的DC精度,通常还有较低的输入电压噪声和较高的LSBW。虽然也有许多JFET或CMOS输入解补偿选择,但它们多数都具有较高的输入噪声或失调电压。为显示一些极低输入偏置电流解补偿选项,扩大了筛选条件:

1. 输入电压噪声>3.0nV/√Hz

2. 最大输入失调电压>2.5mV

3. 价格>4.00美元

4. 过时的器件

使用解补偿方法时压摆率通常较高,同时大多数器件也显示较低的输入电压噪声和失调电压。RRO或NRI器件相对较少,其中一个最新的器件(OPA838)还具有压摆增强输入级、极低功耗及低噪声。一般来说,这种器件提供极低的输入失调电流,允许使用输入偏置电流消除技术。SSBW x Gmin降序排列远超每个器件的实际GBP,因为最小工作闭环增益具有较低的相位裕度,扩大了最小建议闭环增益处的闭环带宽。Gmin是建议的最小增益。通常设置为达到安全的最小相位裕量,在30°~45°之间。Gmin通常会使非反相SSBW达到峰值,但不会不稳定。因此,“最小稳定增益”有点用词不当,“最小工作增益”更准确。使用简单的补偿技术,解补偿VFA可在任何增益(包括衰减)下进行反相操作。

表2:解补偿高速、单通道VFA器件,按Gmin x *SSBW(@Gmin)降序排列。

要缩小单位增益稳定VFA运放SSBW和LSBW的差距,最早的方法是在跨导元件上使用一个匹配的输入缓冲级。这显示了VFA的一个外部反馈特性,但随后仿真了CFA压摆率,因为误差电压的增加会导致输入缓冲器之间电阻器中的转换电流增加。图1示出了一个早期的例子,图中标出了输入级和跨导元件。压摆限制开始时,输入误差电压增加,从而增加了通过电流镜到补偿电容(图1中的“C”)的充电电流。

图1:VFA输入级仿真CFA压摆增强。

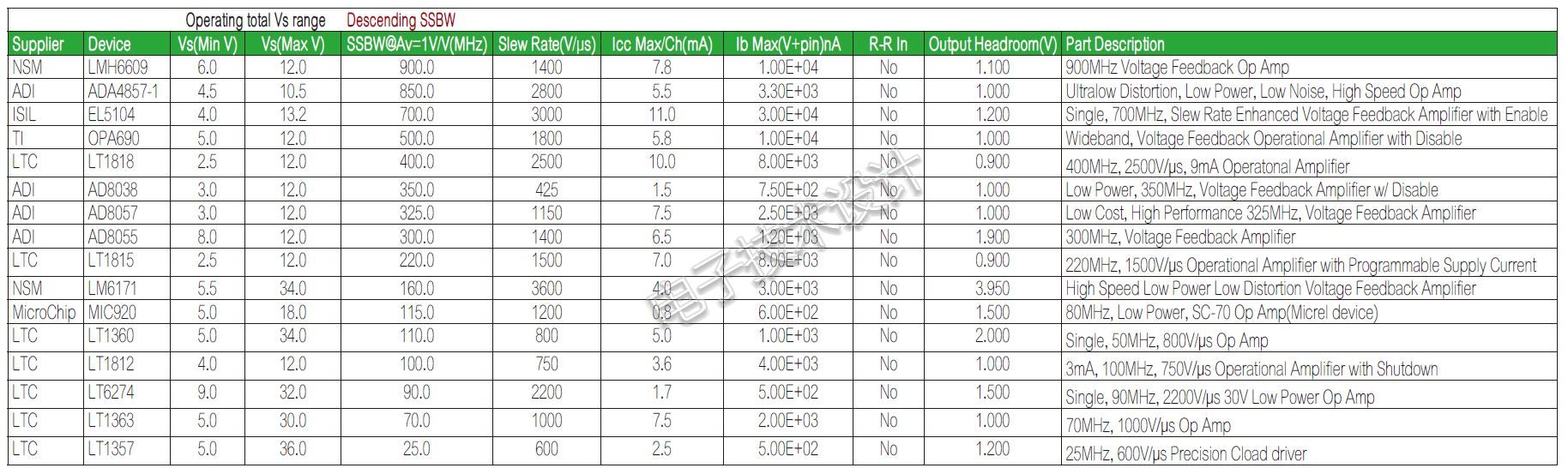

这种方法通常可由其所带的相对较高的输入电压噪声来识别。而且,由于输入缓冲器不是那么匹配,输入失调电压和电流通常要高些。没有失调电流漂移信息也是识别该拓扑结构的一个线索。类似于CFA放大器(使用类似的输入缓冲器),这种压摆增强方法通常带来较差的DC精度和非RRIO摆动性能。有些情况下很难识别这种拓扑结构(尽管LTC在其数据手册中为这种类型提供了图1)。表3尽可能地列出了与图1的设计类似的一系列单通道、单位增益稳定、极高压摆率的器件。尽管这些器件中有许多具有较高的输入噪声和失调电压,表3还是去掉了极值,包括排除在外的器件(没对输入失调电压进行筛选)。

1. En>12nV/√Hz

2. 1K MSRP>3.00美元

3. 非单位增益稳定的器件

4. 过时的器件

表3:单位增益稳定、极高压摆率、单通道VFA,以Gmin=1SSBW降序排列。

虽然这些器件基本上仿真了CFA类型的LSBW性能,但DC精度和噪声仍有很大的提升空间。此外,和所有CFA解决方案类似,它们都不支持输入端摆动到轨。

从大约2004年开始,高速VFA的开发找到了新的方法来按需提供压摆率,实现更好的失调和噪声性能。他们的目标是改善DC精度和噪声,同时在I/O引脚上实现摆动到轨的组合技术。目前尚不清楚其内部有多相似,但是在设计师的工具套件中填补这一空白已经取得了很大进展。而且,这些器件首先可以通过LSBW/Icc数值降序排列并寻找摆动到I/O轨的某种组合来识别(删掉表3中的器件)。表4中使用的简单数值是基于压摆率的2Vpp输出LSBW除以25C最大静态电源电流。但请记住,在测试频率增加并且压摆增强电路工作时,对压摆增强型运算放大器的各种LSBW测试都会显示出电源电流的快速增加。所有CFA以及此处描述的压摆增强型VFA器件都是如此。但是在任何压摆增强器件的数据手册中都难以找到这个指标。

早期提高极低功率器件压摆率的方法却导致了极高的噪声和失调电压。最新的方法在减少电源电流的情况下同时降低了输入噪声和失调电压。这里我们看到更多的RRO选择,主要是NRI。虽然表4中未显示,但这些“精密”VFA器件的输入失调电流和漂移通常都非常低。

有一些RRI选择,当输入共模处于输入切换到上级的操作范围时,压摆增强是否起作用还不清楚。LTC的RRI器件在反相配置中指定了压摆率,以保持输入工作电压固定在中间值附近。ADI的RRI器件压摆率规范要求+1的工作增益,但不会进入正电源以下1.3V的交叉区域。

为简化表4,滤除了以下内容:

1. En>6nV/√Hz

2. Vio>0.5mV

3. 1k建议零售价>3.00美元

4. 过时的器件

表4:精密、压摆增强型、单位增益稳定单通道VFA,按LSBW/Icc降序排列。

更高速的VFA一直在努力改善其全功率带宽,加入了与众多<20MHz精密运算放大器类似的I/O范围和DC精度特性。如果不需要RRIO,并且只需要适度的压摆率,表1中列出了一些非常节能的低噪声和低失调选择。如果您的应用可以从解补偿解决方案中受益,则会得到更高的压摆率和电源电流。表2的几个最新器件在非常低的静态电流下具有极低的噪声和失调。当VFA架构中需要CFA类型的压摆率时,这很容易得到,但都不会提供摆动到轨的能力。如表3所示,它们也同CFA一样具有较差的DC精度,和通常较高的输入电压噪声。表4中的最新产品改善了压摆率与静态功率,同时提供RRO和不同的摆动到轨输入选择。虽然它们的输入噪声通常不如表1中那么好,压摆率也远远比不上表3中的器件,却可以在较低的静态电流下扩展LSBW选择,并且有一些吸引人的选择。第四篇我们将继续讨论高速CFA和FDA的DC精度。

(原文刊登于ASPENCORE旗下Planet Analog英文网站,参考链接:DC precision considerations for high speed amplifiers, Insight #3。)

本文为《电子技术设计》2019年4月刊杂志文章。

最前沿的电子设计资讯

最前沿的电子设计资讯