从低密度的后通孔TSV 硅3D集成技术,到高密度的引线混合键合或3D VSLI CoolCubeTM解决方案,研究人员发现许多开发新产品的机会。本文概述了当前新兴的硅3D集成技术,讨论了图像传感器、光子器件、MEMS、Wide I/O存储器和布局先进逻辑电路的硅中介层,围绕3D平台性能评估,重点介绍硅3D封装的主要挑战和技术发展。

从最初为图像传感器设计的硅2.5D集成技术[1],到复杂的高密度的高性能3D系统,硅3D集成是在同一芯片上集成所有功能的系统芯片(SoC)之外的另一种支持各种类型的应用的解决方案,可用于创建性价比更高的系统。硅3D集成技术的主要优势:缩短互连线长度,降低R.C积,让先进系统芯片(SoC)能够垂直划分功能,进一步降低系统尺寸和外形因数[2]。

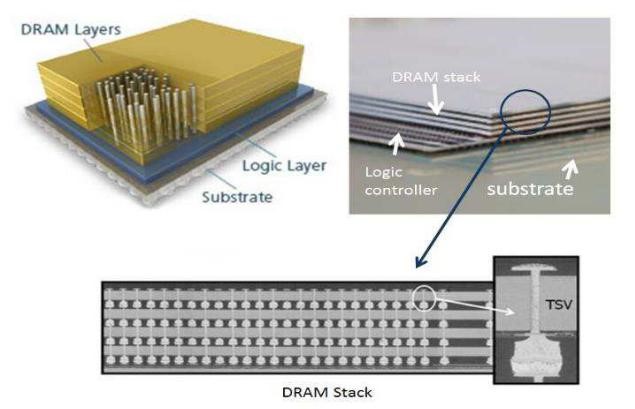

在首批出现的3D产品中,业界认为存储器层叠方案可以提高DRAM/逻辑控制器的容量/带宽,适用于高性能计算系统、图形处理器、服务器和微型服务器(图1)。

图1:与逻辑控制器相连的DRAM混合存储器层叠模块(HMC)(来源:美光)。

美光的混合存储器模块(HMC)[3]和海力士的宽带存储器(HBM)[4]开始进入量产阶段,这两个解决方案都连接硅中介层,面向高性能计算(HPC)应用。

Xilinx于2012年提出在硅中介层制造现场可编程门阵列(FPGA)的概念[5],该技术最初采用CoWoS集成工艺[6],引起供应链巨变,后来改用两个28nm FPGA和两个65nm混合信号芯片堆叠在65nm中介层上[7]。

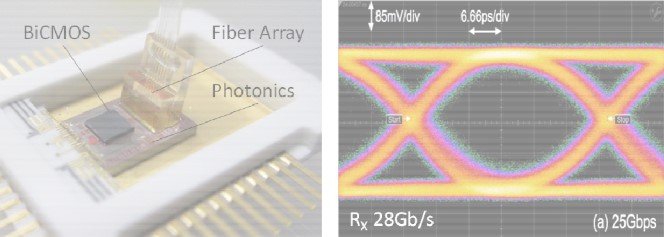

服务器对高带宽和低功耗的进一步需求催生了将CMOS/BiCMOS和光子功能分开[8]的每个通道传输速率高达25 Gb/s的硅光子器件平台(图2),以及产生了硅光中介层集成技术[9]。

图2左图:一个采用3D层叠技术在光子器件上安装BiCMOS器件的光学封装测试芯片;右图:该芯片在RX 25/28Gbps时的电眼测量图

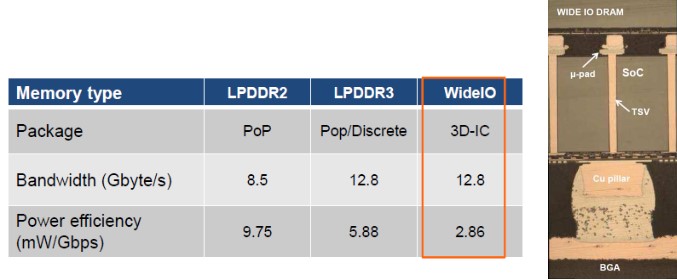

研究人员认为在逻辑层上堆叠存储层可以大幅降低存储器与处理器之间的接口功耗。堆叠在逻辑层上的Wide I/O DRAM(图3)的能效是LPDDR解决方案的四倍,并且在未来几年内传输速率将达到50 GB/s [10]。

图3:置于65nm逻辑层上的Wide IO存储器,顶层/底层具有1250个TSV互连线,1000个倒装片铜柱(底部/ BGA)。

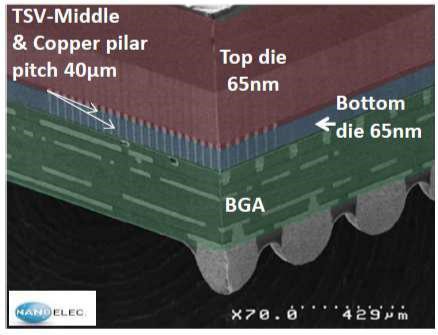

为了给高性能计算或电信应用提供高带宽性能,研究人员设计了一个基于异步3D Network-On-Chip架构的先进逻辑层叠方案,采用3D封装方法将两颗相同的逻辑裸片正反面层叠,证明了可扩展的同构3D层叠方法的技术优势。该3D集成方案的逻辑芯片采用CMOS 65nm制造工艺,使用宽高比为1:8 的TSV Middle通孔和40μm节距的铜柱连接芯片(图4)。

图4 :采用逻辑芯片层叠方法的异步Network-on-Chip 3D架构

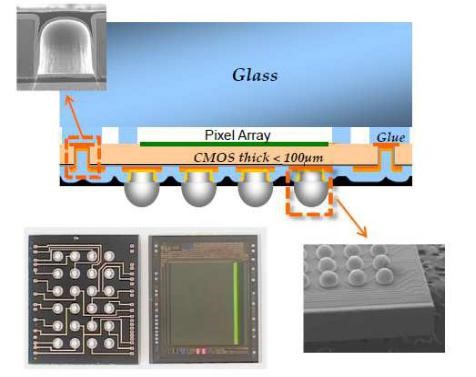

在2.5D TSV被引入CMOS图像传感器(图5)后,3D集成技术从2013年开始进入智能手机和平板电脑中[11-12],目前市场上存在多个不同的相互竞争的层叠技术,数字处理层可以布局在硅衬底上,而不是像素阵列电路上,通过功能划分和工序优化,图像传感器尺寸变得更加紧凑(图6)。

图5:晶圆级摄像头2.5D后通孔方法。

图6:索尼图像传感器[11]采用直接键合+ TSV的晶圆级层叠解决方案(来源:System Plus Consulting)。

图7:博世采用TSV 3D技术在ASIC中集成3轴加速度计(来源:Yole Developpement)。

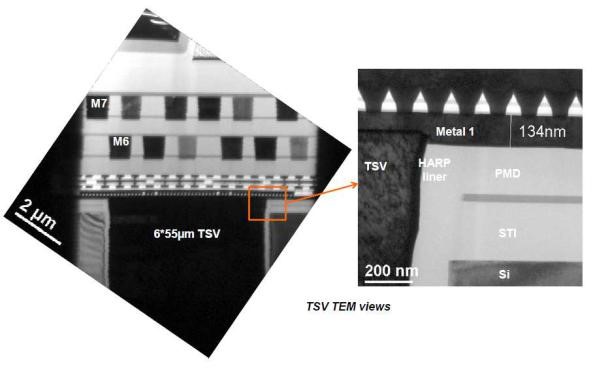

3D集成被广泛应用证明,TSV等先进技术节点的基本模块技术已经成熟(图8)。现在,研发重点转移到由市场需求驱动的新挑战上:封装应变管理;通过改进散热效率提高系统性能;提高芯片间的互连密度。

图8:6x55µm 28FDSOI Via Middle 集成TEM视图,对测试载具良率没有影响,通过了TDDB、EMG和TC测试

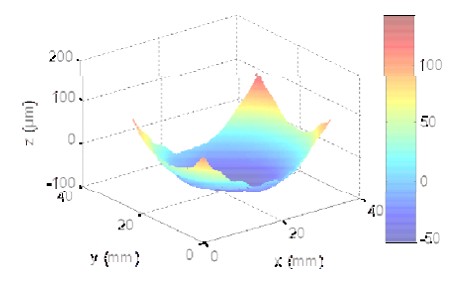

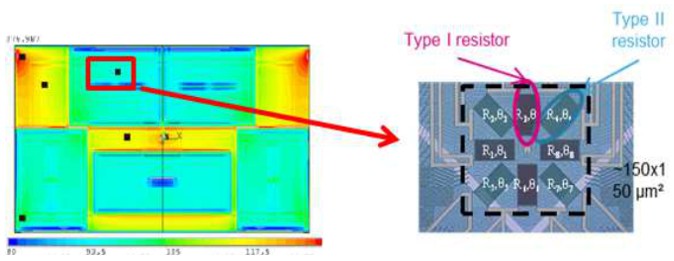

对于较大的硅中介层来说,热机械应变是一个需要考虑的难题,需要解决硅光子变化以及HBM/CPU集成封装问题,叠层之间的热膨胀系数(CTE)不匹配将会致使裸片翘曲[13]。根据裸片级曲率对温度的敏感性,研究人员开发出一种应变监测和翘曲补偿策略,通过综合使用阴影莫尔干涉仪(图9)、现场应力传感器和有限元建模(FEM)方法,创建了介电层特性模型。(图10) [14]

对于MEMS,微缩化是除成本和性能之外的另一个差异化要素。2007年以来,技术发展趋势是开发3D异构MEMS功能,包括通过TSV连接IC(图7)。

图9:使用ShadowMoiré干涉仪在室温下测量80 µm硅中介层的裸片级翘曲,测量结果有一个球面非线性翘曲。

图10:中介层机械应力场模拟(左图)和8片负应变传感器放置方式(右图)。

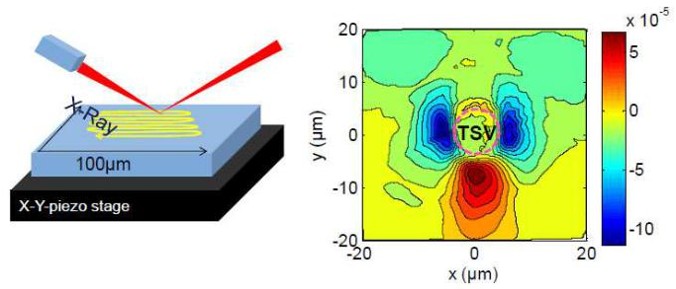

研究人员利用X射线衍射技术对TSV集成引起的局部应变进行了表征实验(图11)。同步辐射源纳米级聚焦X射线衍射测量图高亮显示了TSV周围应变的2D平面分布情况,并证明应变分布与3D FEM模拟相关。

图11:使用纳米聚焦X射线束衍射方法测量的TSV周围应变2D平面空间应变分布。稀化样品是在室温和原位退火过程中完成测量。

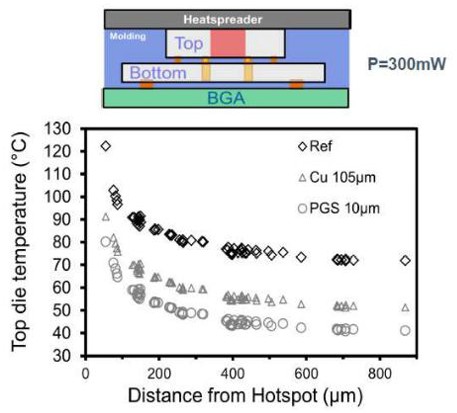

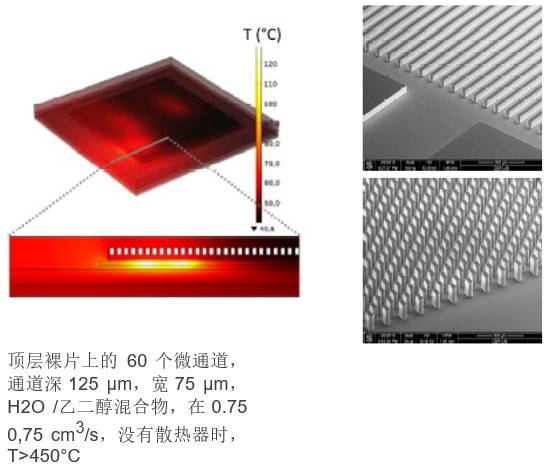

热管理是业界关注的影响3D性能的一个主要问题。精确的FEM模型[15]和在TSV 3D电路上校准的紧凑型热模型有益于设计流程改进[16],研究人员做过高导热率散热器材料的评测,这种材料可以提高封装的散热性能[17],耐受更大的耗散功耗,可以显著降低潜在的局部热点效应(图12),高性能冷却技术被证明具有嵌入式微流体 [18]特性(图13)。

图12:3D电路被动散热器评估:顶层裸片使用铜散热器与使用热解石墨薄板(PGS)散热器的温度原位测量对比(300mW热点)。

顶层裸片上的60个微通道,通道深125 µm,宽75 µm,H2O /乙二醇混合物,在0.75 0,75 cm3/s,没有散热器时,T>450°C

图13左图)在一个热点密集且密闭Wioming 3D 电路上的微流体冷却技术(2000 W /cm²)。右图)在Si中蚀刻的微通道和鳍引脚的SEM图像

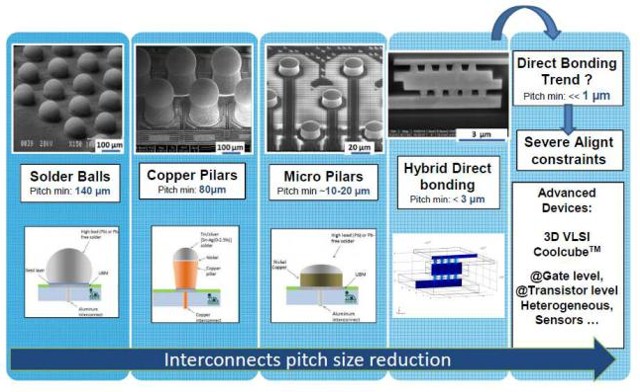

互连密度提高:混合引线键合工艺是一个前景很好的微凸点技术的替代方法,或者可以替代裸片互连使用的TSV直接氧化物键合方法(图14)。

图14:互连线间距随着新技术解决方案和机会的出现而发展变化。

混合键合工艺允许在后工序进行低节距的面对面的层叠,但也给集成和设计优化带来新挑战。

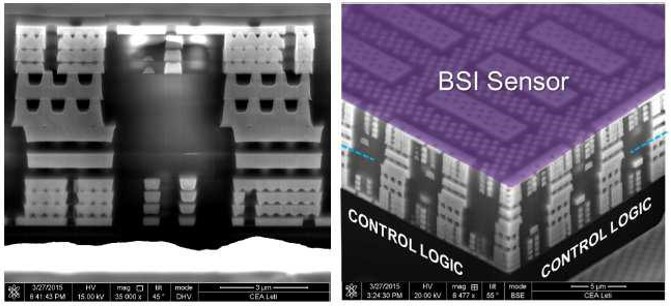

CEA-Leti [19]发布了一个集成背面照明(BSI)与控制逻辑单元的晶圆级混合键合封装,证明低节距(5µm至24µm)焊盘对准精度在400nm以下,并使用了2x6金属层0.13µm 双大马士革镶嵌工艺(图15)。

图15:混合键合封装的SEM图像(俯视图和3D视图),包括BSI成像器结构+逻辑的所有金属层。

为避开非键合区域,必须优化焊盘设计和表面抛光工序。套刻精度优于250 nm的高性能对准系统[20]能够实现最低7µm的高密度节距(图16)。

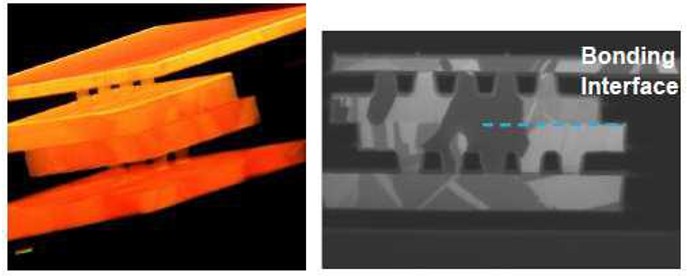

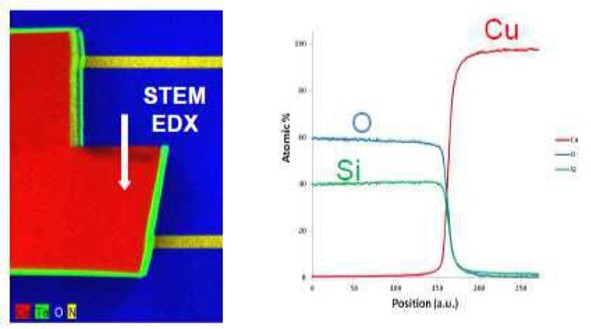

研究人员做了键合界面完整性表征实验,在附加的热应变实验后进行EDX分析,未在氧化层发现铜扩散现象(图17)。

图17:EDX混合键合界面表征,实验显示无铜通过界面扩散(在焊盘失准情况下)。

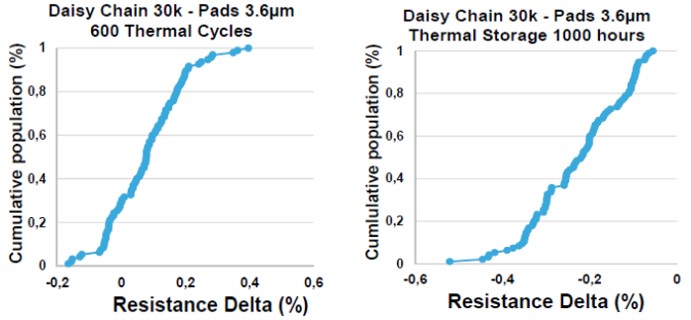

一份有关混合键合技术的电学表征实验和初步可靠性的研究报告[21]证明,在300mm层叠晶片上,良率达到100%,在30k菊花链时,界面电阻离差较低。储热循环实验(图18)结果证明,技术成熟的图像传感器专用混合键合工艺实现了低电阻离差(小于0.5%)(ST内部数据待发布)。

图18:混合键合可靠性实验结果。热循环(左图)和储热(右图)测试的电阻离差小于0.5%。

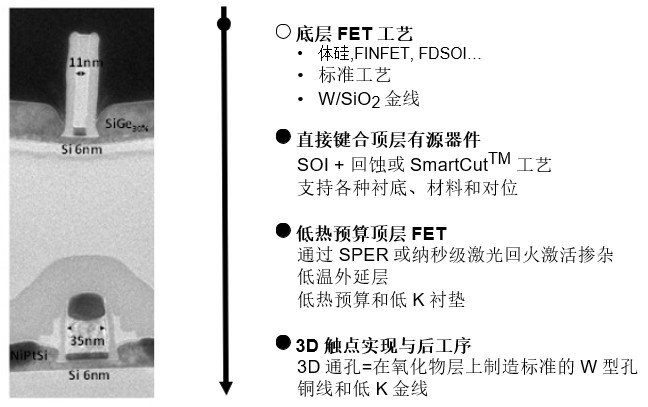

直接键合的趋势:研究人员可能会想出更先进的解决方案,例如,3D VLSI CoolCubeTM 集成[22],该方案利用独特的连接密度超过百万/平方毫米的通孔技术,可以垂直堆叠多层芯片,为异质集成带来新的机遇( 高微缩化的像素、CMOS与NEMS混合架构、III-V/Ge材料)和设计灵活性,特别适合于线长微缩或神经形态计算(图19)。

图19 - CoolCubeTM 原理

硅3D集成现已成为现实,是一个高性能的半导体集成创新解决方案,可以替代因光刻技术投资庞大而在未来十年内难以维持经济效益的标准“摩尔定律”。3D集成被选择背后的动因是性能、带宽、复杂性、互连密度,以及系统微缩化、最终成本和价值链。热管理、热机械应变和连接密度等难题都已有相应的解决办法。随着直接混合键合套刻精度提高,业界可能会想出创新的集成方法,替代现有的裸片层叠解决方案,简化产品价值链,开发出功能分区、高密度互连的高性能器件。

最前沿的电子设计资讯

最前沿的电子设计资讯