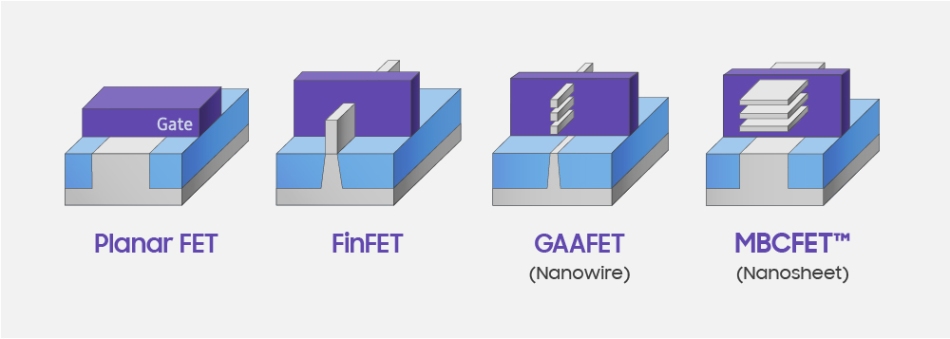

日前,高通在2022年的骁龙峰会上发布了骁龙8 Gen2平台,这一代CPU、GPU、AI等架构大幅升级,与此同时,高通也确认会继续使用三星的晶圆代工服务,而且他们最快会在两年上使用三星的GAA工艺,虽然没有明确表态,但高通的态度印证了也许将来会使用三星的3nm GAA工艺。那么所谓的GAA工艺又是什么呢?

GAA是Gate-All-Around的缩写,GAA即环绕式栅极工艺,该技术通过降低工作电压水平来提高能耗比,同时通过增加驱动电流增强芯片性能,从而突破FinFET(鳍式场效应晶体管)技术的性能限制。

就在今年6月末,三星宣布,其位于韩国的华城工厂开始生产3nm芯片,采用全新GAA架构晶体管技术。三星表示,与原来采用FinFET的5nm工艺相比,初代3nm GAA制程节点在功耗、性能和面积(PPA)方面有不同程度的改进,其面积减少了16%、性能提高23%、功耗降低45%。到了第二代3nm芯片,面积减少了35%、性能提高30%、功耗降低50%。

2014年是芯片制程的一个关键节点,Intel率先迈入了14nm工艺节点,可之后5年,Intel却一直在14nm节点停滞不前,只搞出14nm+、14nm++这样的工艺,迟迟无法突破到10nm。正常来说芯片制程工艺其实是指栅极的宽度,它的宽度为14nm,就表明这个芯片的制程为14nm,它的宽度为5nm,那么这个芯片的制程就是5nm。当栅极的宽度越窄,晶体管也就能够做得越小,晶体管越小,单位面积就能放下更多晶体管,芯片的性能就越强。

可是栅极宽度并不能做得无限窄,因为栅极变窄的同时,源极和漏极的距离也在变近,当距离近到一定程度时,就会发生彼此漏电的问题。当栅极宽度小于20nm的时候,漏电率就会急剧增加,这也是Intel迟迟无法继续突破的原因,传统的平面结构无法满足继续向下突破的需求。

这时候也就出现了我们的第一个关键技术FinFET,它的解决思路就是改造晶体管的结构,将源极和漏极做成像鳍片一样直立的样子,然后让栅极三面包围住鳍片,由于这种鳍片结构是立体的形态,所以也叫做 3D FinFET。这样的结构,栅极的宽度并没有改变,只是通过增加长度,来增加接触面积,进而提升对电流的控制。从原来的一个接触面,到现在的三个,这样哪怕栅极宽度在进一步缩小依然可以保持稳定的性能。

3D FinFET 技术凭借着优良的性能,一路伴随着半导体产业发展,走到今天的7nm、5nm时代。可是FinFET虽然可以改善电路控制并减少漏电流,缩短晶体管的栅极宽度,但是当栅极宽度进一步缩小,源极和漏极的距离还是会编近,栅极下方的氧化物也越薄,依旧会产生漏电,造成严重的发热问题。加之随着工艺微缩,单个晶体管上的鳍片数量变少,鳍片高度增加,到一定高度后,鳍片就很难在内部应力作用下保持直立了,FinFET 结构也就很难形成了。

我们今天的主角GAA技术也就登场了,GAAFET相当于3D FinFET的改良版,这项技术的晶体管栅极和漏极不再是鳍片的形态,而是变成了一根根 “小棍子”,垂直穿过栅极,这样,栅极就能实现对源极、漏极的四面包裹。相比之下,GAA可以实现四边充当电流通道,而FinFET则只有三边。GAA的这种设计可以解决原来鳍片间距缩小的问题,并且在很大程度上解决栅极间距缩小后带来问题,例如电容效应等,可以提供更佳的性能和更低的次临界摆幅。从技术迭代的角度来看,三星使用的这种GAA是更先进的技术,也是向5nm以下制程突破的关键技术。

晶体管结构变化 (数据源:Samsung Electronics)

不过,目前的GAA技术还不成熟,三星使用GAA技术制造的3nm芯片良品率徘徊在10%到20%之间,PPA也远不及预期。据Digitimes统计,三星3nm工艺的晶体管密度大约为170 MTr/m㎡(百万晶体管每平方毫米),与台积电5nm的晶体管密度173 MTr/m㎡差不多,这也许是为什么高通没有在这一代选择三星的技术的原因之一。

相较于三星的激进,台积电就显得保守很多了,他们明确的表示3nm节点上将会继续打磨FinFET技术,据相关人士预测,台积电可能要到2nm节点上才会采用GAA技术。当然了GAAFET本身的工艺制造难度就不低,即使是三星、台积电和Intel这些对FinFET技术非常熟悉的巨头,也需要进一步的打磨才能实现顺利的技术过渡。

最前沿的电子设计资讯

最前沿的电子设计资讯