随着人工智能(AI)的快速部署,AI系统级芯片(SoC)设计的重点一直着重于构建更智能、更快速、更便宜的器件,而忽略了更安全、更可靠和更具防护性。

美国国家安全专家Jason Matheny曾经强调这个议题的重要性。他说:“尽管政府和私人企业为人工智能系统的开发提供了充足的资金,但在实际开发时并未关注到持续变化的威胁形势。事实上,只有不到1%的资金用于安全性。”Matheny同时也是美国乔治敦大学安全与新兴技术中心(CSET)创始主任暨美国国家人工智能安全委员会委员。

在探讨如何以芯片级将安全性建构到AI SoC之前,先思考一下什么是人工智能系统。人工智能系统中一般包括三项要素:

例如,Nest恒温器能分析并学习用户的行为,从而设置用户最爱的温度。最终,它能预测到用户喜欢在晚上将温度调低10度,于是推理引擎就会在每天的同一时间向恒温器发送降低温度的命令。

人工智能系统面临的最大威胁分为两类:面向控制的攻击和面向数据的攻击。当攻击者利用常见的软件漏洞——如缓冲区溢出,并接管系统时,就会发生面向控制的攻击。顾名思义,面向控制的攻击会控制人工智能设备,以执行攻击者的命令。无论是导出私人数据或者是更危险的事情,例如迫使自动驾驶车撞向高速公路上的护栏等。

而在面向数据的攻击中,攻击者会操纵人工智能系统的训练数据或系统中用于进行决策的现实世界数据,导致人工智能设备故障,并根据错误数据指示做出不应该的事情。这可能是无害的,如同破坏垃圾邮件过滤器使其带有恶意或导致自动驾驶车辆无法识别停车标志一样。

SoC设计人员可以在设计时结合内置于CPU架构中的安全功能,然后在CPU周围添加硬件和软件层,这将有助于使其更接近在其基本结构中内置安全的设计。

那么,SoC设计人员如何在其设计中利用这种功能呢?第一步是选择可预测常见安全攻击形式的CPU架构,例如以安全性为考虑而建构的最新一代RISC-V开源指令集架构(ISA)。接下来,添加监督硅知识产权(IP)和软件,使其可在威胁到达CPU硬件之前先进行查找问题。

RISC-V架构是在人工智能时代和当今具安全意识的世界中开发而来的。由于该架构开放公众监督和工程社群,采用这一开源架构应该不至于有任何意外。

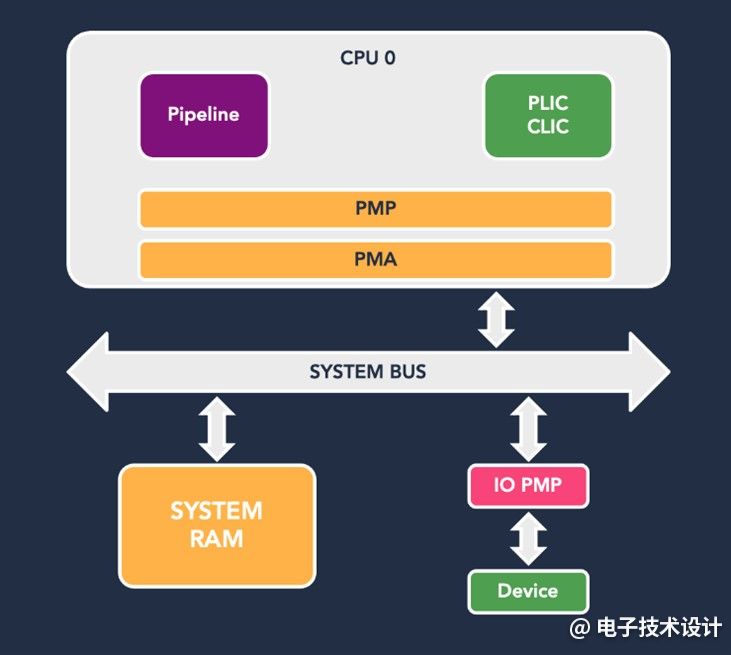

此外,RISC-V还提供了具有不同授权级和访问权限的操作模式。第一种是机器模式(M-Mode),其中软件可以完全访问机器资源。在建立信任根后开机时,机器进入用户模式以执行用户程序。在用户模式下,使用控制中断和异常分配来限制CPU的访问。两个额外的RISC-V安全架构特性是:(1)物理内存保护(PMP),(2)物理内存属性(PMA)。这些特性让设计人员指定哪些应用程序可以访问内存及其如何访问。

图1:内置RISC-V安全性。

商用的RISC-V IP供应商为设计人员添加了可选择实施于其设计中的附加功能。例如,晶心科技(Andes Technology)增加了堆栈溢出保护机制。为了实现此功能,设计人员决定堆栈其应用程序正常运行所需的最大程序。例如,假设应用程序需要不超过15个项目。当应用程序在现场执行时,如果检测到堆栈溢出,CPU将会产生异常。异常可能是由正常事件或恶意攻击引起的。无论是哪一种情况,异常处理软件都能够确定罪魁祸首。

另一个安全附加组件是可编程的内存属性,它让设计人员能够将内存区域分配为只读、只写或不受限制地访问。此外,设计人员可以选择隐藏包含应用关键数据的内存区域。如果发生任何试图访问该区域的情况,则会产生一个异常以评估哪个功能试图未经授权破坏该区域。晶心科技添加的第三个附加功能是隐藏程序代码使其不被反汇编和反向工程的能力。

启用RISC-V ISA中可用的更安全功能是添加自定义扩展的能力。例如,创建自定义指令以加速加密算法的执行。这些自定义指令可以对数据进行加扰和解密,任何不熟悉该指令的人都很难在没有专业知识的情况下进行黑客攻击。另一个安全功能是创建与主系统内存隔离的专用内存存储,只能由设计人员的应用软件访问。

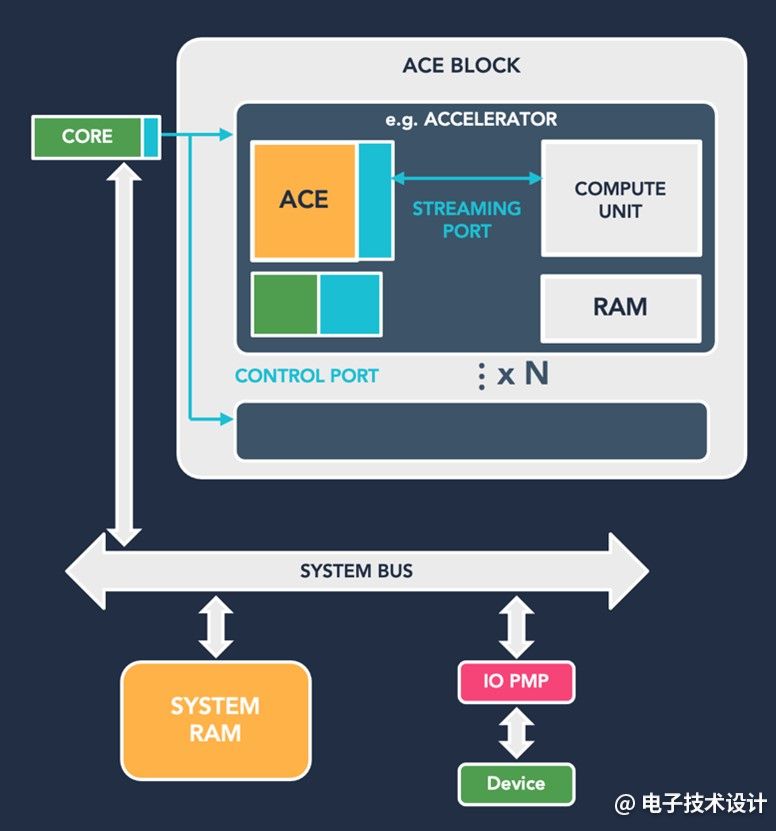

最后,创建用于访问协处理器、加密处理器和私有内存的专用总线,为RISC-V ISA增加了另一个层级的安全性。这种私有访问使最重要的数据远离系统总线和任何寻求进行秘密入侵的应用程序。晶心科技通过其Andes Custom Extensions (ACE)工具,简化了向RISC-V ISA添加自定义扩展和安全元素的任务。ACE大幅减少了制作和验证这些附加功能所需的时间。

图2:Andes Custom Extensions (ACE)自定义扩展工具。

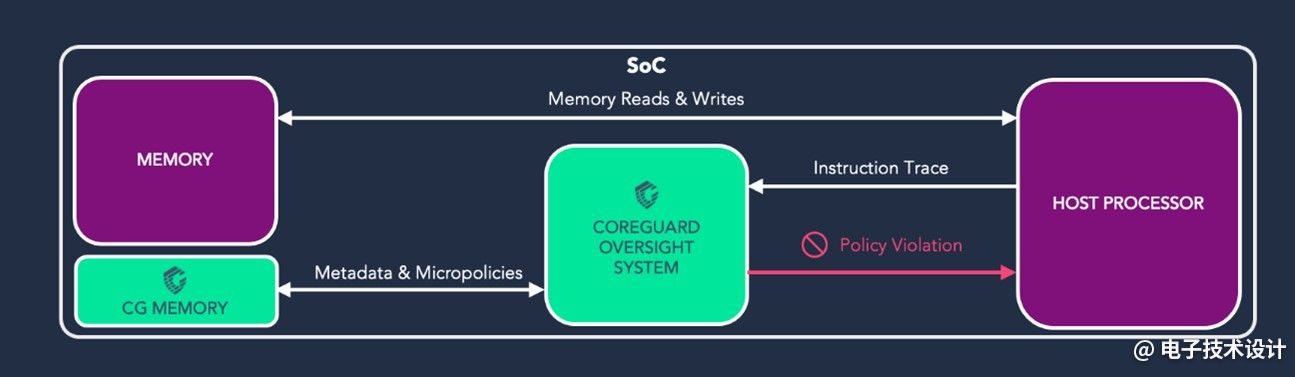

除了结合RISC-V ISA中固有的安全功能,以及上述Andes提供的附加功能外,Dover Microsystems的CoreGuard则围绕RISC-V CPU添加了一个监督系统。它就像是主机RISC-V处理器的保镖,监控执行的每条指令并防止利用软件漏洞。CoreGuard解决方案包括硬件和软件组件,硬件组件是与主机RISC-V内核集成的监督硅IP。驻留在硬件中使其在网络上无懈可击,并以硬件速度运作以提供实时执行。

该解决方案的软件方面包括两个部分。首先是一套微观政策(micropolicy),定义了安全、防护和隐私规则。第二个是元数据(metadata),即受微观政策保护的软件应用程序相关信息。在操作中,主机RISC-V处理器从内存中读取需要处理的指令和数据,并将指令追踪发送到监督硬件。硬件采用动态的微观政策集,以及每个微观政策做出决定所需的所有相关元数据。如果指令不违反微观政策,则执行该指令。然而,如果违反了微观政策,则会将违规发回主机作为异常处理。

图3:CoreGuard方块图。

除了能在造成任何损害之前阻止攻击,安全解决方案还为主机RISC-V处理器提供了任何试图执行非法操作的精确恶意指令相关信息。

然后,主机可以根据该信息采取各种行动。默认操作将会终止应用程序的分段错误——但是,这通常不是生产选项。其他选项包括要求用户输入、启动地址空间布局随机化(ASLR)以争取时间,或让单独的“安全”应用程序接管。

例如,如果攻击者试图利用包裹递送无人机导航软件中的漏洞,将所有的包裹重新安排路径并递送到另一个位置。当检测到违反微观政策时,可以从受保护的储存空间中取出一个安全位置,然后指示无人机飞回该安全位置。

为了说明此安全解决方案如何阻止控制导向的攻击,让我们以自动驾驶车为例。如果攻击者成功利用硬件对策未检测到在CPU中的缓冲区溢出漏洞,并尝试注入程序代码以完全控制车辆,则CoreGuard的微观政策——Heap,就会阻止所有缓冲区溢出攻击,包括零日威胁,因而也关闭攻击者进入路径的门。

在2015年进行的一次安全测试就属于这种类型的攻击。当时研究人员成功控制了一辆吉普车,包括控制从音量到刹车和转向的一切。在采用CoreGuard保护的自动驾驶车中,它可以通知驾驶人关闭自动驾驶模式并接管车辆控制。

而在数据导向的攻击中,攻击者的目标是访问执行人工智能推理引擎的应用程序,并修改其传感器数据,从而导致系统出现故障。使用人工智能的一个常见应用是预测性维护,以预测机器或飞机何时需要维护。在跨多个产业中均采用了人工智能来预测各种事情,从飞机上的机械问题到预测食品生产设施中的工业冰箱何时需要维护等。

预测性维护应用取决于高质量、准确的数据读数。如果攻击者操纵了这些数据读数,人工智能系统将无法取得清晰或准确的图片来进行预测。例如,这可能意味着无法注意到需要维护的飞机,致使它可能在飞行途中发生故障。

在签核之前和签核验证过程之后,为人工智能系统提供动力的数据最容易受到攻击。如果攻击者可以拦截和更改该数据,则人工智能系统可能会受到严重损害。CoreGuard可以使用数据完整性微观政策,确保数据的真实性。该微观政策可防止在数字签名认证和人工智能系统之间修改数据,确保仅将可信赖且安全的数据输入系统。

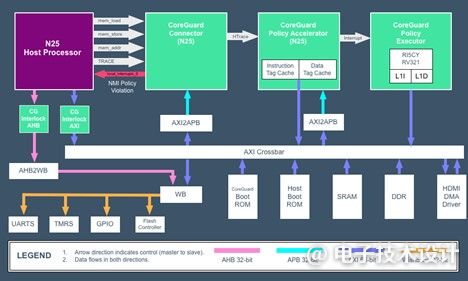

图4中说明了这如何将安全性内置于设计中,而不是在事后才添加。在此示例中,CoreGuard解决方案与Andes N25 RISC-V主机处理器集进行集成。这项集成包括识别通知CoreGuard互锁有关指令执行的信号:加载、储存,以及从数据存储器访问流水线阶段提取的数据地址。接下来,集成的SoC设计用于硬件仿真。其结果成功地执行一项示例应用,以实现所有CoreGuard互锁路径,从而证明了集成N25 RISC-V处理器与CoreGuard的可行性。

图4:N25 RISC-V处理器与CoreGuard集成的可行性证明。

许多方法都可用于确保SoC的安全性。本文介绍的是使用内置于RISC-V架构中的固有特性以及附加扩展,如何有助于展开确保CPU安全的过程。接着,本文说明为芯片级安全性另外增加一个分层,能够保护数据流以及SoC中不同组件之间的互动。确保安全并不至于困难,但确实需要规划。

(原文刊登于EDN姊妹网站Embedded,参考链接:Building security into an AI SoC using CPU features with extensions,由Susan Hong编译。)

最前沿的电子设计资讯

最前沿的电子设计资讯