据EDN美国版报道,在今夏公布其与美国麻省理工学院(MIT)和国立台湾大学(NTU)合作的结果后,台积电据传正计划在桃园打造1nm晶圆厂。报导中指称,新的1nm芯片生产设施将落脚桃园龙潭科学园区,台积电至今已在该科学园区经营两座半导体封测厂。

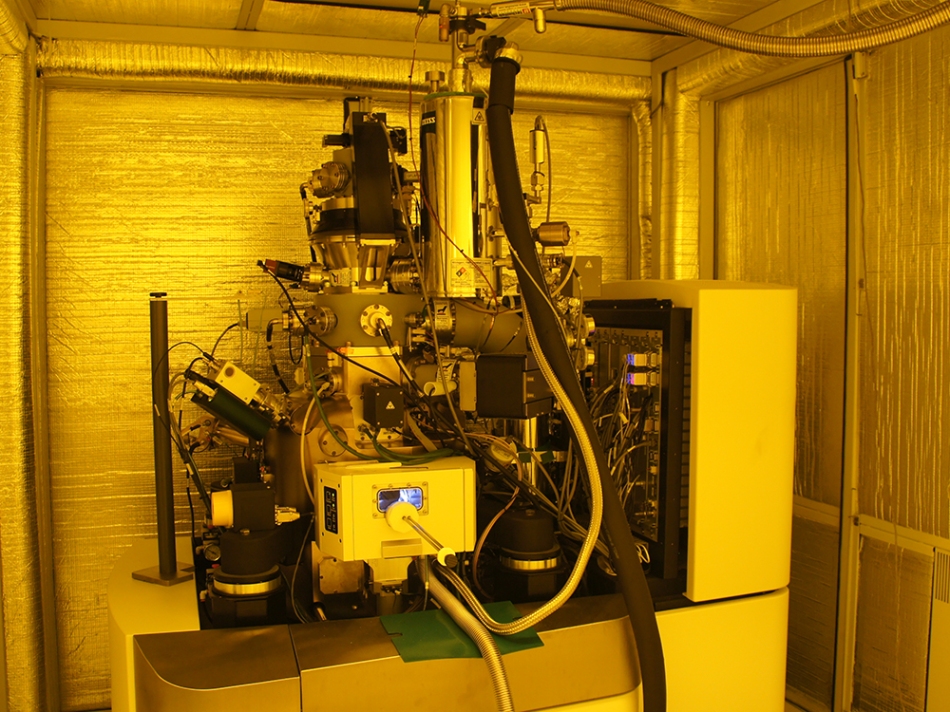

图1:MIT、台湾大学和台积电的研究人员发现,2D材料与半金属铋(Bi)相结合可达到极低的电阻,克服实现1nm芯片的挑战。(数据源:NTU)

这家全球最大的纯晶圆代工厂近来频频跃上新闻版面。

除了该公司的3nm芯片将于今年第四季进入量产,台积电3nm制程节点的升级版—N3E也宣称将在2023年下半年开始商用化生产。接下来,到2025年时在其位于新竹的宝山厂量产2nm芯片也备受期待。而相较于其3nm芯片,预计台积电的2nm芯片处理速度可望提高10%至15%,同时功耗也可望降低25%至30%。

根据一项来自台积电的消息来源指出,超越3nm制节点以上的先进制造技术目前正处于“探路”(pathfinding)阶段。然而,台积电在1nm技术取得突破这一事实则是一大关键进展。

随着半导体制程技术持续微缩,日益增加触点的电阻,因此,台积电和其他大型晶圆厂正致力于寻找具有极低电阻、可传输大电流且能用于量产的触点材料。今年5月,台积电宣布与MIT和NTU合作开发1nm制程节点的关键特性,但稍早也曾为此澄清说,这些突破性进展并不一定能很快地用于商业化芯片生产。

在MIT、台湾大学和台积电共同发表的研究论文中描述了由金属诱导导电间隙而引发的制造挑战,以及单层技术如何受到这些金属诱导间隙的影响。此外,文中并建议采用后过渡金属铋和半导体单层过渡金属二硫属化物以缩减间隙的尺寸,从而生产出比以往更小尺寸的2D晶体管。

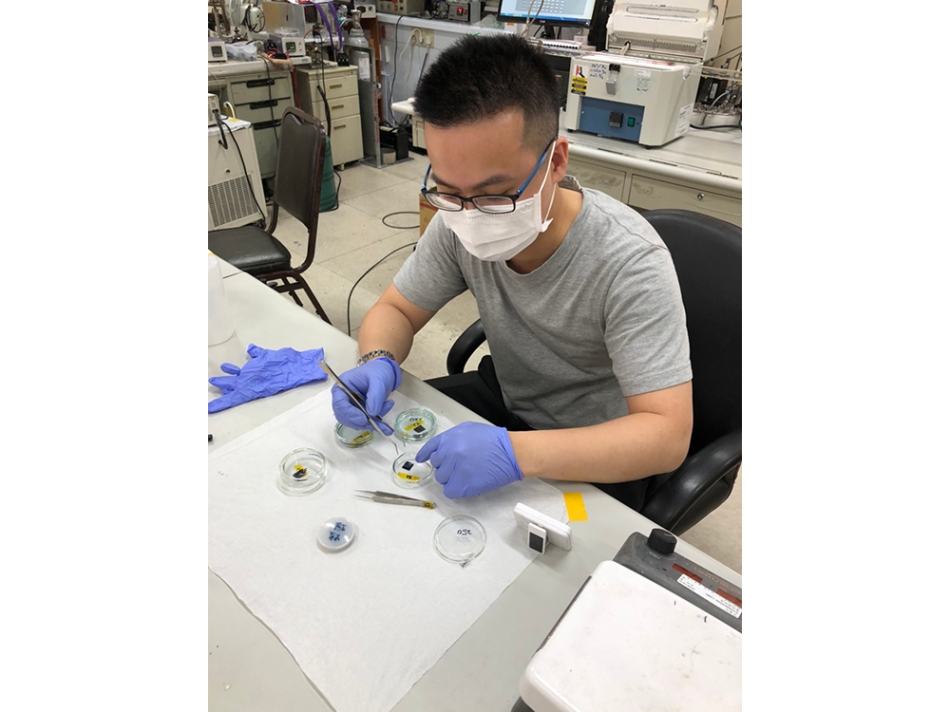

图2:结合半金属铋电极与2D材料,有助于显着降低触点的电阻并增加电流传导。(数据源:NTU)

这项突破涉及一系列新材料,使其可在芯片中创建单层或2D晶体管,从而透过与层数匹配的因子来微缩整体密度。台积电和MIT的团队已经采用包括二硫化钼(MoS2)、二硫化钨(WS2)和二硒化钨(WSe2)等各种现有半导体材料,展现其所实现的低触点电阻。

总之,使用非晶硅材料有助于实现非常小的晶体管——小至1nm。然而,正如台积电研究人员坦言,在未来几年内还不太可能导入使用于1nm制程节点。然而,为了实现1nm制程几何结构寻找合适晶体管结构与材料的任务本身已是一项令人振奋的进展。

(原文方式标语ASPENCORE旗下EDN美国版,参考链接:TSMC approaching 1 nm with 2D materials breakthrough,编译:Susan Hong)

最前沿的电子设计资讯

最前沿的电子设计资讯