日前,英特尔在IEDM上展示多项与半导体制造技术相关的研究成果:3D封装技术的新进展,可将密度再提升10倍;超越RibbonFET,用于2D晶体管微缩的新材料,包括仅三个原子厚的超薄材料;能效和存储的新可能,以实现更高性能的计算;量子计算的新进展。此外,英特尔表示,目标是在2030 年实现在单个封装中集成一万亿个晶体管。

根据组件研究小组主管兼高级首席工程师Paul Fischer的说法,组件研究团队目前专注于三个关键领域的创新进展,以实现摩尔定律的延续:一个是“用于小芯片平滑集成的3D混合键合(hybrid bonding)封装技术”,另一个是“使用超薄2D材料作为通道的高密度晶体管技术”,第三个是“提高性能的能效与存储器升级技术”。

硅芯片堆叠的连接密度增加 10 倍

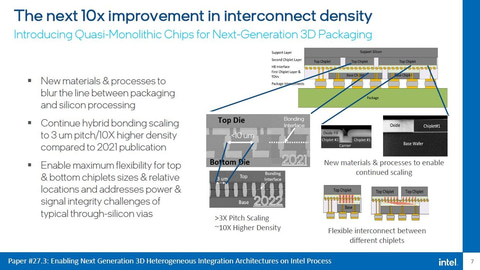

首先是“集成小芯片的3D混合键合(hybrid bonding)封装技术”的研究成果。这是近来备受关注的小芯片三D异构集成技术的成果。

用于堆叠和电连接形成小芯片的硅管芯(微型管芯)的技术可大致分为两种类型:微凸点连接和混合键合。Hybrid bonding是一种理论上可以缩短连接间距,换而言之,可增加连接密度(面积密度)的技术。

通过改进混合键合技术,英特尔将连接间距从 2021 年的不足10微米缩短至3微米,不足三分之一。当转换为连接密度,它高出 10 倍,英特尔实现了与单片式系统级芯片(system-on-chip)连接相似的互连密度和带宽。此外,混合键合技术还支持多个小芯片直堆叠。

使用超薄2D材料作为通道的高密度晶体管技术

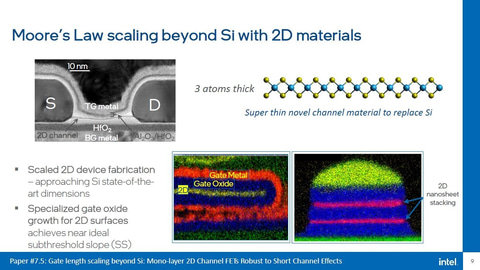

二维材料是指形成厚度仅为一层或三层原子层的薄平面的化合物。用于半导体器件研发的典型二维材料有过渡金属二硫化物(TMD)和石墨烯(一种碳原子平面时的结构)。

最近,以TMD为沟道的场效应晶体管(FET)的研究尤为活跃,被认为是实现亚纳米节点晶体管的强大基础技术。

英特尔展示该领域的两项研究成果。其中一个是“超越Si的栅极长度缩放:单层2D通道FET对短通道效应具有鲁棒性”为标题进行介绍。

大部分半导体材料——例如硅、氮化镓和碳化硅——都属于三维晶体,即原子会在3D空间上结合起来。而2D材料的特点,就是所有键合均在同一平面上完成。

英特尔展示了一种环栅(GAA)堆叠纳米片结构,采用典型的TMD 二碗化钼(MoS2)作为通道材料,并制作具有25nm短源漏距离的FET原型。具有顶栅和底栅的双栅FET的亚阈值斜率(SS)为75mV/dec,接近理想晶体管的亚阈值斜率。

此外,英特尔还在室温下以低漏电流在双栅极结构上实现了近完美的晶体管开关。英特尔表示,这两大成果正是堆叠GAA晶体管的实现基础,也将推动整个行业超越硅材料自身的天然限制。

他解释道,“在缩小晶体管尺寸方面,这些因素非常关键。通道厚度必须要跟X和Y轴成比例,也就是一缩就得俱缩。正因为如此,这些成果才对英特尔乃至整个半导体行业都极具吸引力。”

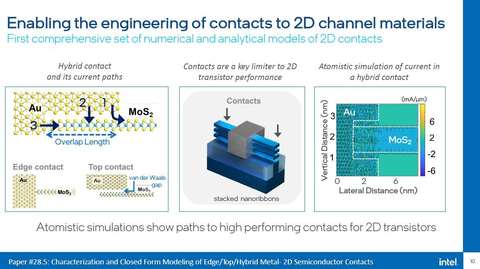

另一项研究成果以“边缘/顶部/混合金属-2D 半导体接触的表征和封闭形式建模”为题进行介绍。

2D材料为二硫化钼(MoS2),接触电极的金属为金(Au)。模拟了电阻如何根据横向重叠长度和垂直间隙长度而变化。

二维材料中的另一大挑战是实现电接触,如今的制程工艺已经让各元件间的距离小到极限。英特尔正在开发模型,希望探索二维材料电接触的相关物理学效应。研究人员创建了一个全面的二维材料电接触拓扑分析器,有望带来性能更高、可扩展性更强的晶体管通道。

为了提升能效和存储器,英特尔在两年之前发布了3D堆叠铁电存储器的概念。

Fischer表示,“我们坚信这项技术具有可行性。铁电材料具有一种独特属性,就是其电荷是固定的。我们实际可以在沟槽或通孔中创建多个不同的、可以单独识别的可寻址电容。这其实代表着新的密度提升空间,相当于单一元件可以充当四个存储元件。这是个令人兴奋的概念,只是原理说起来简单,但要拿出能够展示的实例却很困难。”

堆叠四个铁电电容器的高密度 FeRAM 单元技术

在第三个主题“面向高性能计算(HPC)的高能效技术和存储技术”的研究中,英特尔展示了四项成果。前两个是“铁电存储器”,下一个是“功率晶体管”,最后一个是“超低功耗数字电路”。

其堆叠铁电电容与传统铁电沟槽电容具有相同性能,并可用于在逻辑芯片之上构建FeRAM。

研究人员还开发出一个元件级模型,通过显示价态和空位缺陷的混合相来改进铁电氧化铪元件,这有望衍生出新的存储器和铁电晶体管。

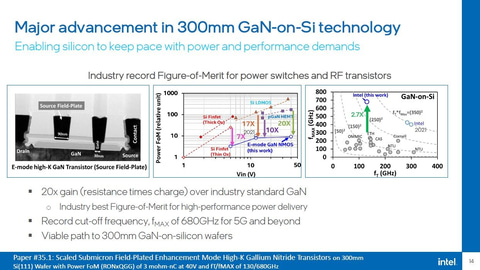

英特尔正在为打造300毫米硅基氮化镓晶圆(GaN-on-silicon wafers)开辟一条可行的路径,从而让世界离超越5G和电源能效问题的解决更进一步。英特尔在这一领域所取得的突破,实现了比行业标准高20倍的增益,并在高性能供电指标上打破了行业记录。

在“功率晶体管”中,“300mm Si(111)晶圆上的缩放亚微米场镀增强模式高 K 氮化镓晶体管,功率 FoM(RONxQGG)为3.1 mohm-nC,40V和fT/fMAX为130/680GHz”的标题下介绍氮化镓(GaN)高频功率晶体管的研究成果。

英特尔在直径为 300mm 的硅晶圆上制作了短栅极长度为 30nm 的增强型n 沟道 GaN MOS FET, 并实现了 680GHz 的最高工作频率(fMAX)。

过渡频率(fT)为 130GHz。作为功率器件品质因数的功率FoM(导通电阻×栅极电荷)低至3.1mS2-nC(外加电压40V,栅极电压OV)(指数越低,性能更高)。

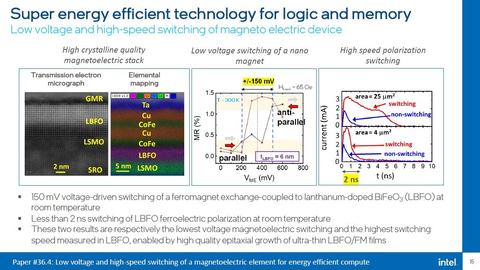

磁电效应是指当在晶体(块状或薄膜)上施加磁场时,晶体会在同一方向极化,而当在晶体上施加电场时,晶体会被磁化的现象同一方向。指发生的现象。即使在停止施加外部磁场(或外部电场)之后,产生的极化和磁化仍然存在。因此,一直期待在非易失性逻辑和非易失性存储器中的应用。

Fischer表示,由于开关半导体的物理特性,目前的设备大多在0.6伏电压上工作。组件研究小组则展示了一款磁电设备的低压与高速切换能力。

“研究人员使用掺了镧的氧化铁铋作为贫电材料。通过在其上施加电场,他们成功将磁矩转换到了材料上,并可在施加另一电势之前处于永磁状态。但只需施加150毫伏电压,即可完成恢复转换。这就是降低工作电压的绝佳机会,意味着激活切换的工作电压只需要150毫伏、而非目前常见的0.6伏。”

根据Fischer的解释,这一点之所以重要,是因为设备的功率与电压的平方成正比。另外,这些材料的高速切换能力也很关键。对于约4平方微米的较大元件,研究人员展示了在2纳秒内即可完成切换。

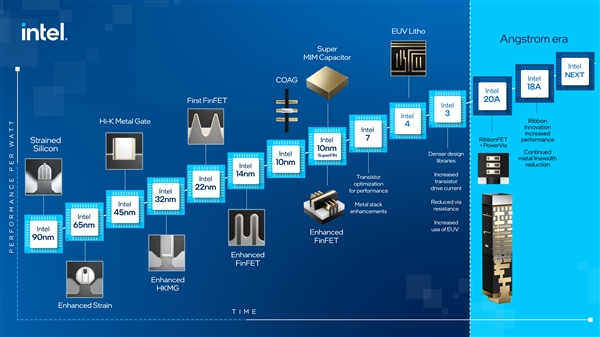

据英特尔最新对外公布的信息显示,Intel 4nm芯片已准备投产,它将用于包括Meteor Lake(14代酷睿流星湖)处理器、ASIC网络产品等。

同时,Intel 3nm、20A(2nm,其中A代表埃米,1nm=10埃米,下同)、18A(1.8nm)进展一切顺利,甚至还略有提前。

其中Intel 3nm将在明年下半年投产,用于Granite Rapids和Sierra Forest数据中心产品。

Intel制造工艺路线图

Intel制造工艺路线图

Intel封装技术路线图

Intel封装技术路线图

Intel 20A计划2024上半年准备投产,首发Arrow Lake(15代酷睿)客户端处理器,Intel 18A提前到2024下半年就绪,分别用在下一代酷睿和数据中心产品上。

综合来看,英特尔在设备技术研发上涉及的领域是非常广泛的。尽管在今年的IEDM上没有公布任何结果,但英特尔早期参与自旋转移磁存储器(STT-MRAM)、电阻变化存储器(ReRAM和硅光子技术的研发在半导体研发界颇有名气,我们期待在未来继续研究和开发。

最前沿的电子设计资讯

最前沿的电子设计资讯