随着时间的推移,PCIe取得了巨大的发展。从PCIe 1.0推出到现在的PCIe 6.0时代,其数据传输速率不断上升。特别是从PCIe 4.0到5.0到6.0,其数据传输速率增幅非常显著。分析其背后的原因,主要是数据爆炸式的增长,而这一增长又主要来源于人工智能以及机器学习所驱动的一系列应用。

不难发现,每次PCIe推出一个全新版本,其数据传输速率都比上一代基本实现了翻倍。比如PCIe 6.0和上一代的5.0,也就是64GT/s对32GT/s的双倍提升。

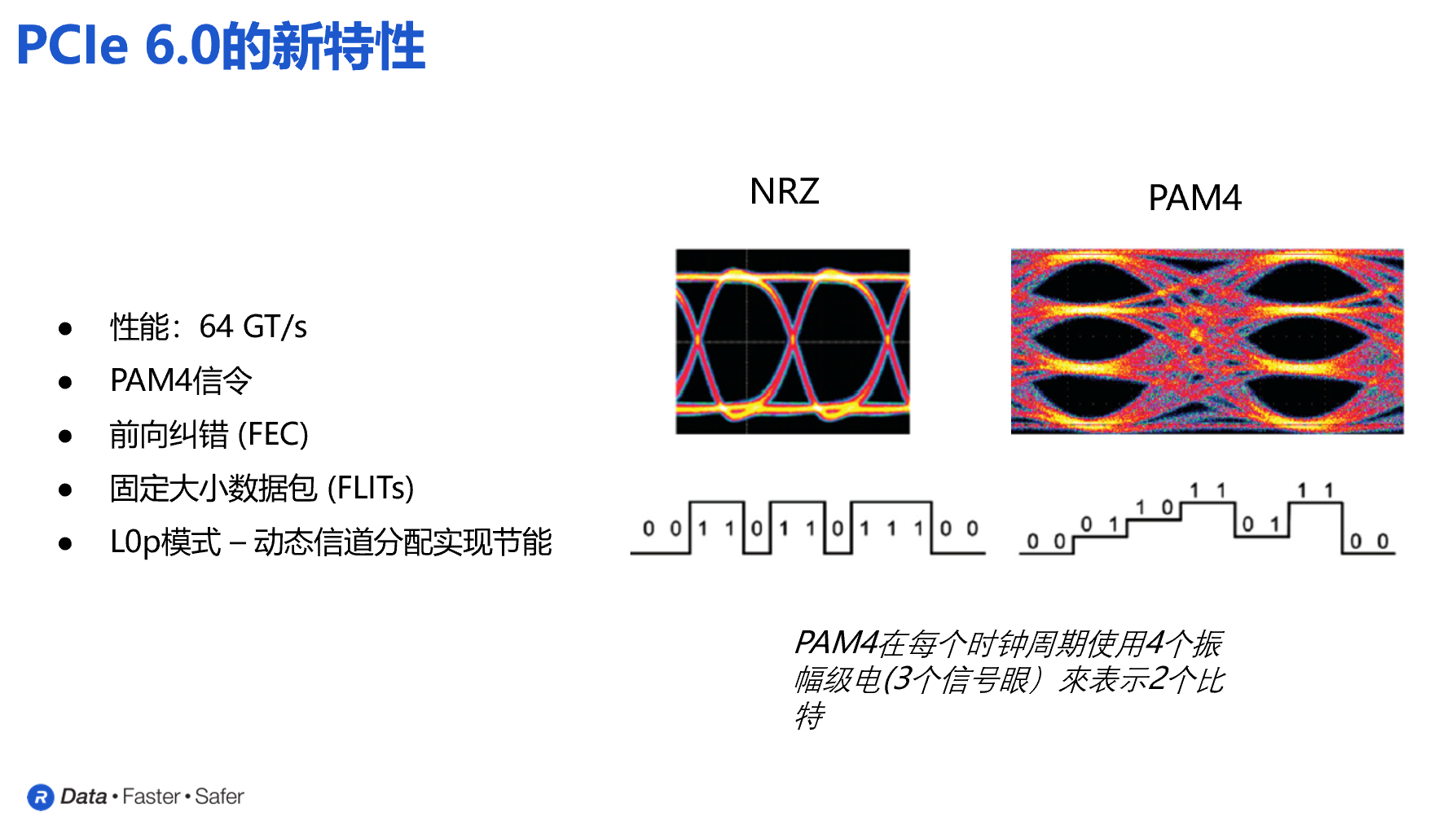

为了进一步满足PCIe 6.0达到64GT/s数据传输速率的需求,它的架构必须要重新优化和调整。同时,在整个电路和电路传输机制的配比上也存在着巨大的差异。这当中有一个最大的变化,就是从NRZ(不归零编码)到PAM4(四电平脉冲幅度调制)的转变。NRZ和PAM4有着非常明显的区别。在NRZ的制式下采用的是双电平模式,但是在PAM4则是升级到了四电平模式,而且它的传输速度达到了两个比特时钟周期,从PAM4的眼图上也可以看到它有三个眼。

由于采用了全新的PAM4信令,这也带来了PCIe 6.0时代两大非常重要的改变。

第一个改变是采用前向纠错,这就必须采用固定大小数据包(FLIT)作为支持。在此之前的PCIe版本中,则可以支持不同大小的数据包。

第二个改变是在PCIe 6.0当中采用了L0p模式。L0p模式的采纳可以让PCIe 6.0实现动态信道分配,从而更好地达到产品设备的节能。尽管在PCIe各代版本中都有一些选项可以将不使用的信道关闭,但是L0p模式可以更好地支持动态分配,从而更好地实现节能。

针对上述变化,Rambus公司也最新推出了PCIe 6.0接口子系统。在Rambus PCIe 6.0接口子系统发布暨媒体沟通会上,Rambus公司战略营销副总裁Matt Jones介绍了其相关内容。“该新品主要是针对高性能计算领域的具体应用,包括人工智能的SoC芯片。”Jones表示,“我们最新发布的PCIe 6.0有着非常重要的全新提升,包括数据传输速率可以达到64GT/s,同时支持全新的物理接口以及CXL 3.0。”

Rambus公司战略营销副总裁Matt Jones

据介绍,2022年年初,PCIe 6.0的规范和标准正式提出,在此基础之上,Rambus也推出了自己的控制器产品。现在,Rambus进一步扩展了其PCIe 6.0产品线,也即全集成的PCIe 6.0接口子系统,包括控制器以及PHY在内。

最新发布的PCIe 6.0 PHY支持CXL 3.0,其数据传输速率可达到64GT/s。同时,由于采用了PHY和控制器的全集成,其可以进一步降低延迟,更好地降低功耗,以及优化具体产品和芯片的占用面积。ASIC集成商,包括供应商,也无需额外的验证就可以直接将Rambus的产品应用在其产品设计中,通过这种方式就无需再去做额外的工作。

Rambus PCIe 6.0接口子系统也搭载了最先进的IDE安全引擎,也即在其控制器当中已实现了支持。随着数据传输速率越来越快,特别是在分布式计算场景之下进行数据的传输,也即在PCIe 6.0的环境之下,IDE的安全引擎可以保证数据传输的安全性。

最后,这一最新一代的PCIe 6.0产品,也对Rambus现有的非常成功的PCIe产品系列进行了补充,该系列已经有400多个成功的PCIe流片。

接下来,Jones介绍了Rambus支持CXL 3.0的PHY。“其实CXL 3.0最新的规范也是在2022年8月刚刚发布的。从它发布以来,到目前为止我们已经发现了一些早期的应用和未来的开发意向。作为CXL 3.0和PCIe 6.0,可以达到64GT/s的情况下,这两者之间也有着非常好的协同作用。我们可以帮助客户提供更加灵活的解决方案,除此之外,因为我们的PHY是可以同时支持PCIe 6.0和CXL 3.0,这也带来了更大程度上的优势。”Jones表示。

因此,作为PCIe 6.0子系统重要组成的PHY,将全面支持CXL 3.0版本下全部特性和相关功能。同时,也可以更好地支持闪存一致性,从而更好地推动数据中心的长期应用和发展。“我们期待着与我们的客户合作,利用CXL3.0解决方案,帮助实现数据中心向分布式可组合架构的变革。”他并表示。

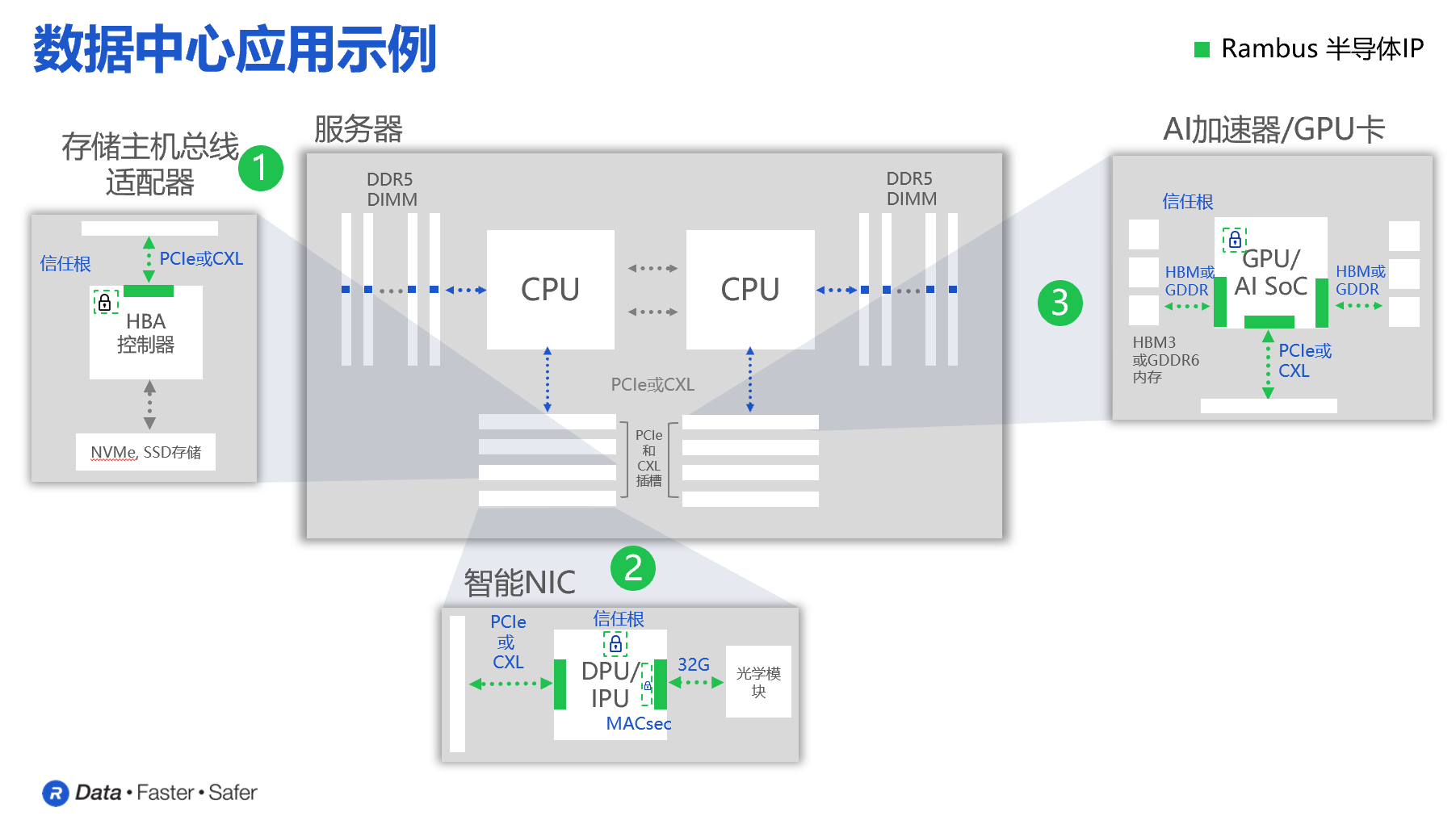

以下是Rambus在数据中心的PCIe 6.0接口子系统的应用案例。

在这三个例子中,每个示例都有一个存储主机总线适配器、一个智能网卡和一个AI加速器或GPU卡。可以看到,PCIe PHY和控制器的组合提供了一个成熟的接口,可以从服务器主板上的PCIe插槽和物理接口连接到控制器芯片上。这三个例子都保证了PCIe或CXL接口是经过硅验证的,并且不会增加设计复杂性。

更重要的是,PCIe 6.0的子系统也支持高性能内存,包括HBM、GDDR内存PHY和控制器,以及一流的安全解决方案,从而为系统设计人员提供全套IP。

PCIe 6.0解决方案可以同时支持三大非常关键的目标市场以及终端市场,分别是存储、智能网卡,以及加速器市场。

总的来讲,因为PCIe 6.0能够提供高带宽、低功耗以及低延迟互联,所以是数据中心以及很多其他数据应用的非常理想的解决方案。

可以看到,PCIe的应用场景越来越丰富,不管是芯片到芯片,还是网卡到网卡的连接。因此,Rambus推出的PCIe 6.0相关产品有着非常广泛的市场需求,不管是数据中心,还是在IoT、汽车,以及一些政府相关应用。

过去一段时间,数据量呈指数级的增长是加速新一代标准开发和推出的重要驱动力。目前为止,针对64GT/s PCIe 6.0的标准已经完成了制订。Rambus推出集成了控制器和PHY的PCIe 6.0内存接口子系统,主要就是面向SoC以及ASIC的开发者。“凭借行业领先的性能和来自Rambus的安全集成解决方案,我们正在通过创新真正使数据变得更快、更安全。”Jones总结说。

最前沿的电子设计资讯

最前沿的电子设计资讯