我需要用一个电路来限制某些耗散受限设备的电压。它必须将电压限制在最大1.5V,具有对称限制,能够接受2A的电流,并且在1V时漏电流小于100µA。

可以用两个串联的齐纳二极管,阳极到阳极,达到目的,但Vz=0.8V和2W耗散的齐纳二极管在市场上找不到。

我在网上搜索了可用的内容。在EDN美国版的设计实例(Design Ideas)网页中,我找到了一个[1],但是该电路不能限制低于2.5V的电压。在另一个设计实例[2]中,1.8V的最小电压对我的应用来说太高了,但是电流高达6A。另一个参考文献[3]使用单个器件将电压限制在1.5V,但其电阻约为1Ω,结合我对2A的要求会产生过高的电压。另一个电路[4]取决于用MOSFET的特性来设置限制电压,这在我的应用中不是一个选项,因为我必须要测试选择MOSFET才能找到可接受的限制电压。最后,参考文献5提供了一个完美的电压范围,最大电流为8A,但关断电流为200µA,这是我的限值的两倍。总之,我必须设计一个电路来满足我的需要。

您在设计电源时是否遇到过各种棘手的问题,想要获得原厂专家的帮助?3月30日,AspenCore将在上海举办国际集成电路展览会暨研讨会(IIC Shanghai 2023),同期举办的“第25届高效电源管理及宽禁带半导体技术应用论坛”邀请到国内外多家优秀的电源管理IC原厂,欢迎感兴趣的朋友点击这里报名参会并到场交流。

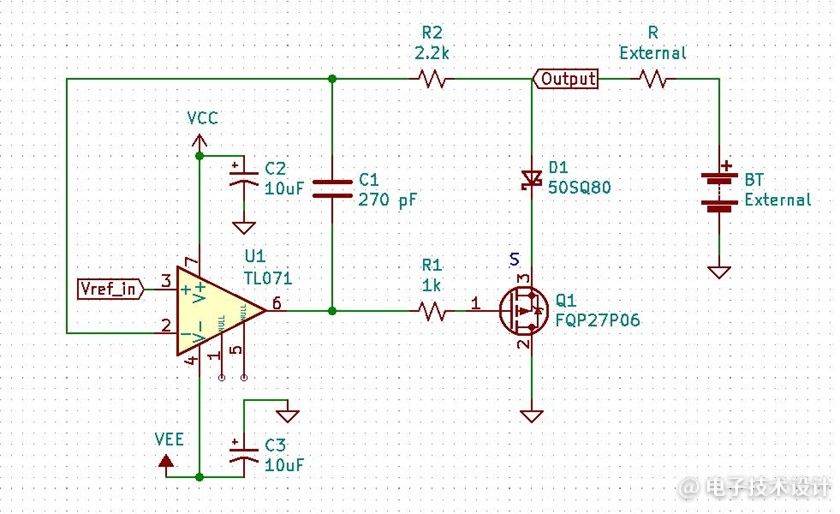

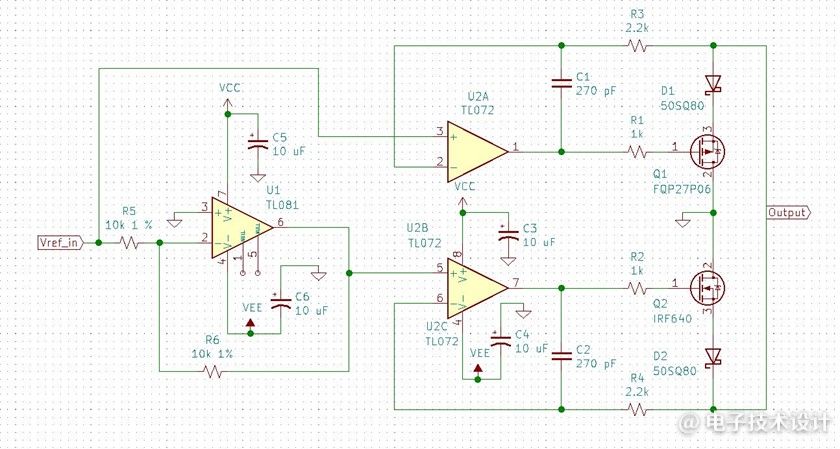

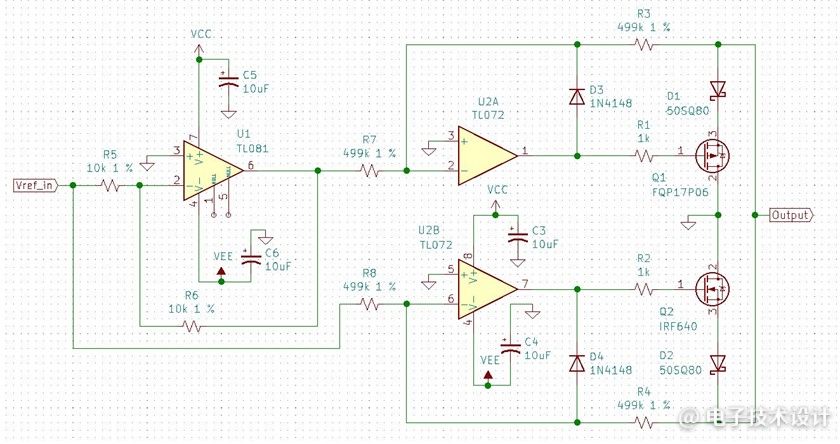

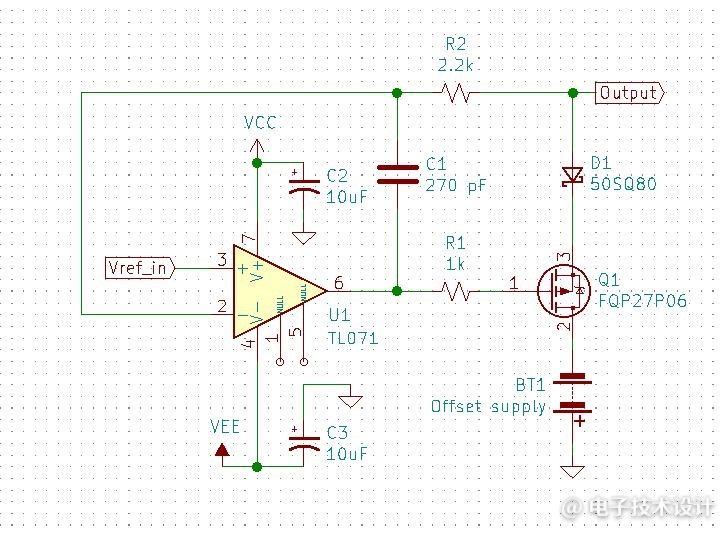

图1的电路具有所需的特性。它是一种改进的分流式稳压器。在此应用中,要调节的电压来自原理图中的外部电源电池BT。

图1:简单的正分流电压限制器的原理图。

假设原理图中的参考电压Vref_in为1.5V,电路输出端的电压也为1.5V。由于U1的两个输入相同,运算放大器输出为0V,MOSFET关闭,此时没有电流流过它。如果外部电压升高,运放输出将变得更负,并使Q1打开——这是一个P沟道MOSFET,用于源极跟随器配置——就会使更多电流流过D1和Q1。当电路处于限制状态时,输出端的阻抗大约等于二极管电阻加上Q1的RDS(on)除以U1的开环电压增益所得的总和。输出阻抗在数百毫欧范围内。电阻器R1是一个门限电阻器,用于消除MOSFET中振荡的风险。

当输出电压低于参考电压时,U1输出将上升为正,Q1将进入弱反相或亚阈值区域[6]。然后反馈回路打开,运放将饱和到它可以提供的最大正电压。如果输出端的电压变为负值,则二极管D1会阻止流过Q1体二极管的任何反向电流。当输出电压低于限制电压时,电路输出中所流过的电流是D1反向漏电流和U1输入偏置电流之和。

电阻器R2在出现负过压时将对U1提供保护,并能通过C1通过将运放的反相输入与输出隔离来使回路补偿生效。C1的值取决于运放、MOSFET和布局。

最大额定电流定义为使二极管和MOSFET两端的总压降等于参考电压的电流。公式是:

其中,VREF是参考电压(Vref_in),Vf是额定电流下D1两端的电压降,RDS(on)是MOSFET最大漏源电阻,Imax是源极可提供的最大电流。如果施加的电流大于Imax,则输出电压会从设定限值线性上升。如果施加的电流过高,D1或Q1会过载或过热,从而导致永久性故障。根据所使用的MOSFET,最大电流也可能受到运放最大输出电压的限制。

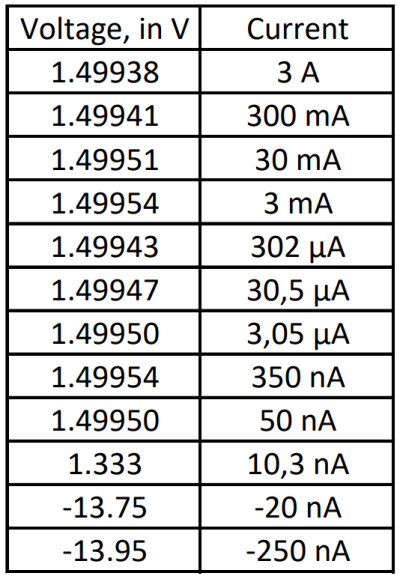

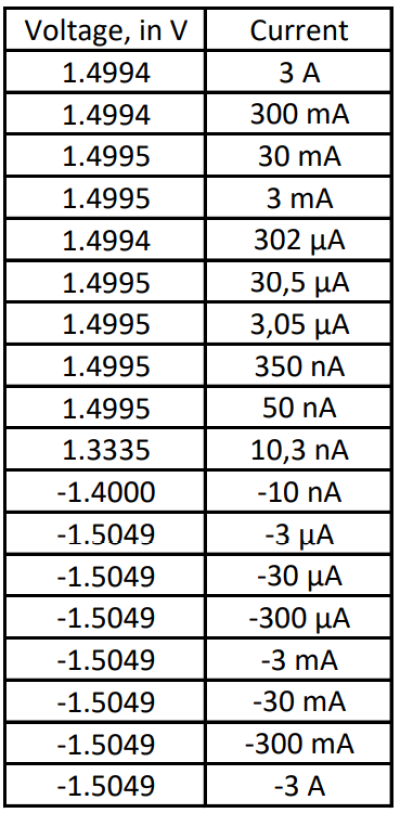

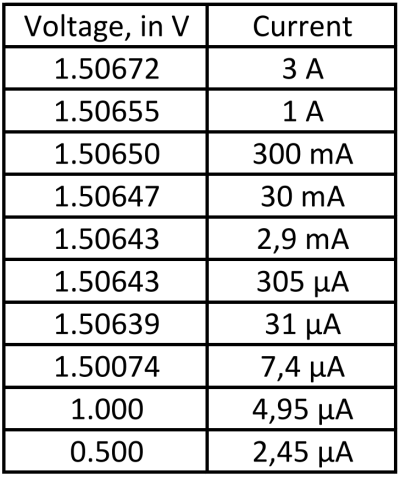

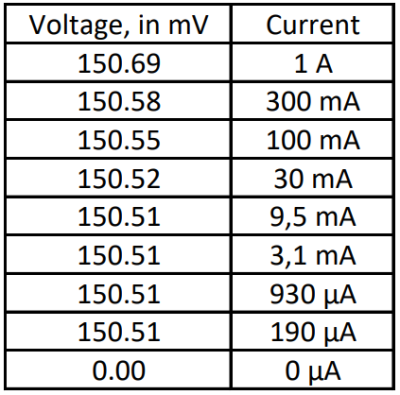

表1中列出了实际测量值。所有测量值都是在+15.5V的Vcc和15.5V的Vee下进行的,因为它们是目标仪器电源电压。为获得良好的结果,在测量过程中应注意电压表的连接位置,四线开尔文连接和稳定的参考电压源是必须的。

表1:对图1中的电路所进行的测量结果。

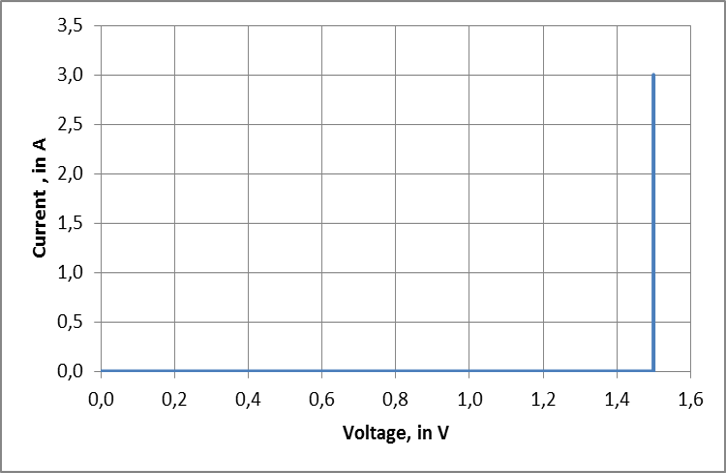

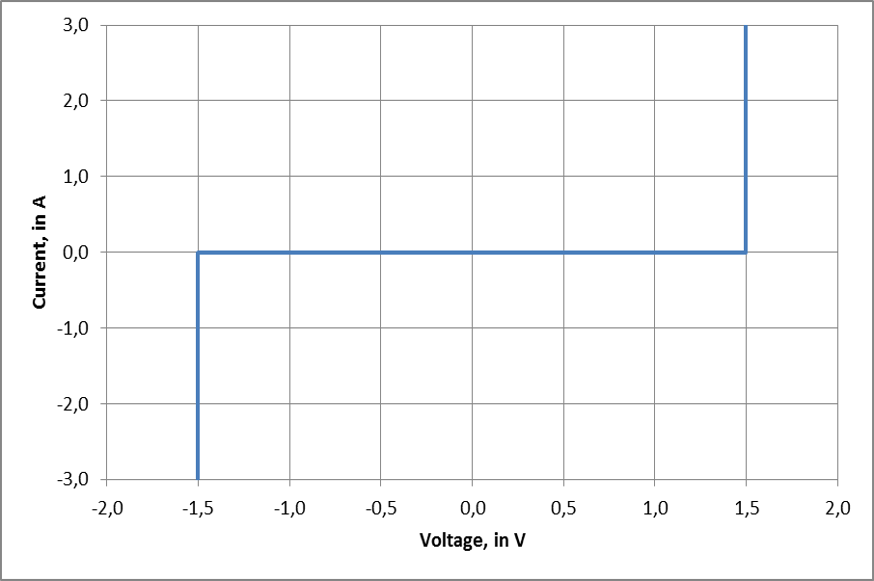

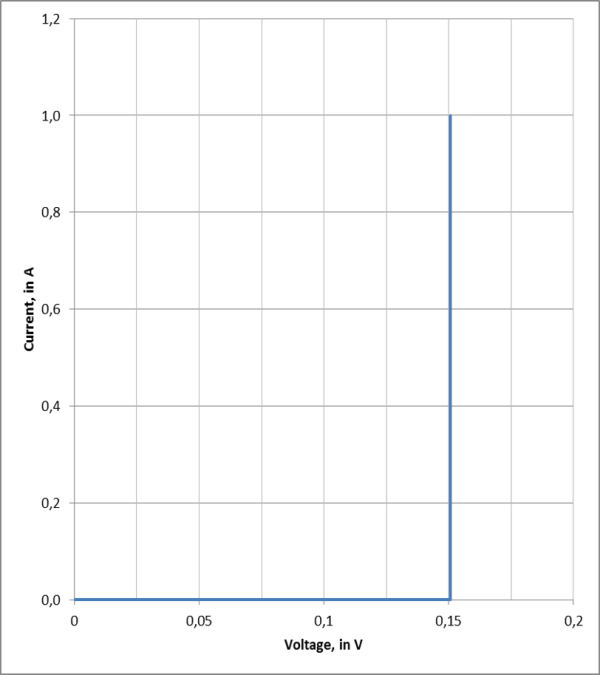

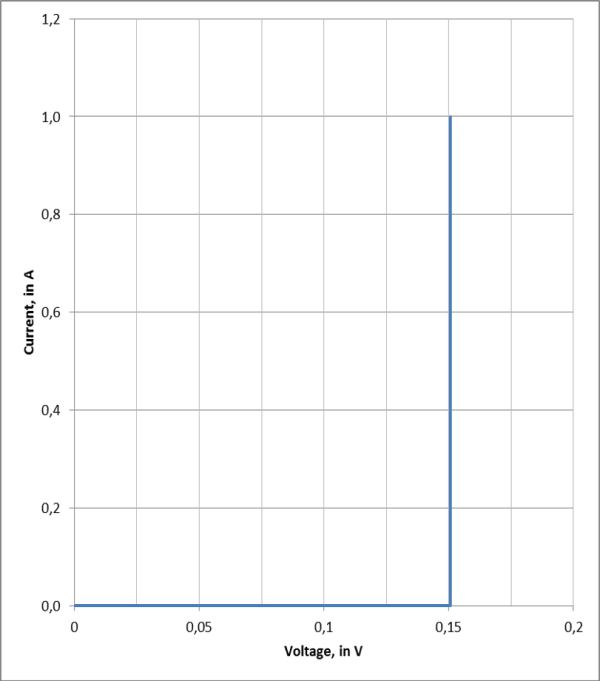

图1中电路的电流与电压曲线如图2所示。该电路将电压保持在1mV基准以内,而电流则将在3µA至3A之间变化。拐点非常尖锐。

图2:图1中电路的电流与电压关系,大电流,请注意方形拐点。

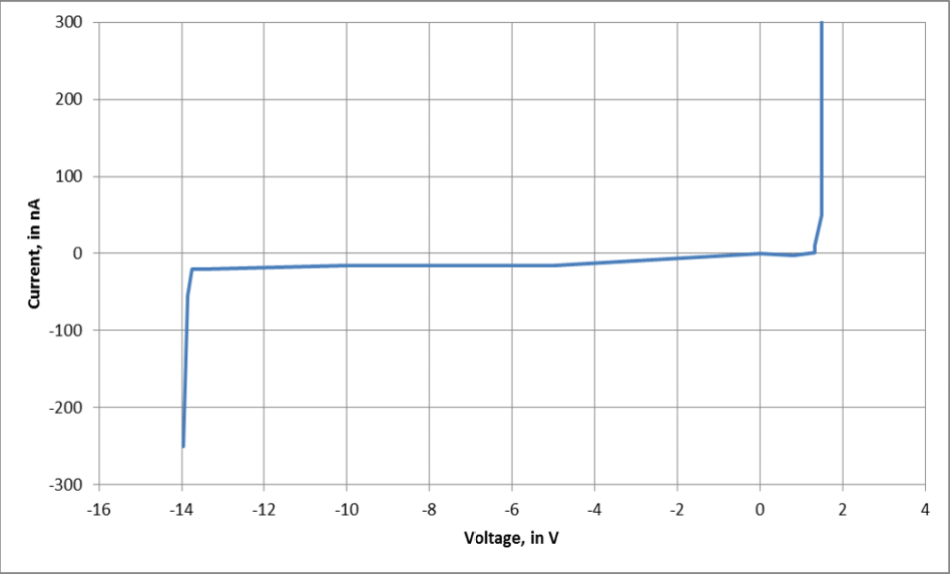

图3显示了曲线的小电流部分,总电流范围接近170dB。对于-14V和+1.5V之间的大部分范围,电流低于100nA。可以看到,当电压达到-14V时,电流增加。电流增加是因为电压越来越接近该运放的常见电压范围限制。

图3:图1中电路的电流与电压关系,小电流,显示了接近共模范围限制时电流增加。

该电路使用常用器件。应选择二极管D1和MOSFET以承载全电流,并且总压降要小于最大电流时的参考电压。根据电流值,MOSFET可能需要散热。我为D1使用了肖特基二极管,但硅PN结二极管也可以。由于U1的输入偏置电流从输出流出,所以我使用了JFET输入运放,但任何低偏置电流运放都可以工作。

对于对称应用,图4的电路运行良好。它由图1所示的正限幅器和并联的互补负限幅器所组成。单个正参考电压用于控制两个电压限制。负参考电压由单位增益反相器U1生成。

图4:对称分流电压限制器的原理图。

静态测量结果如表2所示,图5是相应的图表。图5显示了对称电压限制。

表2:对图4中的电路所进行的测量结果。

图5:图4电路的曲线,限制电压关于0V非常对称。

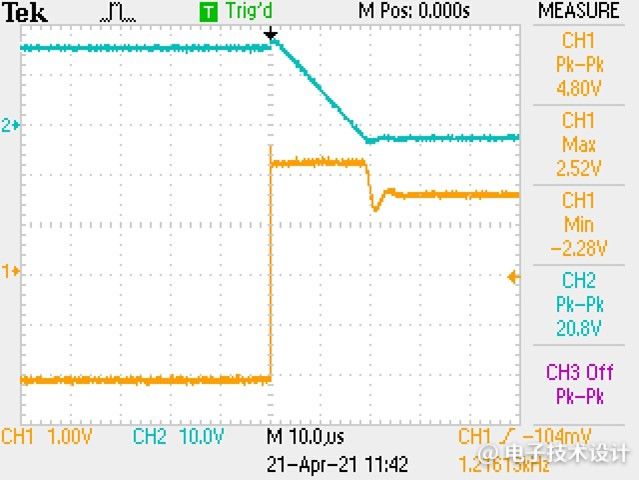

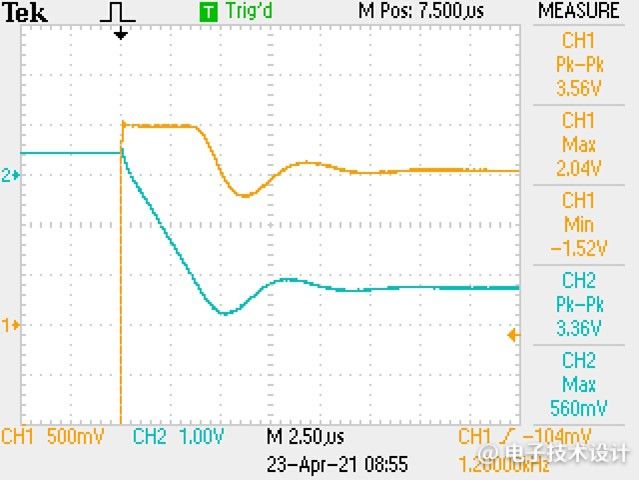

由于当电路输出电压低于限值时运放处于饱和状态,因此响应较慢。在图6中,设置用于产生4V开路峰峰值电压的发生器提供了一个方波。发电机具有50Ω的输出阻抗。示波器CH1为电路输出电压,CH2为运放输出。运放需要花大约20µs才能将电压从大约+15V向下摆动20V至-4V。

图6:图4中电路的波形显示压摆率是响应的主要限制。详情见正文。

图7是一种不会使运放饱和的改进电路。主运放U2A和U2B现在是单位增益反相放大器。二极管D3和D4在饱和状态下将运放输出电压限制为0.7V[7]。运放U2A输出现在只能从+0.7V转换到-4V。由于输入电阻R3将加载输出,因此将它选择为指定的最小可接受电阻200kΩ的两倍。我手边有一些499kΩ的1%的电阻,所以我使用了它们。波形仅使用图7中的正限幅器部分获取,R3和R7具有200kΩ电阻。

图7:对称分流电压限制器原理图,最终运放在反相模式下运行。

图8中示波器CH1为电路输出电压,CH2为U2A输出。响应时间为5µs,比初始电路快约四倍。

图8:图7中电路的响应时间,有界电压会产生更短的转换时间。详情见正文。

表3和图9概述了与第一个电路非常相似的静态测量结果,除了低于VREF的电流处于微安范围内。要具有不对称限制,就需要移除逆变器级并使用两个参考电压源。

表3:对图7中电路所进行的测量结果。

图9:仅适用于图7中电路正半部分的曲线,速度增加不会影响DC性能。

如果需要将电压限制在低于700mV的值,则二极管中损失的电压将使任何一个电路都几乎不可能满足该要求。但是,如果将P沟道MOSFET漏极连接到负电压源,则任何电压限制都可能甚至为0V。同样的方法可用于N沟道MOSFET。图10中的电路正是这样实现的,其性能与上述电路相当。偏移电压源,即原理图中的电池B1,应该能够提供所需的电流。

图10:能够在低于1V的电压下工作的限压器原理图。

表4给出了使用150mV基准电压和1.8V偏移电源的结果。图11中绘制了高达1A的大电流下的电流与电压曲线。电路再次显示出尖锐的拐点、低漏电和恒定的限制电压。相同的技术可用于图7中的原理图。为了将电压值限制在大约1V以下,误差预算计算应决定对运放失调电压和偏置电流最大值的选择。

表4:对图10中电路所进行的测量结果。

图11:图10中电路的曲线。

该电路可作为教具,将限制电压置零,并插入学生的测试电路中。想象一下将欧姆表的一个极性短路而将相反的极性开路会有怎样的乐趣和困惑!

为了在大电流应用中获得最佳效果,电压限制器应安装在电压源和要保护的设备之间。

我测试了各种二极管——齐纳二极管、硅PN结二极管、肖特基势垒二极管和LED——它们都没有像上述电路那样具有如此尖锐的拐点、低漏电并能承载同样大的电流或在使用时一样灵活。

通过简单的修改,钳位电压可以扩展到更高的值,但这是另一个设计实例了。

[1] Peter Demchenko, Shunt circuit clips large transients or regulates voltage, https://www.edn.com/shunt-circuit-clips-large-transients-or-regulates-voltage/.

[2] Chris Toliver, High-power shunt regulator uses BJT & reference IC, https://www.edn.com/high-power-shunt-regulator-uses-bjt-reference-ic.

[3] Adolfo Mondragon, Power Zener using the LM317. https://www.edn.com/power-zener-using-the-lm317.

[4] Stuart R. Michaels, MOSFET shunt regulator substitutes for series regulator, https://www.edn.com/mosfet-shunt-regulator-substitutes-for-series-regulator/.

[5] Robert N. Buono. High-Current, Low-Voltage Shunt Regulator, https://www.electronicdesign.com/technologies/analog/article/21756712/highcurrent-lowvoltage-shunt-regulator.

[6] Sansen, Willy. M. Analog Design Essentials. ISBN-13: 9781489978912, page 24.

[7] Pease, Robert. Bounding, clamping techniques improve circuit performance. EDN, November 10, 1983. Pages 277 to 289.

3月30日,AspenCore将在上海举办国际集成电路展览会暨研讨会(IIC Shanghai 2023),同期举办的“第25届高效电源管理及宽禁带半导体技术应用论坛”邀请到国内外多家优秀的电源管理IC原厂,欢迎感兴趣的朋友点击这里报名参会并到场交流。

Daniel Dufresne是一名退休工程师,曾从事电信、公共交通、消费品、大功率电子产品和定制仪器设计工作。他还是加拿大圣洛朗学校(Cegep de Saint-Laurent)的教授,并在加拿大蒙特利尔综合理工学院(Polytechnique Montreal)教授课程。他住在加拿大蒙特利尔,仍然从事电子项目和测试设备的修改和维修工作。

(原文刊登于EDN美国版,参考链接:Active shunt voltage limiter outshines Zener,由Franklin Zhao编译。)

本文为《电子技术设计》2023年2月刊杂志文章,版权所有,禁止转载。免费杂志订阅申请点击这里。

最前沿的电子设计资讯

最前沿的电子设计资讯