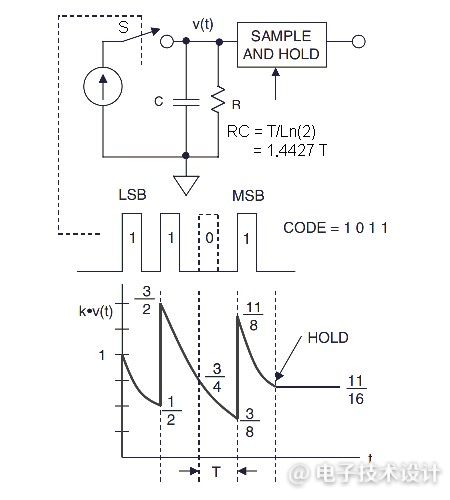

读者朋友们应该都认识大名鼎鼎的克劳德·艾尔伍德·香农(Claude Elwood Shannon),他被誉为“信息论之父”,是许多发现和发明的创始人。其中有一个优雅而具有开创性的DAC设计实例,它早在1948年就进行了首次发表,称为香农解码器(SD),如图1所示——该插图修改自ADI的Data Conversion Handbook(数据转换手册)。

图1:香农解码器DAC。

在工作中,所传入的串行(LSB在前)比特串对开关S提供控制,以便一个1比特向电容器C添加一个单位的电荷,而0则保持不变。各比特(在这个简单的例子中总共有四个)以时间间隔T相继到达。因此,在4T结束时,C上所累积的最终电压V就表示了比特串的数字内容。这种使V与比特串所表示的二进制数N成比例的技巧非常简单(感谢香农的天才),即RC=T/Ln(2)。这导致在每个时间间隔T期间,C上恰好有一半的累积电压放电,从而提供了正确的数模转换所需的二进制比特权重。然后,S&H(采样与保持)将在4T处捕获C上的最终结果。就是这样。我们只用了一个开关、一个单级RC和一个S&H,仅用了4比特时间就完成了4比特DAC转换。

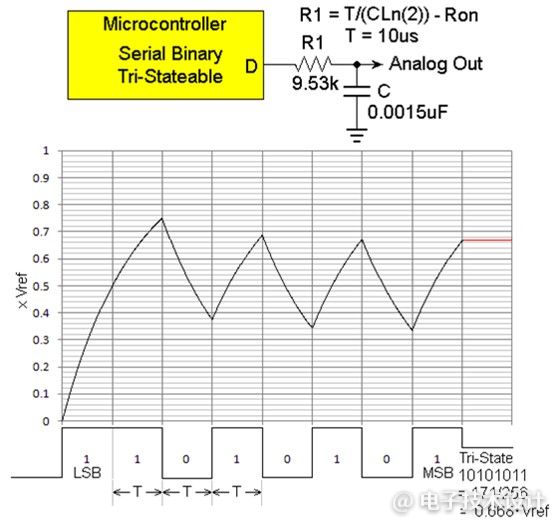

图2展示了使用自1948年以来所出现的器件的8比特SD的样子。请注意,它非常类似于基本的PWM DAC,仅包括典型的通用输出比特D和单级RC——(R+Ron)C=T/Ln(2)。Ron项用于对输出端口的导通电阻(通常为20Ω至200Ω)提供校正。稍后我们会看到为什么Ron很重要。假设有一个典型的8比特串行串=10101011=171,T=10µs,C=0.0015µF,Ron=120Ω,R=9.53kΩ,Vref=5V逻辑电源,则模拟输出=171/256*5V=3.34V。

图2:现代香农解码器实现。

所需的S&H功能可在将模拟输出累加后通过简单地使D处于三态状态而免费提供,从而使电容器C保持在最终电压并因此成为其自身的S&H。

之前我声称SD是PWM的更快替代品。是吗?8比特PWM的基本周期为256个时钟周期,为了将纹波抑制到LSB电平,RC滤波器时间常数需要约等于64个PWM周期,并且还需要Ln(256)=5.5个时间常数,才能将其稳定到1LSB。这增加了256*64*5.5=90,112个时钟周期的总PWM DAC转换时间,用以转换、滤波和稳定到最终的8比特值。

同时,8比特SD将在仅8个T周期内完成所有这些工作,因此显然产生了90,112/8=11,264:1的SD与PWM速度比,并且所使用的器件数与基本PWM相同!

但这真的是一个公平的比较吗?不完全是。

首先,关于速度,PWM时钟周期通常会以专用的片上计数器/定时器硬件生成,而SD的比特移动和最终使输出端口比特处于三态状态则可能需要一些软件交互。这种差异很可能使SD比特率比PWM时钟慢——也许慢10倍。因此,对SD与PWM速度比的更实际的估计可能更接近1,100:1,而不是11,000:1。

其次,关于器件数量,有这样的考虑:PWM会连续自动刷新其输出,而图2中所示的基本SD则不会。图2每隔几毫秒就需要运行一个转换周期,以刷新C的电荷、抵消压降并保持稳定的输出。当然,在这些转换过程中,模拟输出将非常不稳定,从而会产生负载所看到的瞬时输出毛刺。

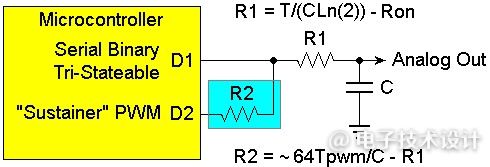

一些负载能容忍这种周期性干扰,但很多负载则不能。要想避免故障是可能的,但要做到这一点,就必须增加器件数量。图3提出了一种可能的解决方案。

图3:用于防止SD输出下降的补充PWM。

用设置为与SD相同的输出电压的“维持器”PWM来补充SD的速度,可以对由SD最初(快速)设置的相同电容器电荷进行保持。

该解决方案仍然不够完美,因为SD和PWM时间常数之间的大比率意味着R1和R2之间的比率同样大,这会对R2施加大电阻以获得足够的纹波抑制,因此就会使模拟输出的稳态驱动能力非常有限。当然,每当SD转换序列设置新的输出电压时,仍然会出现输出毛刺。

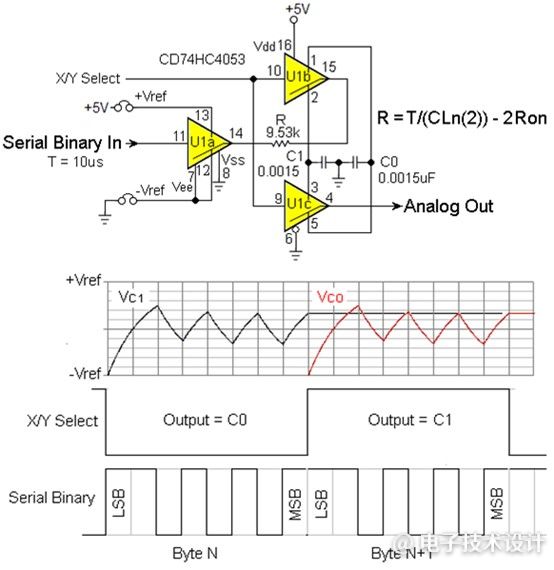

图4为这些问题给出了一种完整解决方法,即通过实现两个S&H转换/保持电容器,让它们通过U1c切换,以便其中一个提供S&H功能(C0/1,通过X/Y Select=0/1选择)和恒定输出电压,而另一个通过U1a和U1b执行下一次DAC转换。于是它们的角色交换,等等。

图4:切换SD。

图4拓扑结构的另一个功能是它能够接受独立于逻辑电源和地的参考电压输入(+Vref、-Vref)。这比依赖逻辑电源的(通常有限的)稳定性和双极性(-Vref到+Vref)输出跨度(如果-Vref为负)可以实现更好的DAC精度。

而且,它仍然只需要使用四个器件。

SD具有固有的可编程分辨率。无需任何电路修改即可容纳任何长度的比特串(6、10、12等)。此外,由于SD转换时间与比特串长度(n)成线性比例,而PWM转换时间与2n呈指数比例关系,因此SD的速度优势只会随着比特串长度的增长而变得更好。

SD精度取决于RC时间常数和比特间隔T/Ln(2)之间的准确匹配。这两个数字之间的差异将导致比特权重与正确的2.0不同,从而影响单调性和微分线性。因此,建议使用精密金属膜电阻器和零温度系数C0G或NPO电容器,并如前所述对SD信号路径中开关元件的阻抗(Ron)进行R校正。

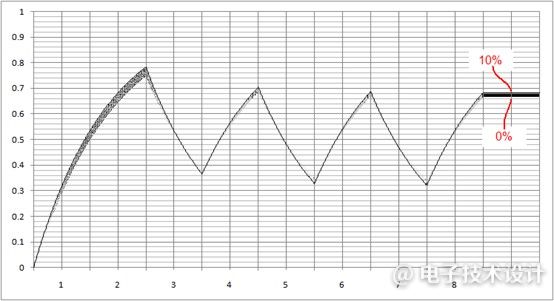

图5显示了从0%(RC=1.44269T)到10%(RC=1.58696T)的RC时间常数误差对转换结果的影响。

图5:0%至10% RC误差的影响。

(原文刊登于EDN美国版,参考链接:The Shannon decoder: A (much) faster alternative to the PWM DAC,由Franklin Zhao编译。)

本文为《电子技术设计》2023年3月刊杂志文章,版权所有,禁止转载。免费杂志订阅申请点击这里。

最前沿的电子设计资讯

最前沿的电子设计资讯