据Arteris官网消息,系统IP供应商Arteris宣布推出物理感知片上网络(NoC)互连IP Arteris FlexNoC 5,可使SoC架构团队、逻辑设计人员和集成商能够整合跨功率、性能和面积(PPA)的物理约束管理,以提供连接SoC的物理感知IP。该技术使物理融合速度比手动优化快5倍,且布局团队可以减少汽车、通信、消费电子、企业计算和工业应用的迭代次数。

3月30日,AspenCore将在上海举办国际集成电路展览会暨研讨会(IIC Shanghai 2023),同期举办的“EDA/IP 与 IC 设计论坛”,为大家提供一个高效交流的互动平台,欢迎感兴趣的朋友到场交流。点击这里报名。

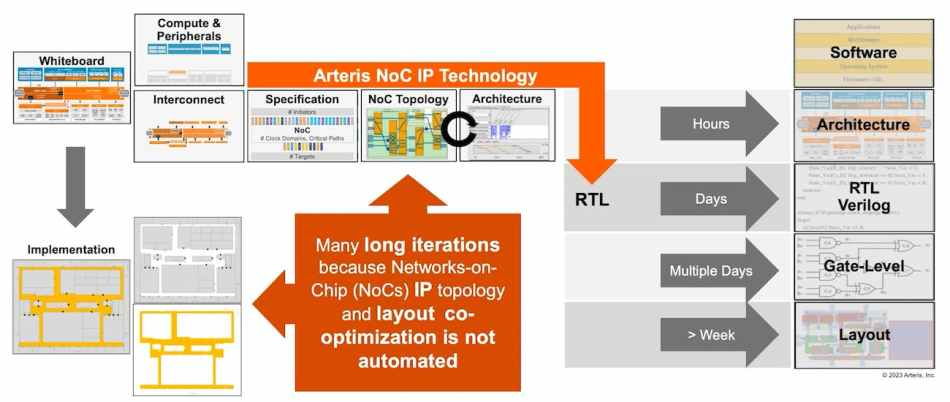

目前,IC设计人员通常使用手动工作流程,包括大量的流水线插入迭代、为单元物理放置创建大量工作约束,以及冗长的NoC放置和路由迭代以收敛于SoC PPA目标。相比之下,FlexNoC 5物理感知消除了这些迭代,并缩短了各种手动步骤的持续时间,使后端物理设计时间和工作量的物理收敛速度提高了5倍。生成的物理优化的NoC IP实例随后准备好输出到物理综合和布局布线以供实施。

大型7nm SoC可能需要6,000多个流水线寄存器,并且手动执行流水线寄存器的插入总是会导致过度设计。资料来源:Arteris

Sondrel首席执行官Graham Curren表示,物理限制一直是一个重要的问题,在16nm以下的几何尺寸更为重要。IC 设计服务供应商 Sondrel 在其定制SoC设计项目中采用了FlexNoC 5,据Curren称,最新的FlexNoC 5及其物理感知技术使他们的RTL团队能够验证架构是否满足物理约束,并为布局和布线团队提供更好的起点。

Arteris总裁兼首席执行官Charles Janac补充说,如果没有物理意识,IC开发人员可能最终会得到难以甚至不可能进行布局和布线的SoC架构。“这可能会导致多次转弯、整体项目延迟风险和额外的项目成本,特别是对于16nm及以下的几何形状。”

此外,FlexNoC 5扩展了对Arm AMBA 5协议和IEEE 1685 IP-XACT的支持,包括与Arteris Magillem的连接流,用于NoC与其他SoC IP块的集成。FlexNoC 5还支持经过生产验证的Arteris弹性选项(用于汽车功能安全认证和数据中心可靠性)、用于优化内存流量的高级内存选项,以及用于超大型设计的Arteris选项。

3月30日,AspenCore将在上海举办国际集成电路展览会暨研讨会(IIC Shanghai 2023),同期举办的“EDA/IP 与 IC 设计论坛”,为大家提供一个高效交流的互动平台,欢迎感兴趣的朋友到场交流。点击这里或扫码报名:

最前沿的电子设计资讯

最前沿的电子设计资讯