任何半导体制造过程都可以分为五个主要阶段:晶体生长、切片和研磨、抛光、外延(epi)与器件制造。第三个步骤,即一般所谓的“抛光”,正是基板生产的最后阶段。这个步骤对于原子级平滑基板表面获得高度平面性特别重要,这对于晶圆的后续处理至关重要。

尽管化学机械抛光(CMP)有一段时期一直是最常用的基板抛光技术,但随着一种新引进的技术——等离子体抛光干式蚀刻(PPDE),成为牛津仪器公司(Oxford Instruments Plc.)旗下Oxford Instruments Plasma Technology提出的有效替代方案,可望克服CMP带来的一些限制。

在此前瑞士达沃斯(Davos, Switzerland)举行的国际碳化硅及相关材料会议(International Conference on Silicon Carbide and Related Materials,ICSCRM)上,Oxford Instruments推出这种用于碳化硅(SiC)基板的新型等离子体抛光技术。等离子体抛光可作为传统CMP技术的直接替代方式,旨在巧妙地填补CMP目前的需求缺口。

3月30日,AspenCore将在上海举办国际集成电路展览会暨研讨会(IIC Shanghai 2023),同期举办的“第25届高效电源管理及宽禁带半导体技术应用论坛”,为大家提供一个高效交流的互动平台,欢迎感兴趣的朋友到场交流。点击这里报名

本文主要介绍Oxford Instruments所开发的PPDE技术。Oxford Instruments成立于1950年代末,是英国牛津大学(University of Oxford)的衍生企业。目前,该公司为许多世界领先的公司与科研团体提供高科技产品与服务。

Oxford Instruments Plasma Technology战略生产市场副总裁Brian Dlugosch说:“我们的等离子体技术有近50%的业务集中在企业研发与大学。然而,剩下的50%业务则围绕着服务生产客户而展开,随着我们的化合物解决方案在依赖先进材料的高增长市场上取得动能,其趋势正明显朝向生产方向发展。”

根据Dlugosch的说法,SiC是Oxford Instruments希望进入生产客户的产品之一,因为市场对于这种半导体有很高的需求,随之而来的是需要大量的制造过程。

根据市场分析,对汽车行业的6英寸晶圆供应预测正在增加,需求缺口明显,这对整个电子行业是相当具有挑战性的。这项解决方案目前支持150mm,但硬件可兼容200mm的生产。该公司的专利方法可提供光滑且无损伤的SiC基板表面与亚表面。这项成就对于实现低缺陷密度的外延生长至关重要。

Dlugosch说:“CMP有其局限性,可能减缓SiC在电动汽车与可持续能源使用的设备应用。等离子体抛光技术有助于克服这些限制,并能满足高度增长市场的需求。”

等离子体抛光技术具有可扩展性,无论晶圆尺寸如何,都能为SiC基板提供相同的效果。这使得符合行业标准的晶圆处理、监测与控制技术得以应用,从而减少接触时间,同时提高产量与效率。

除了缺乏可扩展性,CMP还存在一些限制,涉及大量的环境成本与高营运成本,包括其所附带产生的泥浆,这些都导致了更高的购买成本、处理成本,以及大量用水。一座半导体制造厂的用水量几乎有40%与CMP有关。此外,CMP对晶圆施加的物理压力意味着可能发生破损问题。

“而我们这种等离子体抛光工艺的首要好处是降低成本,”Dlugosch提到,“相较于CMP,等离子体抛光每片晶圆的成本更低,化学品与耗材的使用量更少,工艺稳定性也有极大的改善。”

化学机械过程会对基板施加压力,从而增加晶圆的损耗与断裂。当颗粒与SiC刮擦时,会在表面留下划痕。等离子体抛光是一种无接触的方式,可以有选择性地从表面去除受损的SiC,同时保持良好的表面质量。

PPDE的其他好处是每个晶圆的成本较低,化学品与消耗品的使用较少,以及更好的工艺稳定性与MTBC。

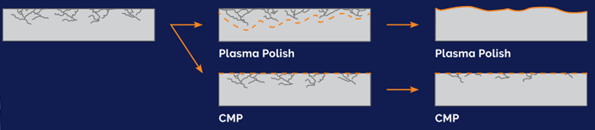

关于晶圆表面与亚表面所发生的问题,必须了解的关键之一在于表面更光滑不一定更好。CMP对SiC表面进行很好的均匀化处理,并产生平坦的表面,但针对表面下的损伤并不一定有效。相反地,等离子体抛光可以选择性地针对存在缺陷与损坏的材料,这些材料结合较弱,也更容易蚀刻。最后一点在图1中也特别强调:剩下的部分不一定是更光滑,但却是更高质量的晶体。

图1:比较CMP与等离子体抛光最后产生的晶体质量。

Oxford Instruments以两个步骤验证其等离子体抛光工艺。第一个步骤包括通过KOH蚀刻、Candela与外延表面粗糙度来验证外延层的特性。第二步是与合作伙伴Clas-SiC晶圆厂合作制造设备,以验证等离子体抛光基板。Clas-SiC在其位于苏格兰的晶圆厂运营,提供CMP与PPDE制备的晶圆,并评估晶圆的质量,将它们用于相同设备生产线,生产二极管与MOSFET。1,200V SiC MOSFET器件的整个晶圆均合格,提供与CMP制备的晶圆相当的参数结果与产能,甚至是更好的良率。

最后,经由Clas-SiC进行的评估表明,在PPDE基板上生长的外延具有与在CMP基板上生长的外延相同的特性,而且MOSFET器件显示出相当的性能。Oxford Instruments在最近的ICSCRM上分享了来自Clas-SiC的全晶圆性能数据。

Dlugosch说:“我们相信解决方案对CMP有明显的优势,它同时也是环保的解决方案,不仅成本更低,产量可能也更高。”

由于需求旺盛,SiC基板目前供不应求,而在基板上生产的宽禁带半导体也供不应求。行业需要新的解决方案,特别是随着高度增长的电动汽车与可持续能源市场在其应用中使用越来越多的这一类化合物半导体,预计这一制造差距将会成指数级增加。根据Oxford Instruments的说法,等离子体抛光是一种自动配置的CMP替代方式,能够立即降低每片晶圆的成本,降低运营支出,同时也是加速朝200mm过渡转换的关键技术。

Dlugosch提到:“我们已经验证并推出了一种更清洁、更环保且成本更低的CMP替代方式,它有潜力克服CMP的技术限制,并加速SiC在一些令人振奋的应用中采用。”

为了让道路上的每辆车都能电动化,续航里程更长的电动汽车不仅应该成为常态,其所使用的电池也应该更实惠,充电更快。由于硅即将达到其理论极限,该行业正在转向将SiC用于电力电子,因为它具有更宽禁带、更高击穿电场与更高的热导率。相较于硅器件,基于SiC的MOSFET确实能够实现更低的损耗、更高的开关频率,以及更高的功率密度。

(原文刊登于EDN姊妹网站EE Times,参考原文:Plasma Polish Dry Etch Brings Next-Level SiC Quality,由Anthea Chuang编译。)

3月30日,AspenCore将在上海举办国际集成电路展览会暨研讨会(IIC Shanghai 2023),同期举办的“第25届高效电源管理及宽禁带半导体技术应用论坛”,为大家提供一个高效交流的互动平台,欢迎感兴趣的朋友到场交流。点击这里或扫码报名

最前沿的电子设计资讯

最前沿的电子设计资讯