PUF技术运用了简单、经济高效且灵活、无需存储密钥的方式,建立信任根(Root of Trust)。对嵌入式系统而言,安全性不再只是属于“事后讨论”的问题,如PUF这类新技术,逐渐在微控制器(MCU)到高性能FPGA的应用中出现,显然现在对物联网(IoT)设备,更是如此。

然而,当PUF应用于替芯片产生特定密钥,还要确保不同芯片间ID的低重复率仍具有挑战性。据嵌入式系统和互联设备端到端网络安全解决方案供应商Secure-IC的说法,由于表现不理想,90%的PUF技术很难独立运作。因此,PUF需要透过大量注册及重建,以提升ID或密钥的质量。

3月30日,AspenCore将在上海举办国际集成电路展览会暨研讨会(IIC Shanghai 2023),同期举办的“EDA/IP 与 IC 设计论坛”,为大家提供一个高效交流的互动平台,欢迎感兴趣的朋友到场交流。点击这里报名。

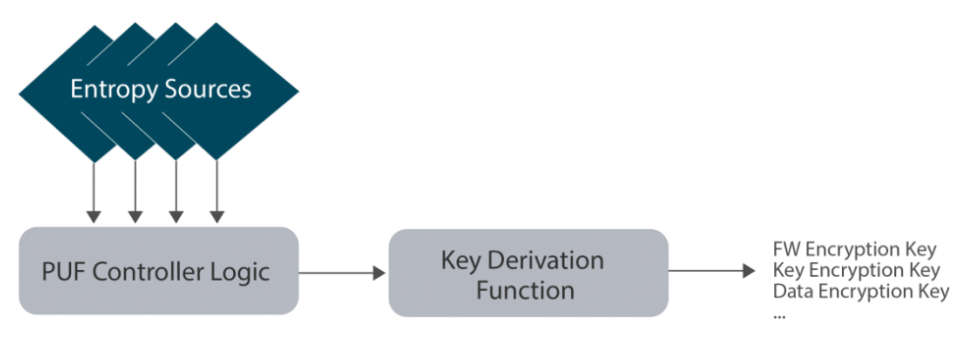

图1:PUF运用内置在设备里的变量,产生独特、无法复制的密钥传到相对应的输入。 (来源:Secure-IC)

换言之,PUF仅能用于加密密钥架构下的注册,作为可靠的安全依据。但因每个芯片都需要个性化,就会使注册阶段变成一个成本高昂的过程,包括得经过长时间测量、特征化、衍生辅助数据及最后的辅助数据编程等流程。当芯片量产时,测试阶段需要高效率的个性化,就难以接受PUF所需的流程。

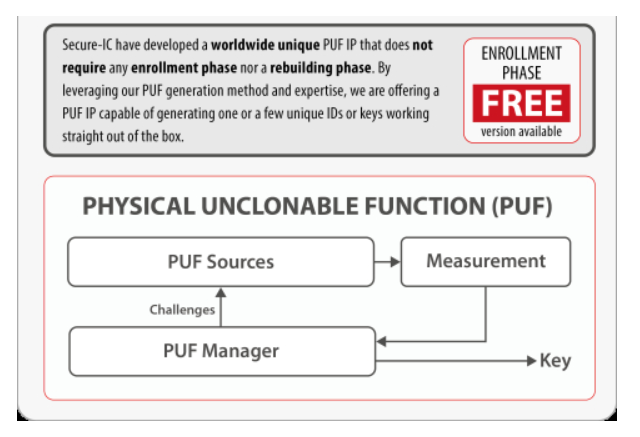

此外,注册所需的程序,也会替意图破坏注册系统的黑客敞开了大门,比如,他们很可能会强制所有密钥位呈现一致。为了应对注册及重建阶段会面临的挑战,以及得付出的高昂成本和系统容易被攻击的担忧,Secure-IC与专注IoT软硬件安全的Trasna,携手推出一种不需注册及重建的PUF解决方案。 新的PUF IP可以生成一个或多个唯一且可直接使用的ID或密钥,做为芯片安全启动、信任根及生命周期管理的基础。

图2:新的PUF IP省去加密密钥架构中的注册阶段。 (来源:Secure-IC)

这项进步展现了PUF做为新技术,如何克服设计障碍并在物联网安全领域取得进步。Secure-IC的新PUF IP符合ISO/IEC 20897网络安全规范,并已整合进Trasna用于窄带物联网(Narrowband Internet of Things, NB-IoT)的系统级芯片(SoC)解决方案。为跟芯片整合,并进一步强化其安全性,PUF技术仍在持续进步中。

(原文刊登于EDN美国版,参考链接:PUF update: New IP bypasses the need for ID enrollment,由Ryan Tsai编译。)

3月30日,AspenCore将在上海举办国际集成电路展览会暨研讨会(IIC Shanghai 2023),同期举办的“EDA/IP 与 IC 设计论坛”,为大家提供一个高效交流的互动平台,欢迎感兴趣的朋友到场交流。点击这里或扫码报名:

最前沿的电子设计资讯

最前沿的电子设计资讯