3月30日,在由AspenCore主办的“2023中国IC领袖峰会”上,英诺达创始人、董事长王琦发表了“突破功耗桎梏——面向下一代低功耗IC设计的挑战”的主题演讲。

他指出,从趋势来说,云计算、汽车电子和5G各个方面其实有一个共同点,也就是都要解决功耗问题,不管是绿色能源,还是芯片设计。

设计创新?还是遵从摩尔定律?这是设计开发同仁们需要去综合平衡的,“魏少军教授提到,如果能用14nm甚至28nm做出7nm的产品性能才是真正的高手。而这句话的背后除了需要扎实的技术功底和深厚的设计经验外,设计创新也是至关重要的,如何做到这一点,其实也充满挑战的,其中功耗就是一个制约的问题。”王琦补充道。

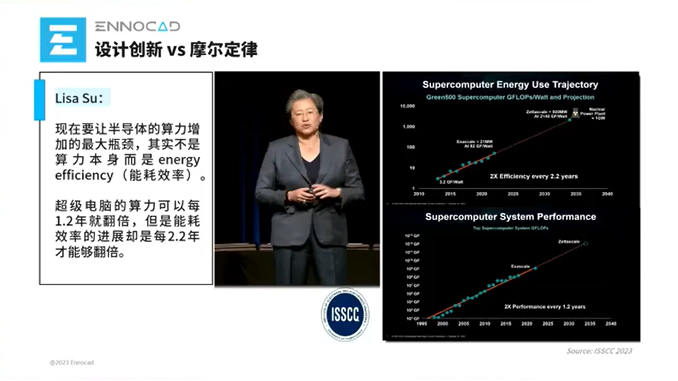

相对的,Lisa Su在2023年 ISSCC会议上提到,超级电脑的算力可以每1.2年就翻倍,但是能耗效率的进展却每2.2年才能够翻倍。也就是说在解决功耗问题之前,电脑算力是无法做到每隔1.2年翻倍的,所以如何超越摩尔定律,解决算力增长瓶颈,能耗效率(energy efficiency)的提升将是一个有效的突破方向。

“讲了这么多环节,就是想给大家引入今天的主题,功耗设计会是芯片设计的重要挑战之一,不论是最先进的制程,还是魏教授所提到的成熟节点制程,这个功耗的设计都会是一个很大的挑战。”王琦指出。

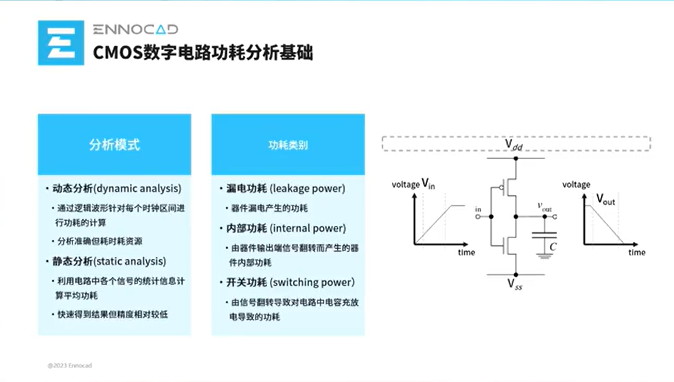

功耗有两种分析;一种是静态分析,一种是动态分析。从功耗类别来看有漏电功耗、内部功耗、开关功耗。下图是最常见的CMOS电路反相器,驱动外部电容。“首先,这个电路不工作的时候就有漏电功耗,虽然在CMOS电路里面漏电功耗已经是最小的,因为在静态状况下永远只有一个是开的,一个是关的,但这个功耗是现在电路设计的瓶颈。此外一个电路不可能不工作,电路工作就会有翻转,翻转就会有内部功耗。在翻转过程当中,这两个管子都是打开的,这里有动态功耗。最后是开关功耗,当电源对电容充放电的时候就会有开关功耗。”王琦分析说。

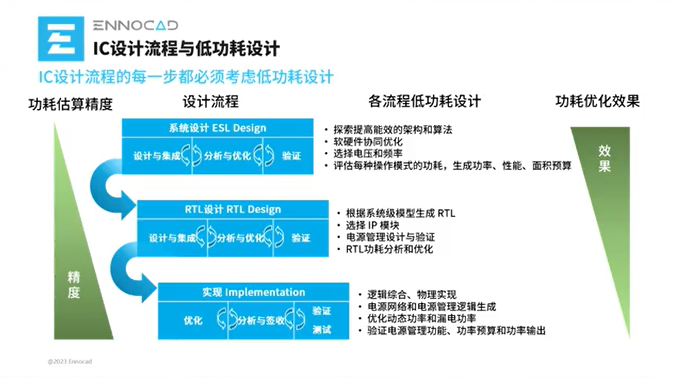

国产EDA突破要从点工具突破。很多人对点工具有一个误解,以为只能用在设计流程中单一节点。以功耗为例,它虽然一个点工具,但是可以贯穿整个设计流程。

每个功耗分析在每个节点都有它的难度。“早期分析时的难度包括IP模型、逻辑门信息、物理信息,需要确认如何去做信息估算的问题;到了逻辑网表的时候,IP模型、逻辑门信息都有了,但是这个时候缺乏物理信息,如何确认最后阶段存在的问题是否都得到处理是这个阶段需要解决的;最后IP模型、逻辑信息以及物理信息都有了,最终的结果就一定准确吗?还是不一定,其实在每个阶段都需要拿到信号翻转的信息,这是一个共同的难点,不管是前端,还是后端。”王琦强调。

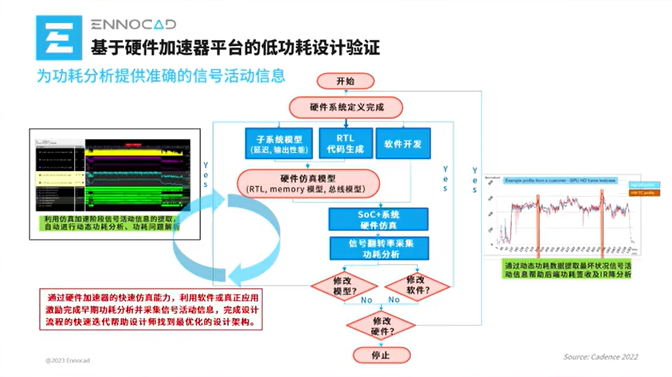

信号的翻转或活动信息很难获取,但通过硬件仿真加速器是非常有效的方式之一,简单讲硬件仿真加速器是一种验证平台,如果运行软件仿真速度是1的话,运行硬件仿真速度大概是千分之一,将大大提升仿真效率。

基于硬件加速器平台的低功耗设计验证流程可以解决哪些问题呢?其实不管在前端设计,用RTL,还是后面用物理实现阶段,都是可以运行这类仿真工具,通过这个仿真可以得到类似的物理逻辑波形,可以得到信号翻转率,甚至可以从信号翻转率过程当中选出我们认为是最差的一些点,把这些信息读取出来,反馈到比如后端物理实现上再去做动态功耗分析、静态功耗分析,这样功耗分析才会更准确。

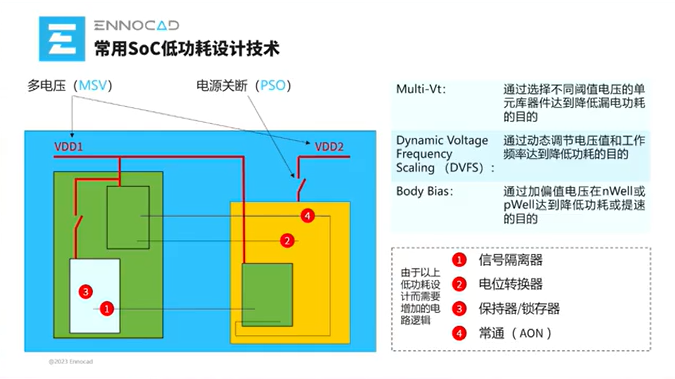

以上是通过硬件仿真加速获取关键的翻转率信息,来帮助我们做更精确的功耗分析。除此之外,在功耗设计上需要考虑很多的设计技术,下图是关于电源开关的一个简单图示,如何去理解图示的电源开关内容呢?打个比方,手机用户会很常见到,比如某个应用不用的时候,它会进入休眠模式,那这个功能在芯片上面是如何实现的呢?就是通过关掉芯片电路上的某个电源,但是芯片设计里面要实现这个概念会导致很多设计上的问题,比如有两个电压,当对高电压低电压信号进行转换时,就需要一个电压转换器;当一个模块电源是关的,从关的电源信号和开的电源信号之间需要加一个隔离器;加了隔离器之后可能会出错,这就会造成电路逻辑错误。就像我们写代码一样,代码越多,bug也会越多,在这种低功耗设计里面怎么样有一个完整的流程找出里面的bug,其实英诺达已经有一套完整的流程和产品来解决相应的问题,王琦表示。

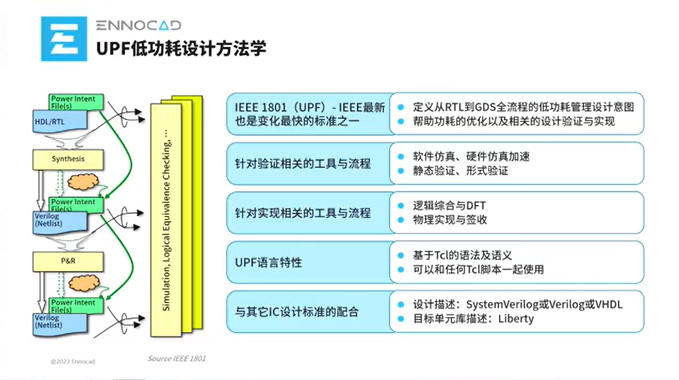

最常见的流程是通过UPF(统一功耗格式)也称作IEEE 1801,从前端设计到后端设计都可以通过这个业界标准来描述低功耗设计的方法,包括电源域,电压域,电源关断等等。工具可以根据UPF的描述在不同阶段完成低功耗设计查错诊断,比如在前端做综合的时候要加一些隔离器,在后端所有隔离器、电源转换器的电源线都要连接。如何确认有没有连对逻辑信号和电源信号?这都可以通过英诺达的流程来帮助低功耗设计进行检查,来确保我们的设计最后是正确的。

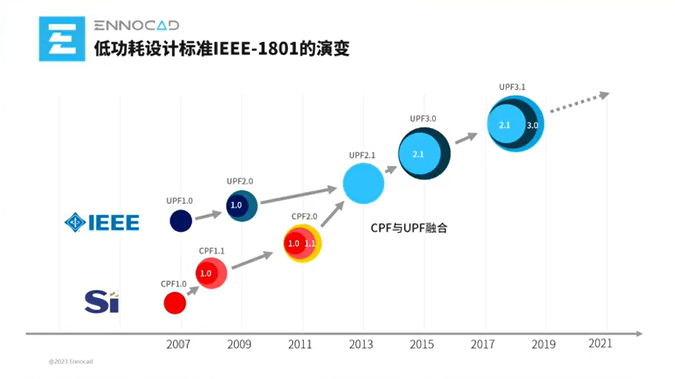

IEEE-1801(UPF)做为低功耗设计的行业标准,自从2007年推出以来,已经推出六个不同的版本。这种不断的迭代更新其实不是好事,不同版本之间势必会产生兼容性问题,这样的情况会让EDA工具在不停地适应和解决在不同版本之间存在的冲突,而工具开发方首先就要对这个标准的各个版本有深厚的理解,然后通过EDA工具内相应的算法来优化解决这些问题,这是一个艰难的过程。

据王琦博士介绍,英诺达的长期愿景是以客户需求为导向,帮助客户实现价值最大化,为中国半导体产业提供卓越的EDA解决方案。“我们一定要做客户需要的东西,一定要做帮助客户实现价值的东西,客户的成功是英诺达最好的品牌背书,也是我们的核心优势。”王琦强调。

同时,王琦博士也对英诺达核心业务做了介绍,英诺达的核心业务有如下三大版块:

一、EDA自研软件,以低功耗设计为切入点。

二、IC设计云解决方案,通过系统验证平台加速验证流程。

三、IC后端设计服务。

据介绍,EnFortius®做为英诺达发布的第一款低功耗设计静态验证工具,目前已得到了业内的大量关注,同时也进入了多家客户的设计开发流程,得到了市场的认可。“从RTL到网表级,通过UPF来做验证,点工具并不见得只能在某一个点。我们这个工具也是点工具,但是它是从RTL到GDS整个链路都可以工作的,为的就是保障低功耗设计保证流片之前没有功耗或者逻辑上的bug。同时这款工具还兼容不同版本的UPF,保证最大程度的通用性及灵活性,以支持不同客户的实际需求。我们也将会在今年4月底陆续推出另一个系列的低功耗工具,主要是如何解决在前端功耗优化潜力和精度等矛盾的问题。”王琦解释道。

英诺达还在近期推出了全新的系统验证平台EnCitius®System Verification Studio(SVS),据介绍,该系统验证平台是集成电路系统级芯片(SoC)及系统相关验证的集成式全栈解决方案,通过英诺达自主研发的验证流程和云平台,采用业界一流的硬件验证系统,同时配合专业的设计验证服务团队来完成。 “SVS将帮助用户加速验证仿真流程、降低研发成本、提高流片良率、缩短time-to-market,同时配合我们英诺达的团队及服务,将为客户快速打通设计需求与资源的渠道”王琦介绍说。

此外,英诺达基于经过量产验证的先进制程IP与SoC的开发与整合经验,可为客户提供全流程、涵盖高端工艺节点的设计服务。客户可以根据需求选择设计服务内容,依托英诺达的EnCitius SVS系统验证平台,可为客户提供管家式的定制服务。

最前沿的电子设计资讯

最前沿的电子设计资讯