近期有业内人士指出,英特尔即将推出代号为Meteor Lake的处理器,将配备L4缓存。据EDN电子技术设计了解,美国专利局一项新英特尔专利表明,英特尔已经准备好代号为 Adamantine L4 的高速缓存块,这将可用于某些 CPU。

通常,缓存通过快速为计算核心提供必要的数据来提高内存子系统的性能。但也有其他用例,因为大型缓存可以存储大量数据。该专利表明,英特尔的 Adamantine(或 ADM)缓存不仅可以改善 CPU 和内存之间的通信,还可以改善 CPU 和安全控制器之间的通信。例如,L4 可用于改进引导优化,甚至在重置时保留缓存中的数据以缩短加载时间。

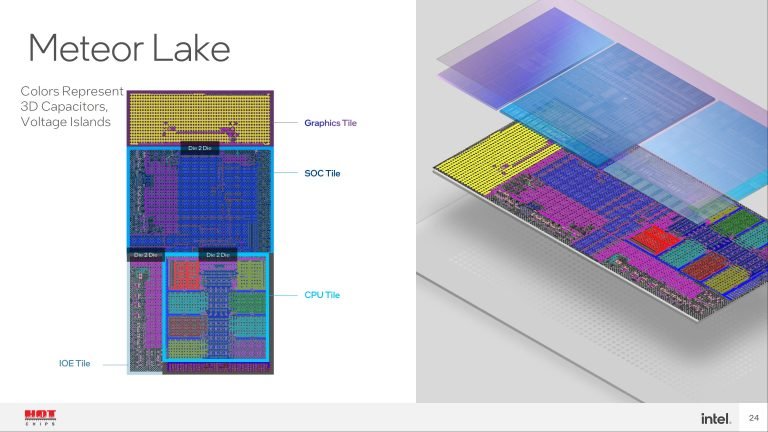

Meteor Lake 将完全采用混合架构,结合五个不同的块:CPU、SoC、GPU、I/O 和基础块。Adamantine 缓存将提供比任何典型缓存(如 L3,通常是 CPU 块的一部分)更快的访问时间。

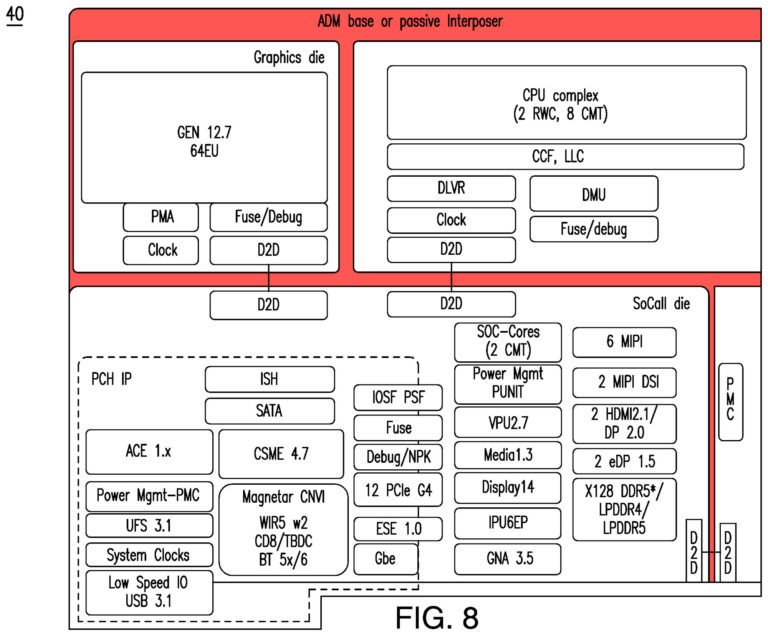

虽然专利本身没有提到 Meteor Lake,但随附的图像清楚地展示了一个处理器,该处理器具有利用Intel 4工艺生产的两个高性能的 Redwood Cove 和八个节能的 Crestmont,此外还包括一个基于英特尔 Gen 12.7 的图形小芯片,还有一个包含两个以上 Crestmont 内核的 SoC 块,以及一个使用英特尔 Foveros 3D 技术互连的 I/O 小芯片。该描述对应于英特尔的 Meteor Lake 处理器。

同时,Adamantine L4 缓存可用于 Meteor Lake 以外的广泛应用。

上图清楚地显示了2个 RWC (Redwood Cove) 和 8 个 CMT (Crestmont) 内核的 Meteor Lake。有趣的是,SOC 磁贴还显示具有两个 CMT 内核,这种特殊设计还将具有带有 64 个 EU 的 Gen 12.7 Xe 图形。

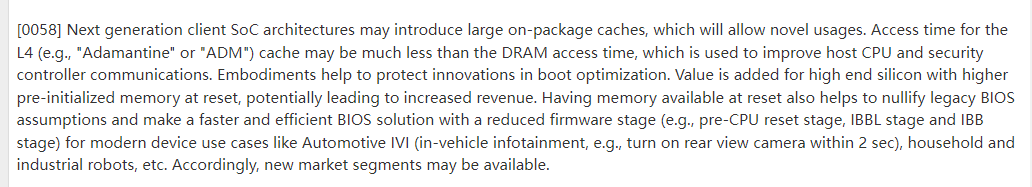

英特尔在介绍该专利的时候表示,下一代客户端 SoC 架构可能会引入大型封装缓存,这将允许新的用途。

专利介绍原文

他们认为,L4(例如,“Adamantine”或“ADM”)高速缓存的访问时间可能比 DRAM 访问时间短得多,后者用于改进主机 CPU 和安全控制器通信。实施例有助于保护启动优化方面的创新。重置时具有更高预初始化内存的高端芯片增加了价值,可能会增加收入。在重置时让内存可用还有助于消除传统 BIOS 假设,并为现代设备用例(如汽车 IVI、家用和工业机器人等)提供支持,这就推动产品走向新的细分市场。

官方预计Intel Meteor Lake将于 2023 年下半年推出。不过,该公司并未确认将首先推出哪个系列的 Meteor Lake。

参考专利:

Early Platform Hardening Technology For Slimmer And Faster Boot

最前沿的电子设计资讯

最前沿的电子设计资讯