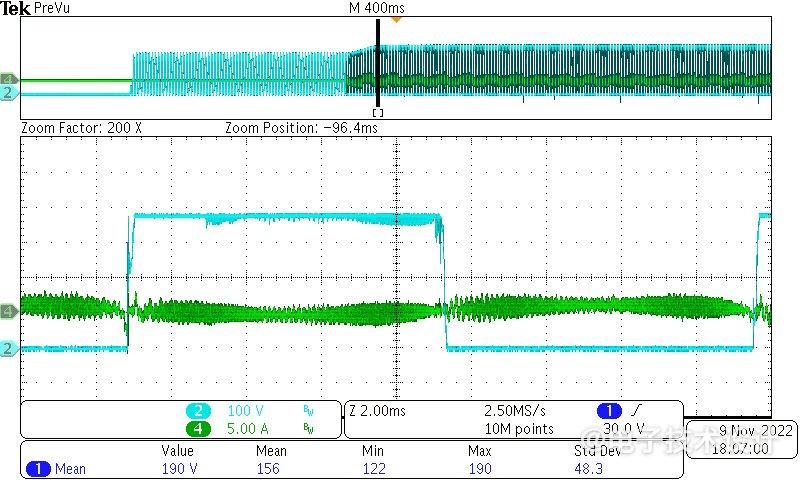

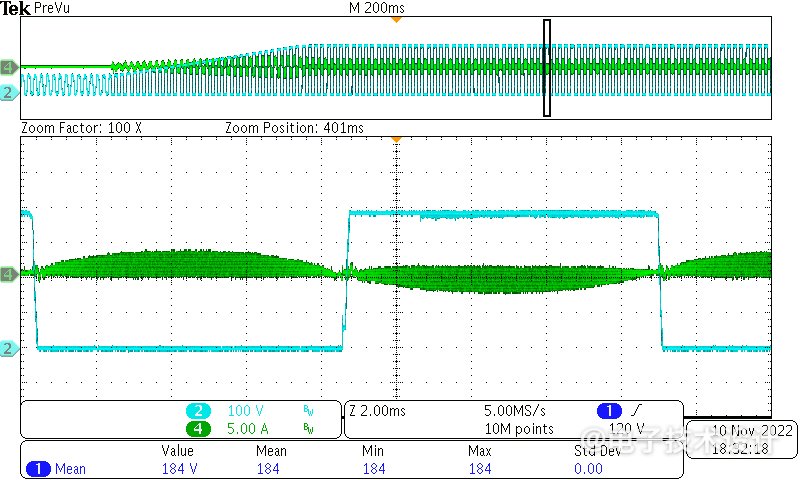

在设计升压功率因数校正(PFC)等数字电源时,你是否见过如图1所示的电流振荡?

图1:电流振荡发生在PFC阶段。

你可能认为这种不稳定的振荡是由太快的控制频带所引起的,因此就会把比例积分(PI)控制器的比例增益(KP)和积分增益(KI)降低,从而使交越频率显著降低。然后,振荡消失。

但这是最好的解决方案吗?较低的电流回路带宽可降低控制速度,但也可能导致总谐波失真(THD)测试失败。有时当你的源阻抗有点大时,振荡会再次出现。

这种不稳定还有其他可能的原因吗?如何在足够的相位裕度下实现最佳控制带宽?让我们详细分析一下数字控制回路,看看这个潜在的错误是如何引入的。并且,你也可以检查你的控制固件中是否发生了同样的情况。

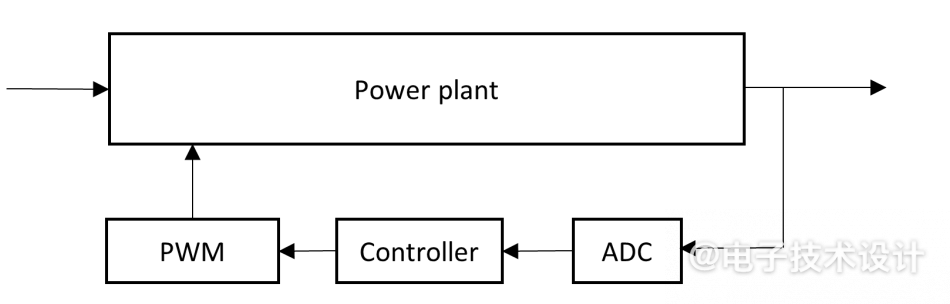

图2给出了基于MCU的数字控制系统。

图2:数字控制系统围绕MCU构建。

控制回路由三个部分组成:模数转换器(ADC),用于对目标电流/电压进行采样;数字控制器,用于生成调整值;以及脉宽调制器(PWM),用于执行调整,通过改变占空比或频率的电压来改变目标电流/电压。

开关电源(SMPS)中的ADC采样往往在两个开关周期的中间点进行,这样不仅可以避免开关的噪声干扰,而且可以得到功率电感在连续导通模式(CCM)下的平均电流值。

数字控制器在中断服务程序(ISR)中计算,并可与PWM输出同步触发。触发事件可能是以下情况之一:PWM的计数器等于零、周期或特定值CMP。

当控制器完成所有计算时,不可能立即更新PWM,但PWM寄存器必须在专用时刻由影子寄存器载入,例如当PWM计数器等于零或周期时。如果在计数器上升或下降时更改PWM值,则很可能会产生错误的PWM动作、丢失脉冲或重复脉冲。

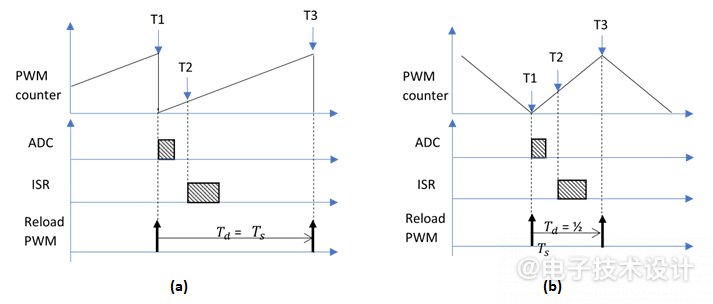

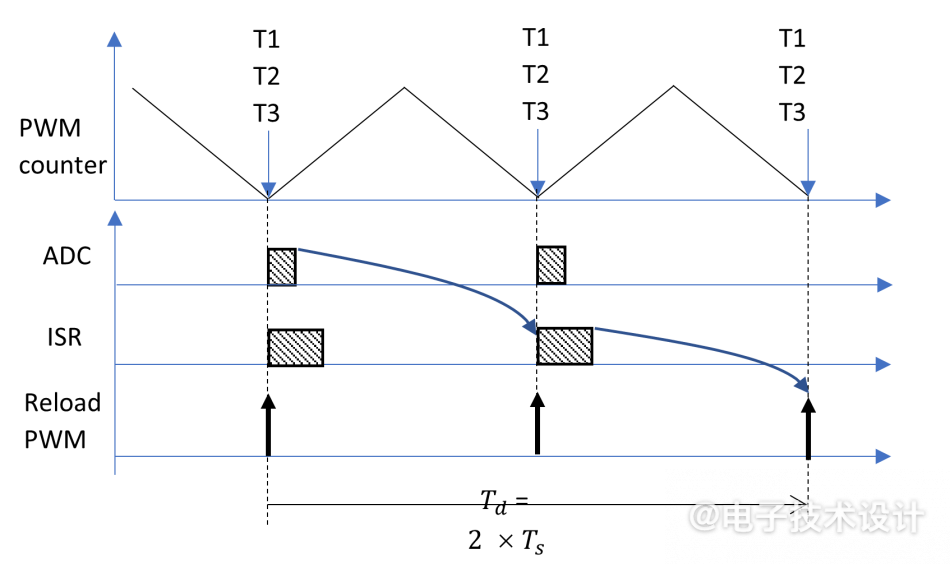

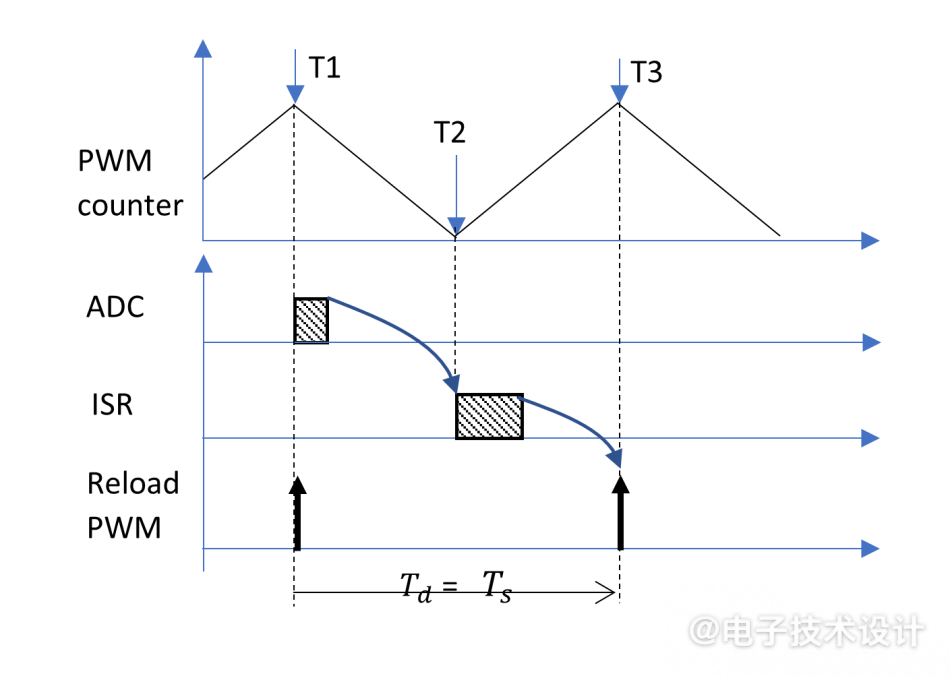

与模拟控制系统不同,数字控制是通过采样频率执行的,从采样到向PWM重新载入新值必然有一个延迟时间(Td)。PWM修改是通过调整翻转时刻来实现的,这在单边沿调制(向上/向下计数模式)中会发生一次,而在双边沿调制(上下计数模式)中则会发生两次。因此,Td最小值将是一个开关周期Ts(如图3a所示)或二分之一个开关周期Ts/2(如图3b所示),具体取决于所选的调制重新载入频率。

图3:通过PWM调整引入最小延迟时间:(a)向上模式,(b)上下模式。

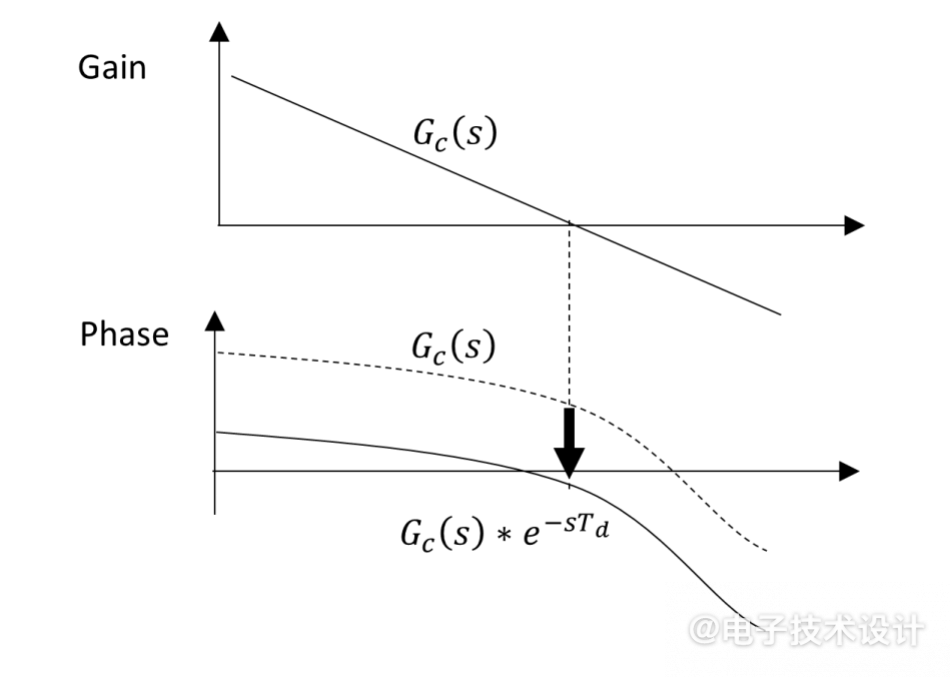

如图4所示,Td在其传递函数中表示为e-sxTd,这会降低相位裕度。当然,当相位裕度小于45°时,系统就会变得不稳定,从而产生振荡。

图4:波特图显示了时间延迟的影响。

如果执行正确,Td最小值是一个开关周期Ts或半个开关周期Ts/2。但是,如果没有考虑ADC、ISR和PWM重新载入的影响,将控制延迟延长到一个以上的开关周期,可能会降低相位裕度并导致不稳定。

例如,在图5中,当PWM计数器为零时,ADC的ISR触发器和PWM重新载入将同时开始。

虽然所有的块会同时执行,但在这种情况下能期望Td为零吗?绝对不能!

图5:错误代码引入较大延迟时间的示例。

这是因为ADC转换和ISR计算都需要远远超过一个MCU时钟周期——当ISR读取ADC结果时,ADC转换还没有完成。因此,ISR将获得“旧”样本值进行计算,最新值的计算将延迟到下一个开关周期。ISR计算完成后,新的PWM值只写入影子寄存器,从而在下一个开关周期才会被重新载入。实际上,Td的总控制延迟将是两个开关周期,即2×Ts。

除了此处所示的示例外,其他实现——例如,如果在ISR代码中将ADC值读数放在控制器计算之后,或者如果在计算控制器之前添加N周期算法平均值——可能会引入类似的扩展控制延迟。

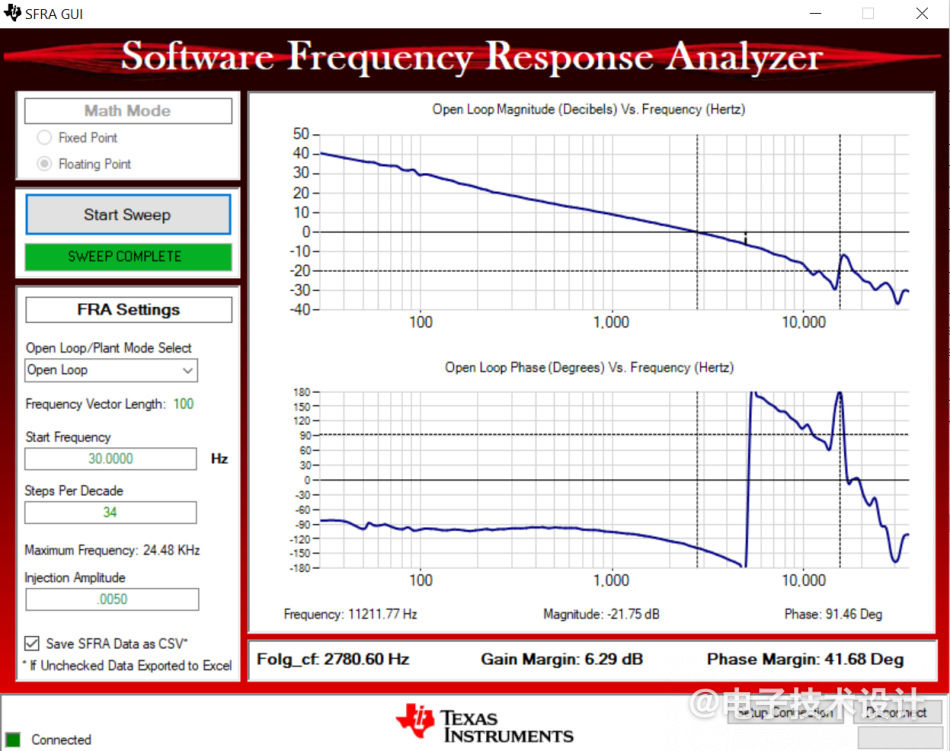

如图6所示,当我们使用图5的错误实现将增益的交越频率设置在3kHz左右时,相位裕度将为41.68°。这还不到45°,扼流圈电流会有明显的振荡,如图1的波形,所以我们不得不将交越频率降低到2kHz以下。然后,iTHD将变得更糟而无法满足要求。

图6:从波特图可看出错误的代码实现。

可以通过将ADC转换移动到计数器=周期的时刻并使PWM重新载入发生在下一次计数器=周期来轻松解决此问题,如图7所示。

图7:可通过改进代码减少控制延迟。

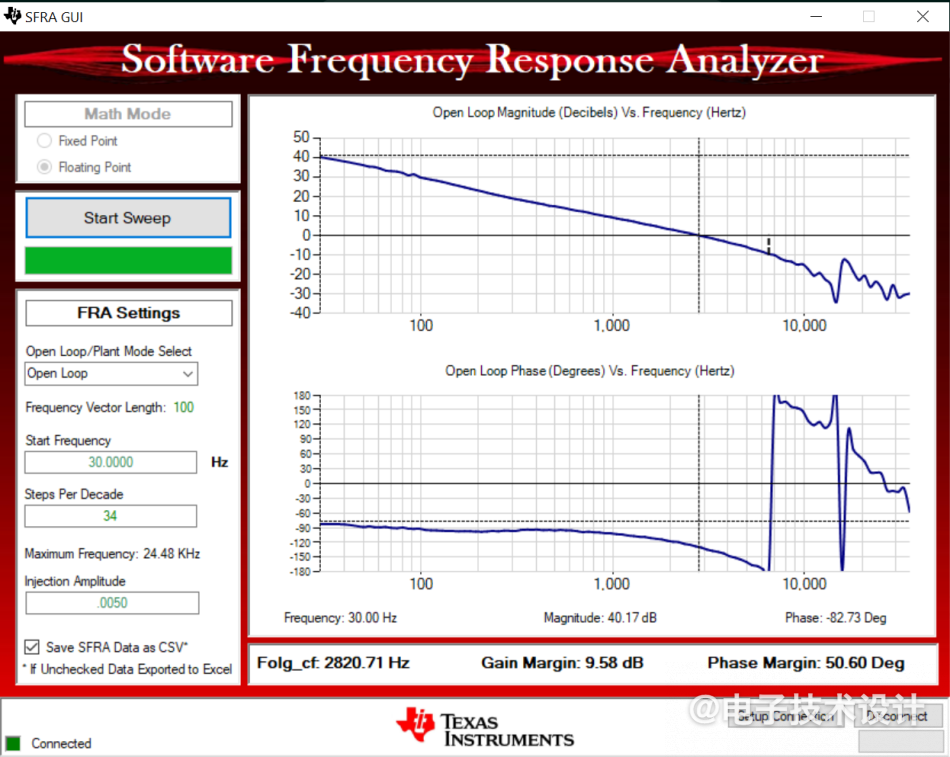

控制延迟将减少到一个开关周期。相位裕度将明显增加,电流振荡将会消失,如图8和图9所示。

图8:改进代码后的波特图。

图9:改进代码后的波形。

数字实现中的控制延迟(从ADC采样到PWM调整)会降低相位裕度并引起振荡。解决这个问题时,可考虑ADC采样、控制器计算和PWM重新载入的影响。精心组织的控制方案,可以将延迟降至半个或一个开关周期,从而增加相位裕度和回路带宽。

(原文刊登于EDN美国版,参考链接:A potential firmware mistake may lead to control instability,由Franklin Zhao编译。)

本文为《电子技术设计》2023年6月刊杂志文章,版权所有,禁止转载。免费杂志订阅申请点击这里。

最前沿的电子设计资讯

最前沿的电子设计资讯