高压碳化硅(SiC)MOSFET在许多行业都有多种应用。传统的硅基MOSFET热性能有限,开关频率较低,因此无法在高频工作中高效工作。卓越的电气参数,如更低的RDS(ON)和更高的开关频率,可为电机驱动、焊接机、可再生能源系统、充电站和IT数据中心中的应用提供更高的功率密度。此外,SiC MOSFET可以在400°C以上的温度下运行,热阻更低,有助于降低传导损耗。同时,它们在更高频率下工作的能力有效地增加了热密度。低传导和开关损耗的理想特性使这些半导体器件是高功率应用的理想选择。

在HVDC转换器、大功率逆变器(图1)等许多操作中,功率MOSFET必须根据特定要求串联或并联。然而,这些配置带来了不同的挑战,甚至可能损坏这些设备。下面列出了其中一些实例:

上述实例表明,在将这些SiC MOSFET安装到此类关键任务应用之前,测量这些SiC MOSFET的可靠性和鲁棒性至关重要。本文围绕1200V DMOSFET技术的可靠性和鲁棒性展开,以更好地理解系统设计的权衡,以提高效率和可靠性。

为进行测试,GeneSiC半导体公司在150mm晶圆上制造了1200V/75mΩ SiC DMOSFET。在器件上执行了三种类型的测试程序,如下所述:

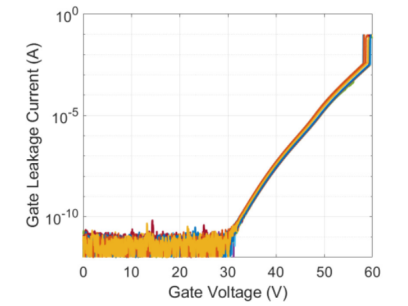

进行了上述不同的实验,并测量了所需的特性(见图1)。栅极偏置温度应力测试表明,在高于30V的栅极电压下观察到Fowler-Nordheim隧穿电流,这提供了高于额定20V的适当安全裕度,而在57-59V之间观察到击穿。栅极特性显示制造时使用了清洁的栅极氧化工艺。在1000小时和175°C下进行了正负栅极偏置温度应力测试,结果显示阈值电压只有很小的偏差,测试前后测量了主要电气特性,发现没有变化。即使在室温下,即使施加高于额定的栅极电压,Vth也能保持相对稳定。

图1:在室温下对10个制造完全的1200V SiC MOSFET测量栅极漏电流和电介质击穿来源:Reliability and robustness performance of 1200 V SiC DMOSFETs

UIS测试显示单脉冲故障前雪崩能量为0.95J(20.7J/cm2),雪崩耐受时间为80μs,如下图所示。雪崩脉冲导致漏极电压增加到1600V,导致高峰值电流,最终导致结温的升高。

对于短路测试,测量半导体器件的不同变化(基于不同的漏极饱和电流额定值ID,SAT)的电压特性并绘制了图形,以查看SC测试前后的变化。据观察,具有较低ID,SAT的器件能够承受较长的短路脉冲。还观察到短路耐受时间与栅极驱动器电压呈现正相关,与RDS(ON)负相关。在600V直流链路电压下测量的短路耐受时间在3-6μs范围内,具体取决于器件额定值。在多个MOSFET器件设计中,观察到软或硬的短路故障模式,并且发现这与漏极饱和电流水平有关。

由GeneSiC开发的1200V/75mΩ MOSFET细致的栅极氧化层的可靠性和鲁棒性特性表明,晶圆代工厂遵循了清洁且良好的氧化工艺。对于175°C下的Fowler-Nordheim隧穿,氧化物击穿场接近理论值11.4MV/cm和势垒高度2.7eV范围也证明了这一点。像GenSiC这样的半导体制造商已经在高功率应用方面取得了长足的进展。

(原文刊登于EDN姊妹网站Power Electronics News,参考链接:Analyzing Robustness and Reliability of High-Voltage SiC MOSFETs,由Ricardo Xie编译。)

最前沿的电子设计资讯

最前沿的电子设计资讯