5月3日,初创公司NEO Semiconductor宣布推出其突破性技术3D X-DRAM,该技术可以生产230层的128Gb(16GB) DRAM芯片,是当前DRAM密度的八倍。这是全球首款类3D NAND DRAM单元阵列,旨在解决DRAM的容量瓶颈,取代整个2D DRAM市场。相关专利申请于2023年4月6日与美国专利申请公布一起公布。

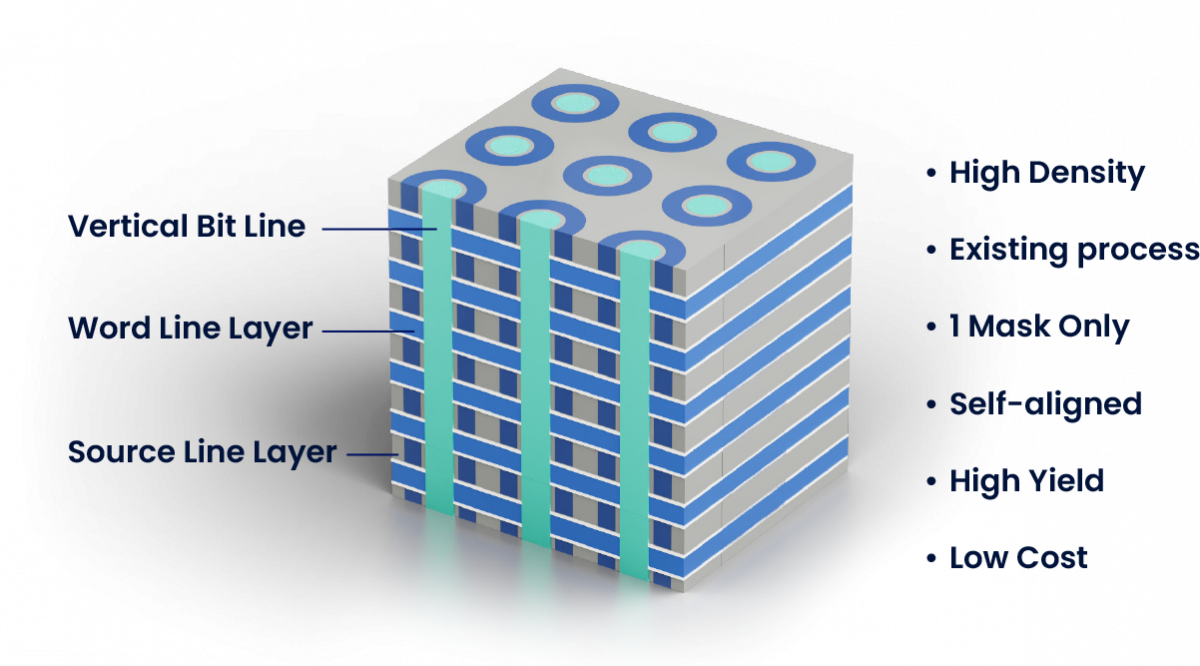

3D X-DRAM阵列结构(来源:NEO)

随着AI技术越来越成熟,训练AI模型所需的大量算力对芯片提出了巨大的挑战,市场对于高算力芯片的需求与日俱增,除此之外,对于更高效运算的达成,当前在内存方面也存在着很大的瓶颈。以DRAM三巨头(三星、SK海力士、美光)工艺尺寸的发展历程来看,三者在2016-2017年进入1X(16nm-19nm)阶段,2018-2019年为1Y(14nm-16nm),2020年处于1Z(12nm-14nm)时代。一直到2022年11月中旬,美光才实现了1β DRAM(第五代10nm级别DRAM)量产,而三星的技术路线图也预计,在2023年才进入1b nm(第五代10nm级别DRAM)工艺阶段。

虽然10nm还不是DRAM的最后极限,但多年来可以很明显的看到DRAM的扩展速度放缓,在工艺完整性、成本、单元泄漏、电容、刷新管理和传感裕度等方面的挑战下,新的DRAM节点也只是缩小很小的一部分。目前,DRAM线宽微缩至10nm,制程能带来的提升已经越来越少,3D DRAM顺势成为了存储厂商迫切想突破DRAM工艺更高极限的新路径。

3D X-DRAM单元结构(来源:NEO)

当前市场上有关于3D DRAM的工艺,主要集中在HBM(High Bandwidth Memory,高带宽存储器)和无电容式IGZO(indium-gallium-zinc-oxide,铟镓锌氧化物)技术上。

2014年,AMD、SK海力士共同开发出了HBM技术,使用TSV(Through Silicon Via,硅穿孔)技术将数个DRAM芯片堆叠在逻辑芯片上面,让HBM存储颗粒与处理器更进一步,做成了2.5D集成,这种方式极大的缩短了存储颗粒与处理器之间的距离。它的好处是容量比较大,带宽也会比较高,功耗比HMC好很多,缺点是成本比较高,互连有一些限制,通常来说,一个处理器只能连4个HBM颗粒。最新的进展是2023年4月20日SK海力士宣布达成的12层堆叠HBM3 DRAM,最高容量为24GB。

而对于无电容式IGZO技术,在2020年的国际电子器件会议(IEDM)上,美国和比利时的独立研究小组IMEC首次展示了一种无电容的动态随机存取存储器(DRAM)单元,实现了两个IGZO薄膜晶体管且没有电容的单元架构。业界普遍认为,无电容IGZO DRAM是实现高密度3D DRAM的合适候选者。

DRAM技术的未来(来源:NEO)

此次NEO所推出的3D X-DRAM也正是一种基于无电容器浮体单元 (FBC) 技术的类3D NAND DRAM单元阵列结构。这种 FBC 技术使用一个晶体管和零个电容器将数据存储为电荷。与当前业内研究的许多将DRAM迁移到3D的替代方案不同的是,这种技术可以使用当前的3D NAND类工艺制造,只需要一个掩模来定义位线孔并在孔内形成单元结构。这提供了一种高速、高密度、低成本和高产量的制造解决方案,极大的加快了3D DRAM的发展进程,很大程度上减轻了行业在未来可能遇到的产量和成本挑战。

“3D X-DRAM 将是半导体行业未来绝对的增长动力。”该公司联合创始人兼首席执行官 Andy Hsu 乐观地表示,“今天我可以自信地说,NEO 正在成为 3D DRAM 市场的明显领导者。与当今市场上的其他解决方案相比,我们的发明非常简单,制造和规模化成本更低。通过我们的 3D X-DRAM,业界有望每十年实现 8 倍的密度和容量提升。”

最前沿的电子设计资讯

最前沿的电子设计资讯