韩媒近日披露了三星为2023年国际VLSI研讨会(6月于日本召开)准备的初步演讲,其内容显示,第二代3纳米工艺晶片的运算速率比当前4纳米工艺快22%、省电效率高34%,晶片尺寸则减少21%。

新信息的发布意义重大,因为这是三星首次将其未来的芯片制造工艺与其主要的 4nm 工艺进行比较。此前,该公司在将其性能与下一代技术进行比较时,将其 5nm 工艺作为基准。

根据三星电子最近在社交媒体上发布的帖子,其 4 纳米工艺的良率现已接近 5 纳米工艺的水平。“下一代 4 纳米工艺将提供更高的产量,”三星电子表示。业内人士表示,芯片制造商罕见地向公众公布其芯片良率的细节。

良率的提高帮助三星电子重新吸引了客户。据业内消息人士透露,美国公司 Advanced Micro Devices Inc. 选择了三星制造 4 纳米处理器。三星电子还将使用其第三代 4 纳米工艺为谷歌的 Pixel 8 智能手机制造 Tensor 3 芯片。

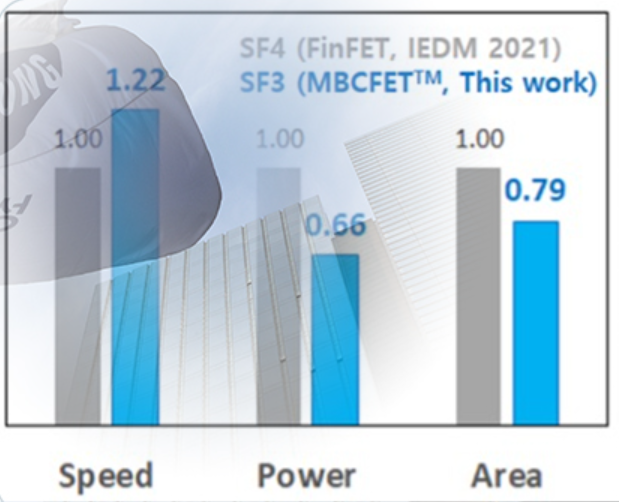

三星在去年 6 月首次开始生产其第一代 3nm 工艺时,声称与 5nm 工艺相比,芯片性能提高了 23%,芯片尺寸缩小了 16%。

台积电最近才公布,第二代3纳米工艺的效能比5纳米(N5)高18%、省电效率多32%。一般认为,台积电N5工艺跟三星SF4工艺相似或较低。

最前沿的电子设计资讯

最前沿的电子设计资讯