氮化镓(GaN)高电子迁移率晶体管(HEMT)由于其优于传统硅基晶体管的卓越性能,在电子领域越来越受欢迎。GaN HEMT可以在更高的开关频率下运行,从而使业界能够减小系统中使用的电子设备的尺寸。卓越的热性能有助于它们用于高功率应用,例如电动汽车的动力总成、传输线和电机驱动。

GaN HEMT需要在众多应用中并联,以提高功率容量和运行效率。但并联它们也带来了挑战,例如开关之间的损耗分布不平衡,这可能导致温度升高到安全限值以上。要并联任意两个开关,开关的导通电阻(RDS(on))需要精确匹配,以确保开关之间的负载均匀分布。任何不平衡都可能导致开关之间的高频振荡,进而导致开关损坏。

对于GaN HEMT,与硅MOSFET相比更高的开关频率给研究人员并联这些开关带来了更大的挑战。由于运行速度超快,GaN HEMT对电路寄生效应非常敏感,这些开关之间的任何不平衡都可能导致效率损失并增加开关损坏的可能性。各种研究证明,可以在不减慢GaN HEMT或降低其额定值的情况下实现可靠的硬导通和硬关断转换。

并联GaN HEMT时的另一个重要参数是确保准确的损耗分布。本文着眼于损耗的类型以及确保对并联GaN HEMT中的损耗分布进行正确的监测和分析的方法。原文可在此处阅读。

测量硅MOSFET和IGBT损耗的方法已经得到很好的发展,但随着行业对更快、更高效器件的需求,焦点现在已经转移到GaN等宽禁带器件上。就像硅基器件一样,GaN中的损耗可分为两类:静态或传导损耗和开关损耗。尽管分类相似,但仔细观察就会发现,GaN的损耗分布与硅MOSFET的损耗分布不同。

对于GaN HEMT,静态或传导损耗包括25°C时的RDS(on)损耗、热效应引起的RDS(on)损耗、俘获效应(也称为动态RDS(on)损耗)引起的RDS(on)损耗和死区时间损耗。开关损耗包括导通/关断的V-I重叠损耗和Eqoss以及Eoss损耗。在非常高的工作频率下观察到的另一种损耗是Coss电容滞后损耗,在用于射频范围的应用要考虑。V-I重叠损耗是由开关工作期间电流和电压的重叠引起的。EOSS是电容充电损耗,即在为开关的寄生电容充电时损失的能量。Eqoss是由于HEMT半桥配置中相对开关的电容器充电电流引起的损耗。

虽然已经对静态损耗对HEMT并联的影响进行了大量研究,但本文重点评估在高压和高频应用中可能与静态损耗一样高的开关损耗。

分段线性模型是分析和估算晶体管损耗的最流行模型之一。该模型仅从输入电容和外部栅极电阻的角度考虑电路,而忽略了寄生参数和温度相关性。因此,它不能用于分析并联GaN配置中的开关损耗。许多研究人员致力于修改分段线性模型以考虑电路中的更多动态。为了有效地监测开关损耗,分段线性模型已被修改来包含寄生元件和同步晶体管的影响。

为了解温度对损耗的影响,绘制了阈值电压和跨导随GS66516B GaN HEMT并联结温变化的曲线图。观察到阈值电压随温度变化几乎是恒定的,但跨导对温度有负相关性。这导致了一种自动结温平衡机制:当结温升高时,开关损耗会显着降低。在并联硅基MOSFET中,与GaN不同,开关损耗会随着结温的升高而增加,这会导致温度分布不平衡甚至热失控。

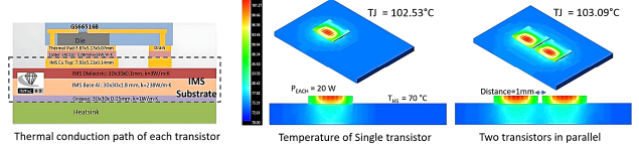

为了通过实验验证上述自动结温平衡机制,测量并联GaN HEMT的结温。该实验是使用240A/650V半桥功率模块进行的,该模块具有使用随机选择的GaN HEMT构建的IMS衬底。电路在不同开关频率下的全功率仿真显示并联GaN HEMT具有出色的结温平衡。

IMS衬底上GaN HEMT的热有限元分析仿真结果(来源:IEEE)

(原文刊登于EDN姊妹网站Power Electronics News,参考链接:Loss Distribution Among Paralleled GaN HEMTs,由Ricardo Xie编译。)

最前沿的电子设计资讯

最前沿的电子设计资讯