氮化镓(GaN)高电子迁移率晶体管(HEMT)工作在较高开关频率下,能够提供现代USB-C适配器和充电器设计所需的高功率密度。本文将讨论使用分立或完全集成式GaN HEMT实现USB Type-C功率传输(PD)设计中常见拓扑架构的可选方法,还将介绍集成开关控制器(在适用的拓扑架构场景下)的优点。

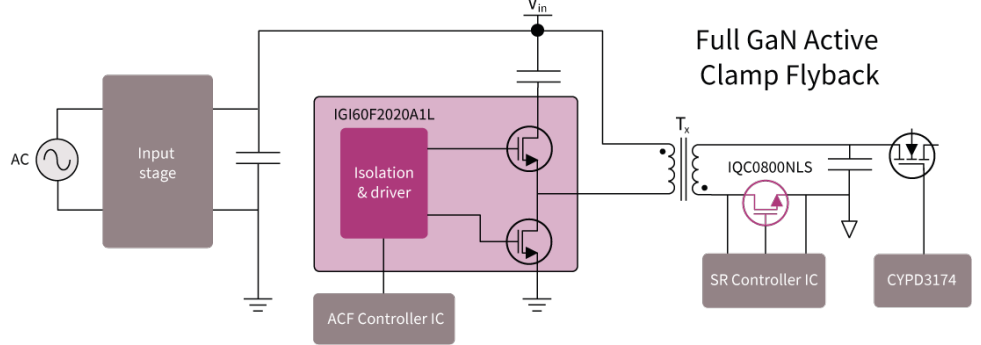

有源箝位反激(ACF)转换器(参见图1)是一种流行的反激拓扑架构,可实现功率器件的零电压开关(ZVS)。由于ZVS操作和反激电阻器-电容器-二极管(RCD)箝位耗散的变压器漏电感能量能够完全恢复,这种拓扑架构适用于比准谐振反激更高的频率操作。通过箝位电容器(与ZVS相结合)箝位主开关电压意味着ACF拓扑架构可提供良好的电磁干扰(EMI)性能。这里有两种ACF控制方案:互补(CP)型和非互补(NCP)型。在CP模式下,主反激开关和箝位开关在每个开关周期中以互补方式接通和断开,因此变压器电流波形具有近似正弦的形状。主反激开关和箝位开关在ZVS开关下工作,开关频率随着负载降低而提高,这会影响轻负载和待机模式下的效率,也会影响EMI。此外,谐振回路中的总谐振电流会导致变压器中的传导损耗增加,而NCP ACF可以用来克服这两个问题。在这种模式下,有源箝位开关仅接通足够的磁能以维持主开关中的ZVS。通过这种方式,循环箝位电容器电流得到了缓解。

图1:有源反激变换器拓扑架构的分立式实现方案。

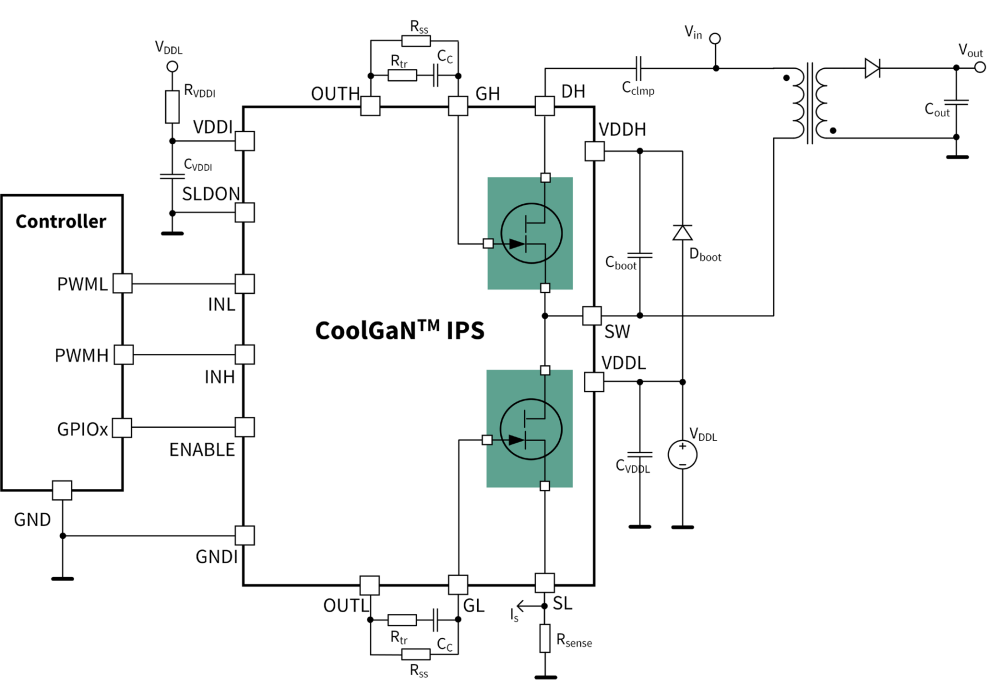

图2所示为使用CoolGaN™集成功率级(IPS)实现的有源箝位反激(ACF)方案。在这里,当主开关断开,箝位开关导通时,钳位开关提供了一条路径来恢复存储在变压器漏电感(Llk)中的能量。因此,Cclmp和Llk通过箝位开关和变压器达到谐振,从而将能量传递到负载。与无源箝位反激相比,这种能量回收提高了系统效率,其中能量存储在传统RCD箝位电路中的Llk阻尼中。

图2:使用IPS实现的有源反激转换器拓扑架构。

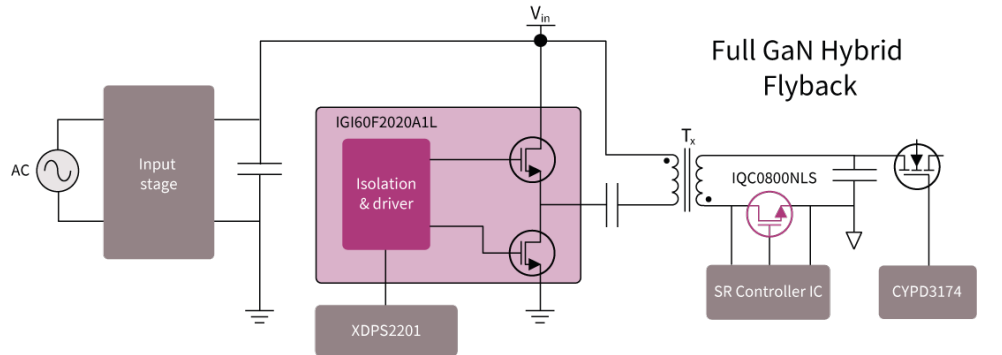

混合反激式(HFB)转换器(参见图3)是另一种谐振拓扑架构,它不仅使用ZVS,还使用零电流开关(ZCS)。初级侧转换器具有谐振型电流波形,这意味着由于具有较低RMS电流的ZVS操作,可以实现高频、高效率。此外,谐振电容器的容量有助于能量存储,因而变压器的尺寸可以比其他反激式拓扑架构更小。由于在初级侧具有自身电压(self-voltage)箝位到Vbus的半桥架构,开关器件上的电压应力比ACF拓扑更好。与QR反激相比,HFB在初级侧有一个额外开关,由于谐振型操作的循环电流,这需要特别注意轻负载效率。对于通用型电压输入规范,需要仔细设计,并且HFB所需的控制复杂度远高于QR反激拓扑架构。然而,英飞凌的XDP™ 数字电源XDPS2201控制器通过专用的控制算法,极大地简化了这项任务。

图3:采用XDPS2201控制器的混合反激拓扑架构分立式实现。

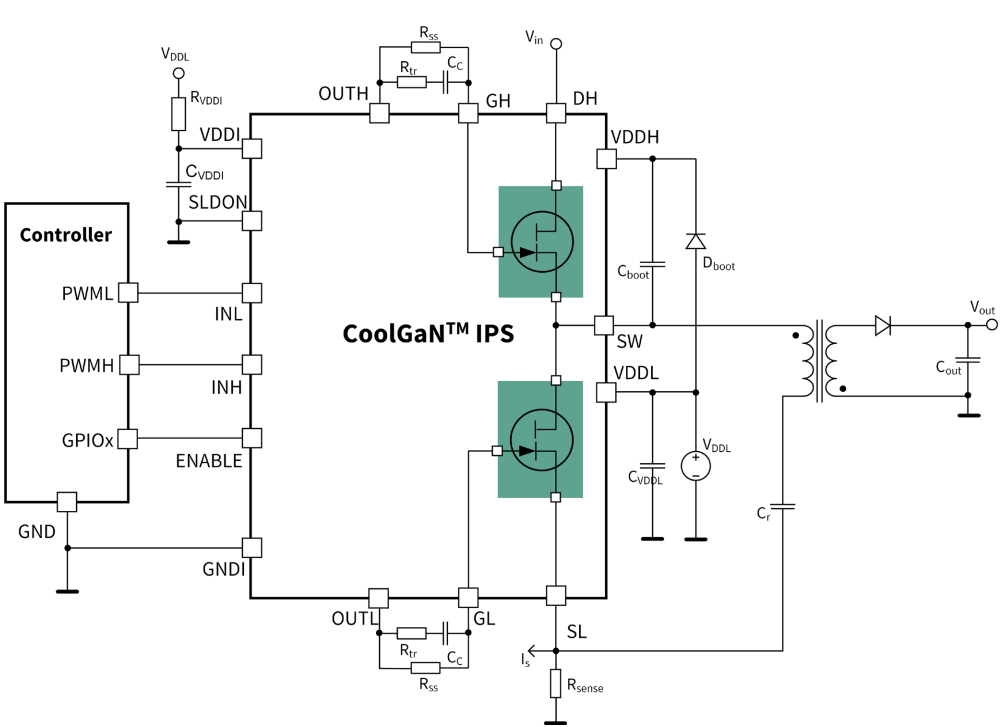

图4所示为带有CoolGaN™ IPS的混合式反激转换器(HFB)拓扑架构。转换器由高侧和低侧开关、变压器、谐振回路(Llk和Cr)、输出级整流器和电容器等组成。采用非互补开关模式的高级控制技术能够提供一种支持宽范围交流输入和直流输出电压的解决方案,这是通用USB-C PD操作所必需的。当高侧开关接通时,混合反激转换器将能量存储在初级侧电感器中。在低侧开关导通时,存储在初级侧电感器中的能量会转移到输出。在两个开关的转换过程中,通过进行适当的时序控制,HFB可使两个器件在ZVS下运行,确保了系统高效率,而不需要额外的组件。这两个器件都受益于ZVS和更高的效率(来自次级ZCS操作),使混合反激成为USB-PD快速充电器等超高功率密度转换器具有成本竞争力的解决方案。

图4:采用IPS实现的一种混合式反激拓扑架构。

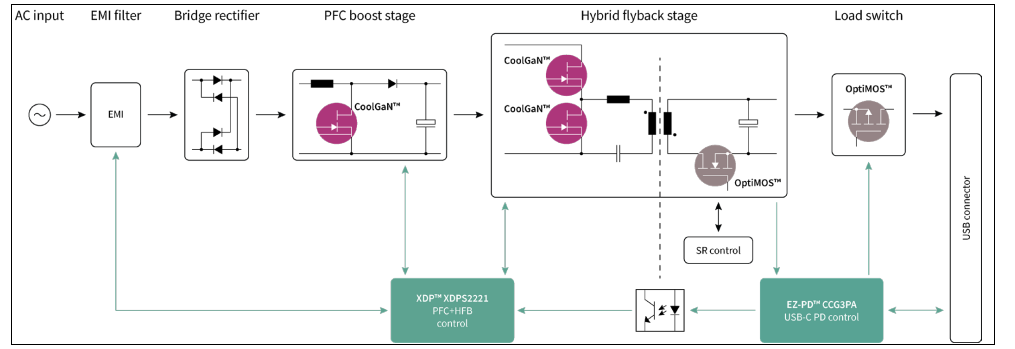

满足扩展功率范围(EPR)标准的USB-PD可提供高达240W的更高功率水平,为广泛用于多种不同场景的通用AC-DC适配器铺平了道路,能够完成为各种终端设备充电,包括从智能手机到游戏笔记本电脑,从电动工具,甚至电动自行车。然而,在电磁兼容性、功率因数校正、待机功率和平均效率等方面有具体要求,对当今使用的转换器拓扑架构提出了新的挑战。与此同时,尺寸和功率密度已经成为各种应用中越来越重要的要求。更宽的输出电压范围(从5V到48V)对现有的转换器拓扑架构也提出了全新挑战,因此将AC-DC功率因数校正(PFC)升压转换器与DC-DC混合反激(HFB)级相结合,为具有宽输入和输出电压范围的USB-PD充电器和适配器提供了最合适的技术组合(图5)。

图5 :针对USB-PD扩展功率范围的电源架构。

这种架构通过使用创新的控制器,既可提供高功率密度,又可实现高效率(满足欧盟CoC版本5 Tier 2和DoE Level VI等国际监管标准)。此外,该架构还支持在最新的USB-PD标准中对宽输出电压进行有效控制。与传统反激式拓扑架构相比,可以使用体积更小的变压器。

XDP™ XDPS2221将AC-DC功率因数校正控制器与DC-DC混合反激控制器(HFB)(也称为不对称半桥(AHB))集成在一个单独封装内,并凭借这两个过程的协调操作,能够满足监管方面的要求。通过集成所有栅极驱动器、用于初始IC电压供电的600V高压启动单元、以及经认证的有源X电容器放电,可减少外部组件数量以及材料清单(BOM)。该控制器基于新型零电压开关(ZVS)HFB拓扑架构(基于GaN器件),能够在广泛的线路和负载条件下实现无与伦比的效率。这些特征,再加上其固有的拓扑架构优势(如零电压开关和用于减小变压器尺寸的谐振能量转移),意味着使用XDP™ XDPS2221的系统设计可以实现极高功率密度。这种新的组合式控制器IC还可实现同步PFC和HFB突发模式操作,以提供尽可能低的空载输入待机功率。此外,透过自动PFC启用/禁用功能和自适应PFC总线电压控制,准谐振多模PFC级也得到加强,能够最大限度地提高平均和轻负载效率。作为一种可选项,集成PFC功能也可以被禁用以支持外部PFC控制器。混合反激阶段使用峰值电流来控制操作,能够实现可靠调节和快速动态负载响应。对于所有条件下的ZVS操作,混合反激都具有ZVS脉冲插入功能,包括在非连续导通模式下防止体二极管跨导(cross-conduction)。

当今的USB-PD适配器和充电器(包括满足扩展功率范围的适配器和充电器)需要以尽可能小的外形尺寸提供更高的性能,本文介绍了基于英飞凌氮化镓HEMT和开关控制器的各种拓扑架构,这些解决方案可用于满足上述要求。

欲了解有关CoolGaN™集成功率级的更多信息,请点击此处。若需查找XDP™ XDPS2221等产品详细信息,请点击此处。

最前沿的电子设计资讯

最前沿的电子设计资讯