台积电(TSMC)的3纳米(nm)制程节点象征最后一代基于FinFET制造的制程技术,因为该代工厂的2nm制程节点将采用纳米片(nanosheet),或称为环绕式栅极(GAA)晶体管。全球代工巨擘台积电在日前举行的2023年北美技术论坛(2023 North America Technology Symposium)中提供关于3nm芯片制程节点的最新信息,并为2nm节点增加两个变化版本,英特尔能否迎头赶上?。

关于目前正生产中的基准3nm节点N3,以及将于2023年下半年推出的增强版N3E的细节,已于去年公布。N3节点配备多达25个极紫外光(EUV)层,同时在其中一些层上使用双重图案,以促进比台积电N5制程节点更高的逻辑和SRAM晶体管密度。

另一方面,N3E利用多达19层EUV,而且无需仰赖EUV双重图案,从而降低了制造的复杂性和成本。然而,虽然N3E提供了更宽的制程窗口和更好的产量,但它所提供的逻辑密度比N3低。因此,它对于旨在提高密度和面积的芯片设计的吸引力较小。

现在,台积电正为其N3开发蓝图增加新的变化版本,以进一步丰富3nm制程技术,从而满足芯片设计者的不同需求。以下简要概述台积电在加州圣克拉拉举行技术论坛中所发布的三个节点: N3P、N3X和N3AE。

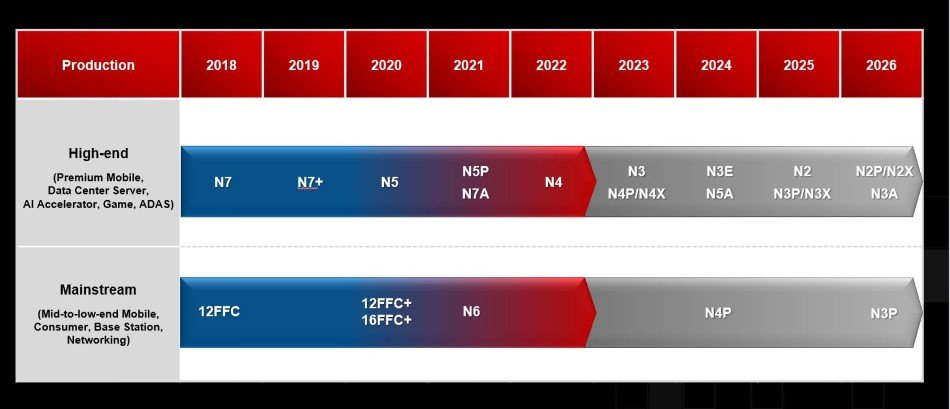

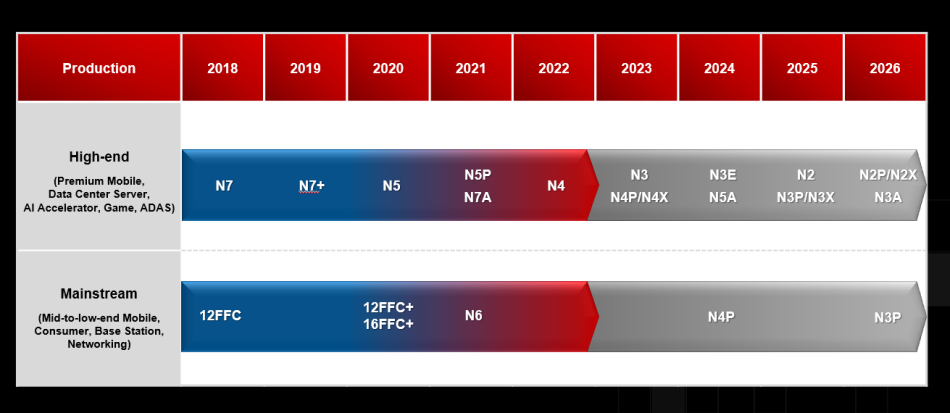

图1:3nm制造节点可分为一系列多样化的制程节点,以满足各种芯片需求。(来源:TSMC)

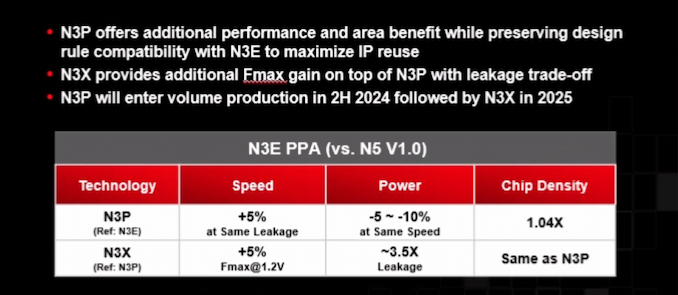

N3P是对N3E的改进版本,透过调整其扫描仪的光学性能,从而降低功耗、增强性能和密度。换句话说,它是N3E的光学微缩版,在相同的漏电情况下提供5%的速度,在相同的速度下降低5-10%的功率以及更高1.04倍的芯片密度。

N3P的关键目标在于透过在N3E的基础上改进晶体管特性,从而优化晶体管密度。台积电声称,对于混合芯片设计来说,这种3nm将使晶体管密度提高4%。这种混合芯片一般是由50%的逻辑、30%的SRAM和20%的模拟电路组成。N3P预计成为台积电最受欢迎的N3节点之一,预计将于2024年下半年推出。

N3X是为CPU和GPU等高性能运算(HPC)装置量身打造的,提供比N3P高至少5%的频率速度。虽然能够承受更高电压,但该节点使IC设计者能够提高频率速度,以换取更高的整体泄漏。据台积电表示,N3X将支持约1.2V的电压,这对3nm芯片制造制程来说是相当高的。

N3X专为高性能运算(HPC)处理器量身打造,是聚焦于性能的先进制程节点。漏电并不是HPC处理器最重要的关注点。这些处理器通常用于服务器级的硬件,并具有强大的冷却系统。尽管如此,芯片设计者也必须致力于控制这些耗电的处理器。

同样值得注意的是,N3X将提供与N3P相同的晶体管密度,其关键的价值主张是为HPC应用优先考虑性能和最高频率频率。据台积电消息来源表示,N3X将在2025年量产。根据业界消息来源,英特尔(Intel)的Celestial GPU将是首批使用N3X制造节点的产品之一。

图2:N3P和N3X节点分别在芯片密度和更高电压容限方面提供多样化制程。(来源:TSMC)

N3AE或 “Auto Early “在先进的芯片制程技术上实现了汽车应用。它提供基于N3E的汽车工艺制程设计套件(PDK),并将于2023年推出。完全符合汽车标准的N3AE制程将在2025年量产。

台积电在2023年北美技术论坛上并提供了2nm芯片制程(N2)细节,N2有望在2025年投产。台积电并将在2026年为其N2技术增加两个变化版本:具有背面供电的N2P和用于HPC的N2X。

N2及其变化版本将是台积电第一个采用GAA晶体管——台积电称之为纳米片(nanosheet)晶体管的制造节点,以提高逻辑、SRAM和模拟电路的性能、能源效率和晶体管密度。GAA技术有利于降低漏电电流,因为通道的四面都由栅极环绕。此外,GAA晶体管提高了调整通道宽度的能力,以获得更高的性能或更低的功耗。

图1 :两种N2变化版本是今年技术论坛最值得关注的亮点之一。(来源:TSMC)

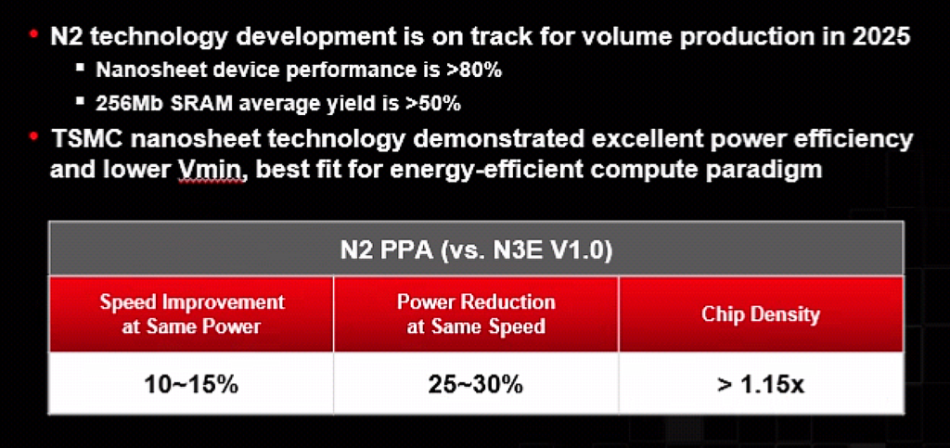

在今年的技术论坛上,台积电声称其新的纳米片晶体管已能满足80%的目标性能规格,而256-Mb SRAM的平均良率目前达50%以上,而台积电也还有两年时间来提高这些数字。

据台积电称,N2将在与N3相同的功率下提供10%至15%的性能,或在相同的频率下降低25%至20%的功率。台积电并声称,对于混合芯片—包括逻辑、SRAM和模拟—N2将比N3E实现更高15%的密度。

图2:今年的台积电技术论坛主要提供关于去年宣布的N2制程节点细节。(来源:TSMC)

虽然关于台积电N2技术的细节已经流传一段时间了,但此次技术论坛上针对N2制造节点宣布了两个新版本,将这一先进制造技术延伸到2026年。台积电在2020年开始研究2nm芯片制造制程,过去几年来也持续不懈地追求这一尖端的芯片制造技术。

关于N2制程节点的变化版——N2P和N2X,预计将在2026年投产,而在采用这些节点制造的芯片可望在2027年出现。

不久前,当台积电宣布采用纳米片设计的N2生产计划时,即宣誓要在未来的版本中晶背供电源技术;该2nm制程版本被命名为N2P。它就像英特尔的PowerVia和三星的BSPDN制程技术一样,将晶体管夹在电源传输网络和讯号网络之间,以提高晶体管性能并降低功耗。

晶背供电技术将电源轨移到芯片背面以解耦I/O和电源布线,解决了诸如后端制程(BEOL)通孔电阻升高的挑战。因此,当芯片制造商持续致力于芯片供电传输电路中的电阻问题时,晶背供电传输增强了晶体管的性能、降低其功耗,并消除了数据和电源连接之间的一些潜在干扰。

据应用材料(Applied Materials)估计,晶背供电技术让逻辑单元面积减少20%至30%。尽管台积电并未提供关于N2P技术的任何细节,但发表在AnandTech上的一份报告声称,晶背供电轨可以实现两位数的晶体管密度改进以及个位数的效率提升。

台积电也在准备N2X,这是针对HPC装置的制程,如高阶CPU和GPU等HPC需要更高的电压和频率速度。N2X将在N2P之后出现,因此关于这种用于HPC应用的N2变化版的信息目前还很有限。

值得一提的是,英特尔在其20A制程上的2nm制造制程也遵循类似的发展轨迹,即采用了晶背供电技术。英特尔计划在2024年底将其2nm PowerVia制程节点推向量产,如果这家位于加州圣克拉拉的芯片制造商能够成功执行这一计划,它将在实施晶背供电传输的竞赛中超前台积电近两年。

然而,考虑到英特尔在执行先进制程节点方面的发展记录,以及其于获得ASML最新的EUV微影设备方面的挑战,能不能做到这一点仍有待观察。尽管如此,除了三星,台积电在纳米竞赛中也出现了第二家竞争对手。

(原文发表于ASPENCORE旗下EDN美国版,参考链接:TSMC upends 3-nm roadmap with three new nodes;TSMC adds two variants to 2-nm node, will Intel catch up?,by Majeed Ahmad;编译:Susan Hong )

最前沿的电子设计资讯

最前沿的电子设计资讯