近日,在比利时安特卫普举行的 ITF World 2023大会上,英特尔技术开发总经理 Ann Kelleher 介绍了几个关键领域最新技术发展,其中就包括了英特尔将采用堆叠式 CFET 晶体管架构,这也是英特尔首次公开介绍新的晶体管设计。

图片来源:ITF World 2023

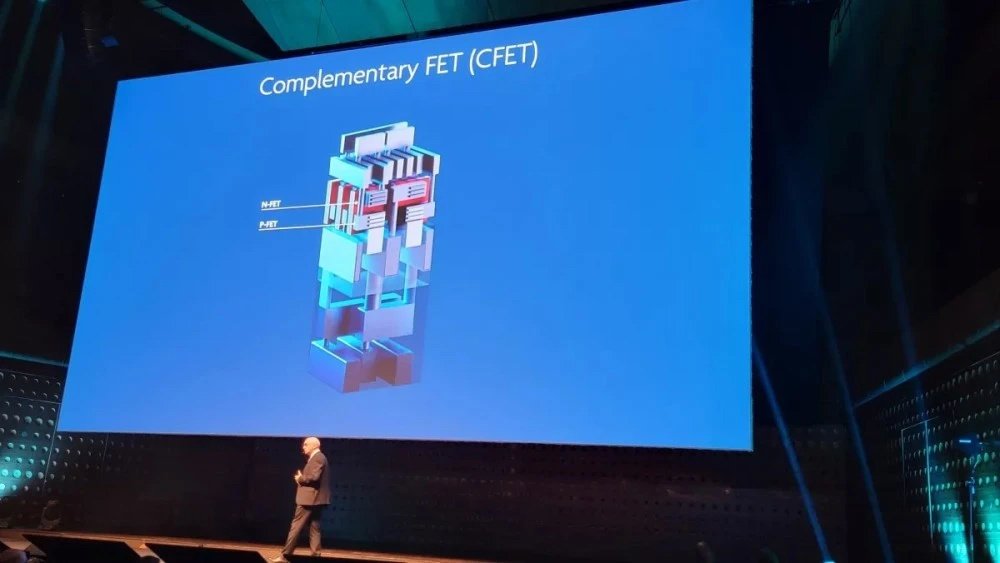

据了解,CFET(互补场效应晶体管),是一种新型的三维结构晶体管工艺,是在GAAFET工艺基础上改进得到,可理解为将两个独立的、具有不同导电沟道的GAAFET(p型和n型)在垂直方向上进行三维叠加,从而突破二维晶体管的性能与尺寸限制。该技术被认为是用于2nm、3nm芯片制造的GAAFET工艺的“接班人”,如果能够与芯粒技术结合应用,就能够有效解决芯片制造的成本问题。

图片来源:ITF World 2023

当前,CFET制造工艺包括单片(monolithic)与顺序(sequential)两种。单片CFET先生长底部通道,然后沉积中间牺牲层,最后生长顶部沟道;顺序CFET是从底部向上制造元件,利用晶圆键合技术,在顶部覆盖一层半导体层,对顶部元件进行集成,并连接顶栅和底栅。对比来看,两种产品各有优缺点,单片CFET整合流程复杂,但成本较低,顺序CFET整合流程相对简单,但晶圆转移难度高。

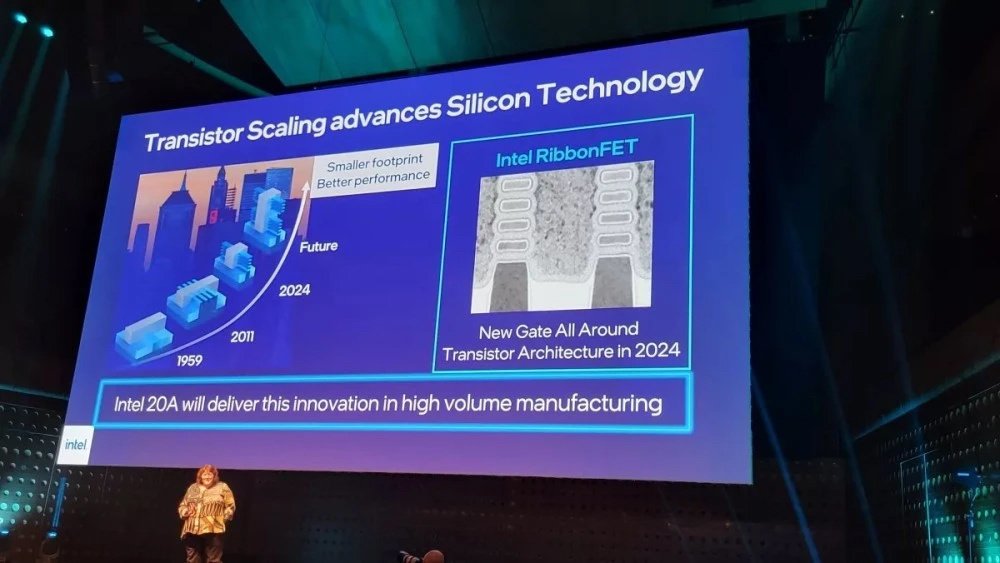

英特尔此次在大会上所展示的GAA堆叠式CFET晶体管架构,允许堆叠8个纳米片,是此前Intel 20A制程技术中引入的RibbonFET晶体管架构的4个纳米片的两倍,进一步增加了晶体管的密度。目前,英特尔正在研究两种CFET晶体管,即单片式和顺序式,但未确定最后采用哪种 CFET晶体管,或还有其他类设计出现。

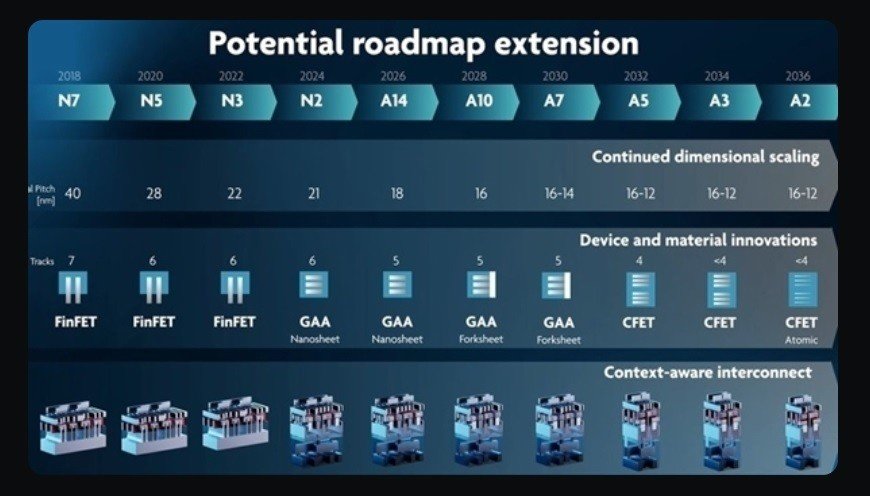

英特尔表示,凭借CFET晶体管技术,2032年将有望进化到5埃米(0.5nm),2036年将有望实现2埃米(0.2nm),CFET晶体管架构类型还会发生变化,也是不可避免的。不过,英特尔只是概述电晶体技术大概发展蓝图,并没有分享太多细节,也没有提及具体的量产时间表。

最前沿的电子设计资讯

最前沿的电子设计资讯