“异或”逻辑器件广泛应用于各种数字电路中。然而,在某些情况下,例如,当使用更高的工作电压时,使用标准芯片是不可能的。这个问题可以通过使用分立器件来解决。

如果标准的与逻辑或或逻辑器件可以很容易地用二极管电阻电路来取代,那么异或器件的情况就复杂得多。值得注意的是,3异或逻辑门并非由工业制造。下面将展示如何从一组标准的分立器件中合成2异或和3异或器件。

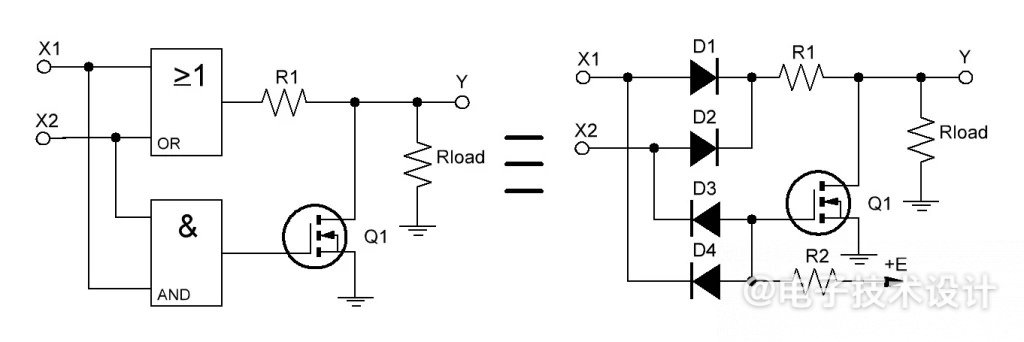

图1显示了如何从2或和2与逻辑器件以及VT1晶体管的组合中合成2异或器件。相应地,2或和2与器件可以用分立器件中的对应器件替换。例如,二极管D1和D2,以及电阻器R1和Rload(Rload>>R1),相当于一个2或逻辑器件。二极管D3和D4,以及电阻器R2,则相当于一个2与逻辑器件。

图1:异或逻辑器件及其使用分立器件的模拟设计。

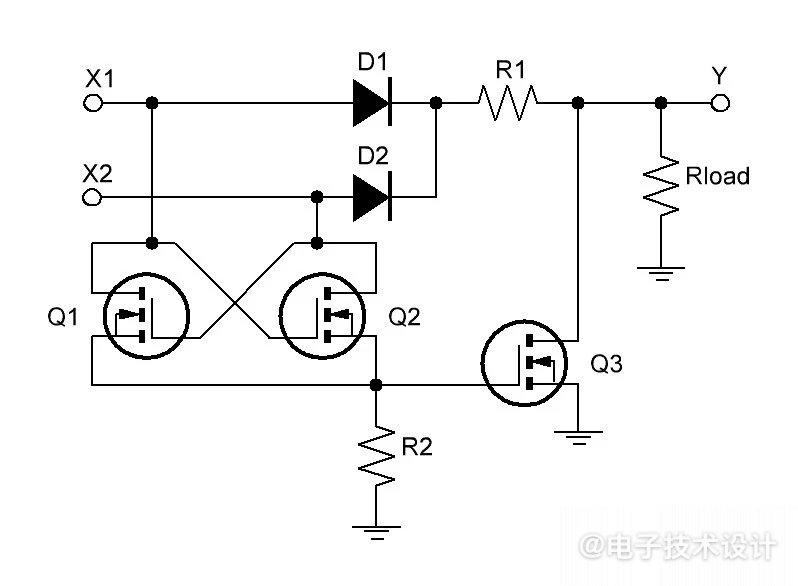

2异或器件的第二种变体如图2所示。晶体管Q1和Q2以及电阻器R2用于实现2与器件。

图2:由分立器件组成的异或逻辑器件。

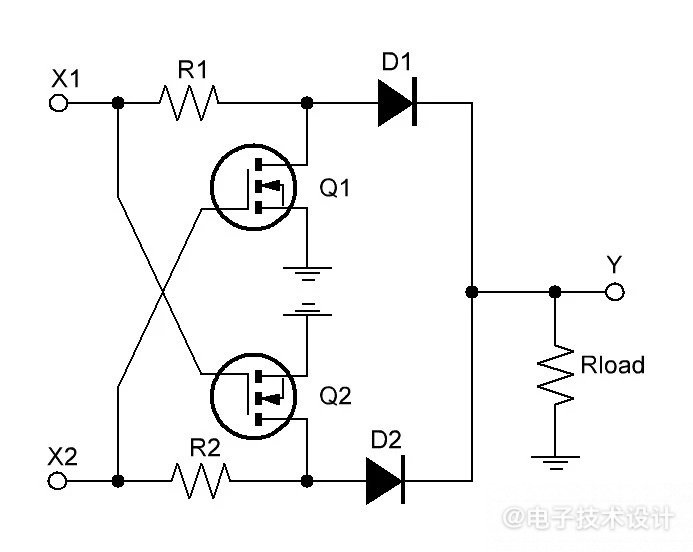

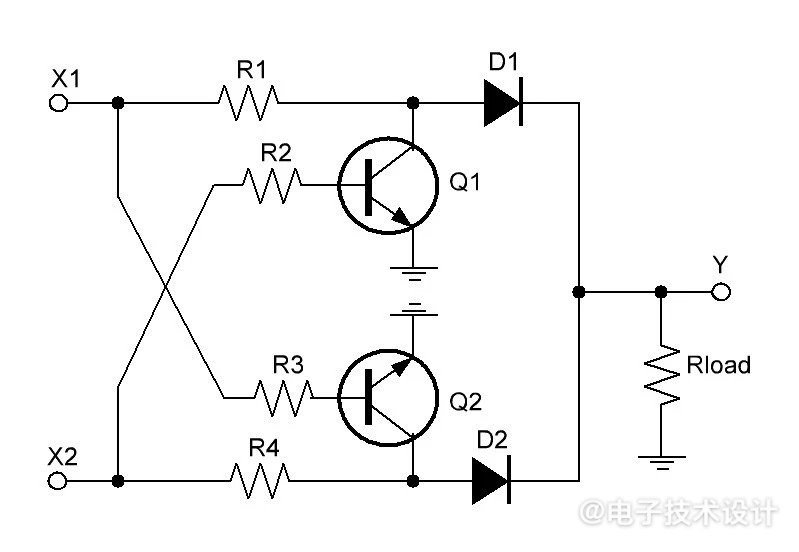

图3和图4给出的2异或逻辑器件的模拟电路变体,分别是基于场效应晶体管(图3)和双极晶体管(图4)制作的。

图3:基于场效应晶体管的2异或逻辑器件。

图4:基于双极晶体管的2异或逻辑器件。

显然,如果“Log. 0”电平出现在输入X1和X2,“Log. 0”也将在电路的输出端被观察到。

当将“Log. 1”电平信号施加到其输入之一(例如X1),并将“Log. 0”电平信号施加到输入端X2时,该信号将通过电阻R1和二极管D1到达电路的输出Y。当然,输出电压会略低于输入电压,这在大多数情况下对数字器件的运行并不重要,尤其是在高压区域工作。

当将“Log. 1”电平信号施加到输入X2,将“Log. 0”电平信号施加到输入X1时,情况类似。

如果将“Log. 1”信号施加到电路的两个输入端,晶体管Q1和Q2都将打开并禁止输入信号通过电路的输出端。

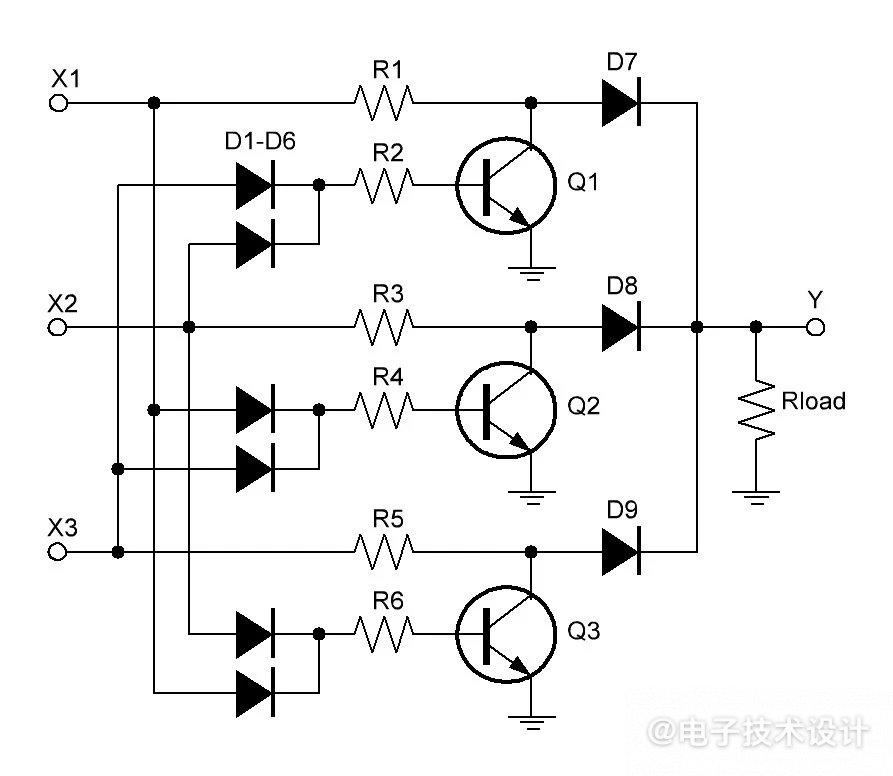

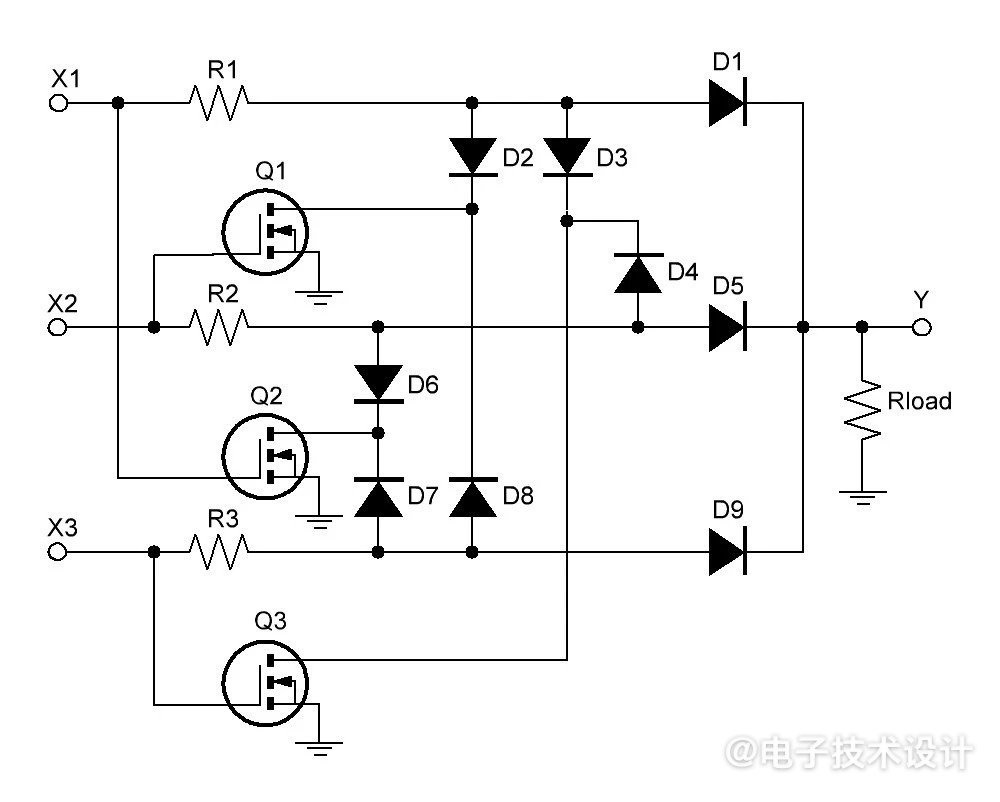

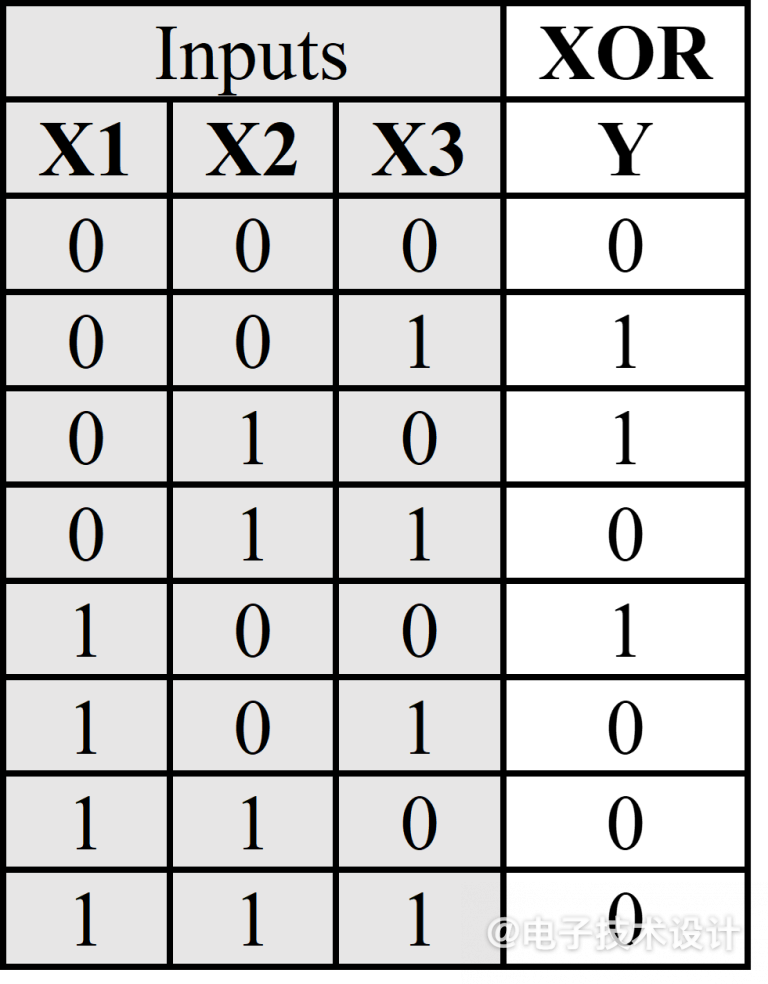

3异或逻辑器件的模拟实现见图5和图6,它们比以前的要复杂得多,但值得考虑的是,由于执行的复杂性增加或出于其他原因,这些微电路形式的器件没有生产。表1(真值表)根据输入信号组合对3异或逻辑器件的输出信号电平进行了表征。

图5:基于双极晶体管的3异或逻辑器件。

图6:基于场效应晶体管的3异或逻辑器件。

表1:3异或逻辑器件的真值表。

Michael A. Shustov是一名技术科学博士和化学科学学位攻读者,在电子、化学、物理、地质学、医学和历史领域发表了750多篇杂志文章。

(原文刊登于EDN美国版,参考链接:Simple XOR logic elements on transistors,由Franklin Zhao编译。)

本文为《电子技术设计》2023年7月刊杂志文章,版权所有,禁止转载。免费杂志订阅申请点击这里。

最前沿的电子设计资讯

最前沿的电子设计资讯