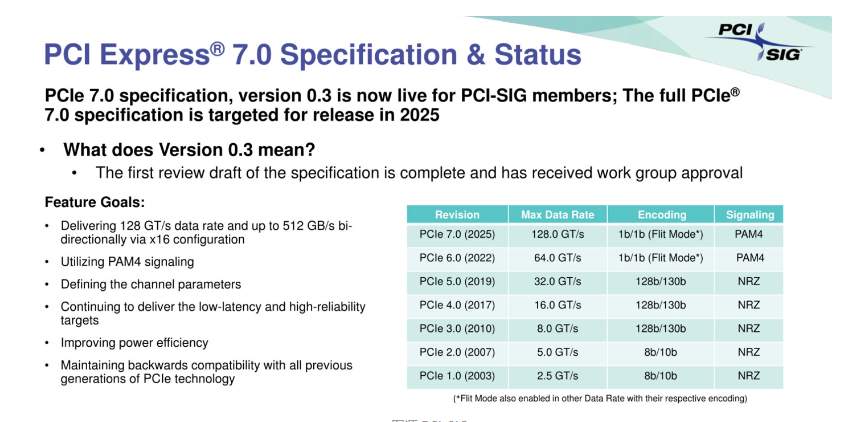

近日PCI-SIG发布PCIe 7.0规范的0.3版本,也就是标准的首个预览版本。这标志着PCIe 7.0规范的新成就,表明PCI-SIG组织成员已经就即将推出的技术的关键特征和架构达成了一致。

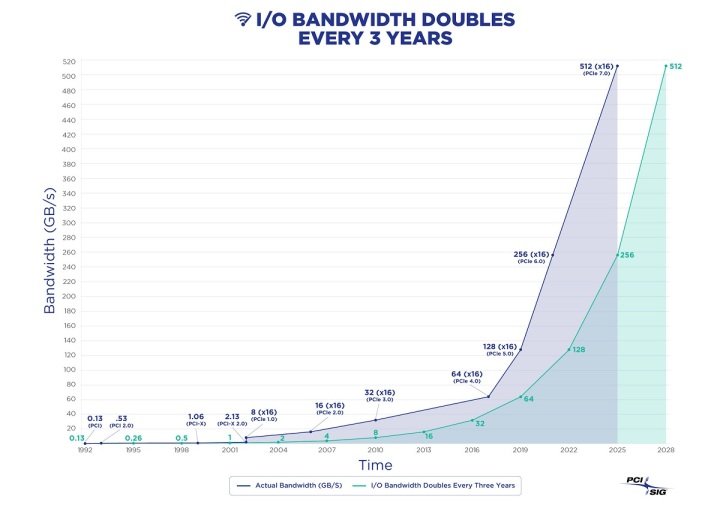

从公布的内容来看,PCIe 7.0规范的数据传输速率将再次倍增,达到128 GT/s,大幅度高于PCIe 6.0的64 GT/s和PCIe 5.0的32 GT/s。意味着单个PCIe 7.0 x16通道可以支持512 GB/s,使用了四级脉冲幅度调制(PAM4)信令和1b/1b flit模式编码和前向纠错(FEC),这些都延用了之前PCIe 6.0规范的功能。

就像PCI-SIG设计的其他规范一样,每个PCI Express规范都会有五个主要的节点。其中PCIe 7.0正处于最早期的0.3版本,即仅仅确定了概念,描述了需要实现的目标和实现这些目标的方法。

据了解,PCIe 7.0规范需要更短的PCIe走线,这使得根设备和端点设备之间的距离进一步缩短。目前要实现PCIe 5.0的设计,需要更厚的PCB和更高质量的用料,也就是说成本提高了,暂时还不清楚PCIe 7.0对于这方面的考虑。

PCI-SIG总裁Al Yanes表示:“PCI Express技术作为基础I/O互连在行业中处于领先地位,从汽车到数据中心服务器,无所不在。随着PCIe架构速度的提高,我们将继续扩展我们的传统垂直领域,同时扩展到令人兴奋的新垂直领域,以满足对高带宽、低延迟互连的需求。”

最前沿的电子设计资讯

最前沿的电子设计资讯