据东京工业大学的研究人员报道,一种用于处理单元和内存的三维集成技术已经实现了全世界可达到的最高性能,为更快、更高效的计算铺平了道路。这种创新的堆叠架构被命名为“BBCube 3D”,它实现了比最先进的内存技术更高的数据带宽,同时还最大限度地减少了能耗。

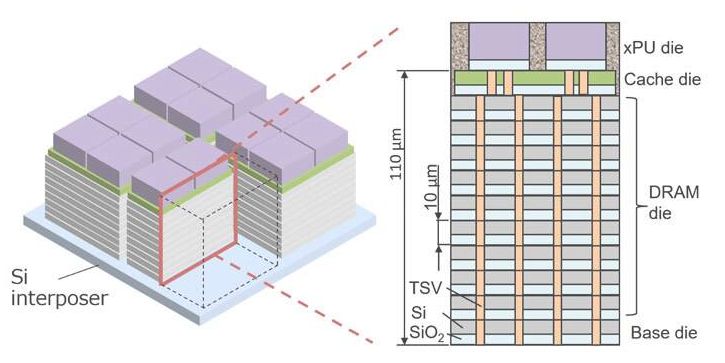

图1:采用堆叠设计,其中处理单元 (xPU) 位于多个互连内存层 (DRAM) 之上。通过用硅通孔 (TSV) 代替电线,可以缩短连接长度,从而获得更好的整体电气性能。图片来源:东京工业大学

在当今的数字时代,工程师和研究人员不断提出新的计算机辅助技术,这些技术需要处理单元(或PU,例如GPU和CPU)与存储芯片之间更高的数据带宽。现代带宽密集型应用的一些例子包括人工智能、分子模拟、气候预测和遗传分析。

然而,为了增加数据带宽,必须在 PU 和存储器之间添加更多线路,或者提高数据速率。第一种方法在实践中很难实现,因为上述组件之间的传输通常发生在两个维度上,使得添加更多电线变得棘手。另一方面,提高数据速率需要增加每次访问一个比特所需的能量,称为“比特访问能量”,这也是具有挑战性的。

据悉,日本东京工业大学(Tokyo Tech)的一组研究人员现在可能已经找到了解决这个问题的可行方案。

在最近举行的IEEE 2023 VLSI 技术和电路研究研讨会上,Takayuki Ohba教授及其同事提出了一种名为“Bumpless Build Cube 3D”或BBCube 3D的技术。该技术有可能解决上述问题,从而更好地集成PU和动态随机存取存储器 (DRAM)。

顾名思义,BBCube 3D最引人注目的方面是实现了PU和DRAM之间的三维连接,而不是二维。该团队通过使用创新的堆叠结构实现了这一壮举,其中 PU 芯片位于多层 DRAM 之上,所有层均通过硅通孔 (TSV) 互连。

BBCube 3D 的整体结构紧凑、没有典型的焊料微凸块以及使用 TSV 代替较长的电线,共同有助于实现低寄生电容和低电阻。在各方面改善了该器件的电气性能。

此外,研究人员实施了一项涉及四相屏蔽输入/输出 (IO) 的创新策略,以使 BBCube 3D 具有更强的抗噪声能力。他们调整了相邻 IO 线的时序,使它们始终彼此异相,这意味着它们永远不会同时更改值。这减少了串扰噪声并使设备运行更加稳健。

图 2.减少输入/输出 (IO) 线之间的串扰噪声

该团队评估了他们提出的架构的速度,并将其与两种最先进的内存技术:DDR5 和 HBM2E 进行了比较。Ohba 教授在解释实验结果时表示:“BBCube 3D有潜力实现每秒1.6 TB的带宽,比DDR5高30倍,比HBM2E高四倍。”

此外,BBCube 3D还代表了比特访问能量方面的重大突破。Ohba 教授解释说:“由于 BBCube 的低热阻和低阻抗,可以缓解 3D 集成中典型的热管理和电源问题。因此,所提出的技术可以通过位访问达到显着的带宽。能耗分别是 DDR5 和 HBM2E 的 1/20 和 1/5。”

参考链接:BBCube 3D: A Breakthrough in Semiconductor Integration and Data Transmission;Demi Xia编译

最前沿的电子设计资讯

最前沿的电子设计资讯