在片上系统(SoC)设备领域,架构师在配置处理器子系统时会遇到许多选择。从单处理器内核到集群,再到主要是异构的但偶尔是同构的多核心集群,不一而足。

最近的一个趋势是广泛采用基于开放标准RISC-V指令集架构(ISA)的RISC-V内核。该系统可通过免版税的开源许可证获得。

在这方面,利用片上网络(NoC)技术的即插即用(plug-and-play)功能已成为加速基于RISC-V系统的集成的有效策略,这种方法有利于处理器内核或集群与来自多个供应商的知识产权(IP)块之间的无缝连接。

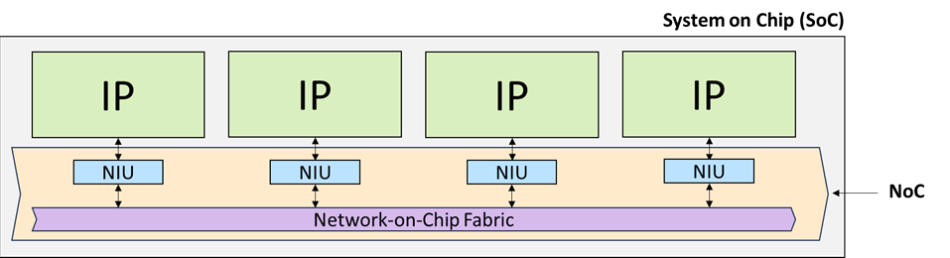

使用NoC互连IP具有多种优势。NoC可以扩展到整个设备,每个IP都有一个或多个跨越整个SoC的接口。这些接口具有各自的数据带宽,以不同的时钟频率运行,并采用SoC设计人员常用的OCP、APB、AHB、AXI、STBus和DTL等多种协议。每个接口都连接到相应的网络接口单位(NIU),也称为套接字(socket)。

NIU的作用是从传输IP接收数据,然后将这些数据组织并序列化为适合网络传输的标准化格式。多个数据包可以同时传输。到达目的地后,关联的socket会执行反向操作,先进行反序列化并打开数据封包,然后再将数据提交给相关IP。此过程是根据链接到该特定IP的协议和接口规范来完成的。

IP块可以直观地表示为实体逻辑块。此外,SoC通常使用单个NoC。图1展示了一个基本的NoC配置。

图1 一个非常简单的NoC表示,显示了基本的设计配置。来源:Arteris

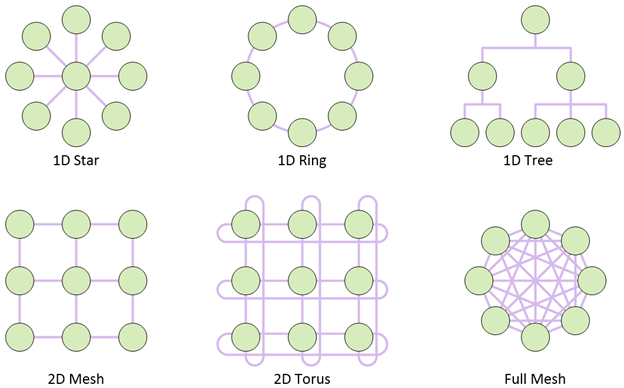

NoC本身可以使用多种拓扑来实现,包括1D星形、1D环形、1D树状、2D网状、2D环形和全网状,如图2所示。

图2 上述示例显示了各种NoC拓扑。来源:Arteris

一些SoC设计团队可能希望开发自己专有的NoC,这是一个极其耗费资源和时间的过程。采用这种方法需要由多名专业工程师组成的团队工作两年或更长时间。使事情变得更具挑战性的是,设计人员在调试和验证内部开发的NoC上投入的时间往往与整个设计的其余部分相当。

随着设计周期的缩短和收入压力的增加,SoC开发团队正在考虑商用NoC IP。这种IP既能满足内部开发的NoC IP所需的定制化要求,又能从第三方供应商处获得。

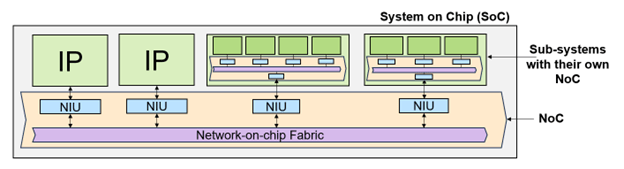

SoC复杂性不断增长的另一个挑战是在单个设备中使用多个NoC和各种NoC拓扑(图3)。例如,芯片的一个部分可能采用分层树状拓扑,而另一部分可能选择2D网状拓扑。

图3 该图突出显示了具有内部NoC的子系统块。来源:Arteris

在许多情况下,当今SoC中的IP块相当于几年前的整个SoC,这使它们成为了子系统。因此,这些子系统块的创建者通常会选择采用第三方供应商提供的行业标准的NoC IP。

在需要高度定制化以及计算和数据传输协同优化的情况下,例如处理器集群或神经网络加速器,IP开发团队可能会选择定制传输机制的实现方式。或者,他们可能选定使用一种较少采用的、高度专业化的协议来实现他们的设计目标。

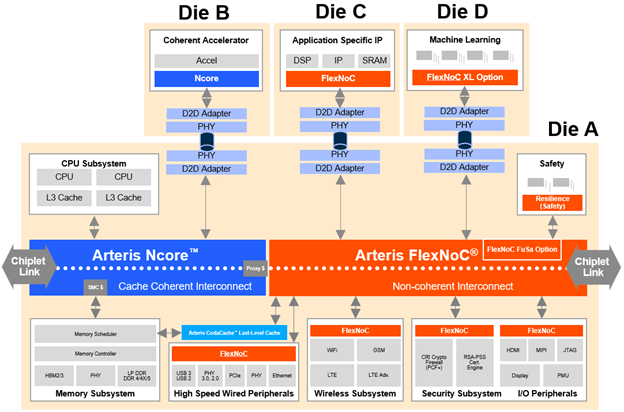

对于独立的RISC-V处理器内核,这些IP可为不需要一致性的设计人员提供AXI接口,为需要一致性的设计人员提供CHI接口。这样,这些内核就能在SoC层面上与行业标准NoC进行即插即用。

同样,如果设计团队在RISC-V设计中选择了一种不太常用的集群间通信协议,则该集群还可以具有面向外部连接的ACE、AXI或CHI接口。这种方法可实现与SoC的NoC的快速连接。

下面的图4显示了非一致性和高速缓存一致性选项。除了在IP和SoC中使用之外,这些NoC还可以在多芯片系统中充当超级NoC(super NoC)。

图4 在多芯片系统中展示了NoC互连IP。来源:Arteris

基于开放标准RISC-V指令集架构的处理器内核和集群的SoC设计正急剧增加。

通过利用NoC技术提供的即插即用功能,可以加速基于RISC-V的系统(包括多芯片系统)的开发和采用。这样就能在RISC-V处理器内核或集群与多个供应商提供的IP块之间就能实现快速、无缝和高效的连接。

(原文刊登于EDN美国版,参考链接:Accelerating RISC-V development with network-on-chip IP,由Ricardo Xie编译)

最前沿的电子设计资讯

最前沿的电子设计资讯