DAC外设(例如ATtiny系列)的8位分辨率通常是不够的。让我们看看如何使用片上资源来解决这个问题。

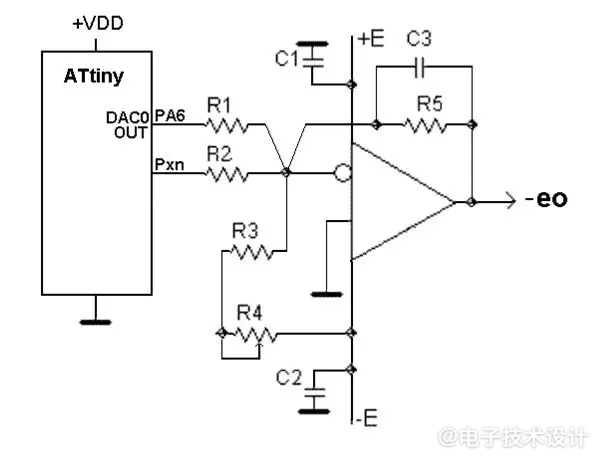

图1中的电路给出了一种提高DAC外设分辨率的方法。该电路还降低了DAC的输出电阻,并可减少其失调量(这对于ATtinyx17来说相当明显)。

图1:用于提高DAC外设分辨率同时降低DAC输出电阻和失调量的电路。

这种简单的方法是完全静态的(不需要添加额外的电容器,也就不会有缺陷和电荷刷新问题),它保留了原始DAC的单调性,但可能需要做些调整才能实现最佳线性度。

要再添加一位,可以使用MPU的任何空闲端口,在图1中,该端口标记为Pxn(x=A…C,n=0…7)。(可以通过这种方式添加不止一位。)

注意:在将端口Pxn用作DAC的额外位之前,应将其配置为输出。还要记住AVR ASM中那些非常有用的指令,它们可以有选择地更改连续的一位。

Pxn的位可以用作新的最高有效位(MSB),或新的最低有效位(LSB)——下面给出最后一种情况的详细描述。

为了保持输出的完整性,DAC0和Pxn的输出应具有相同的裕量。确保这一点的最简单方法是选择+VDD作为DAC的VREF。当然,在这种情况下,+VDD的值必须得到很好的调节。

运算放大器应提供足够的速度和精度,其中运算放大器输出的总附加误差为:

Er=Vos×(1+R5/Req)

其中Vos是运算放大器的失调电压,Req=R1||R3(近似值)。

Er值应至少小于修改后DAC的1 LSB。

DAC0 OUT上的最小电压约为0.2V(对于ATtinyx17)。如果这个失调量适合于应用,可以去掉电阻器R3和R4,而仅使用一个+E电源,但是,运放应该具有:轨到轨输出、足够的精度,并且能够在接近于零的输入条件下工作。

要将e0的最小值减小到零,就必须在DAC0获得零码时使用电阻器R3和R4将输出清零。

所有电阻的值可按下式计算:

R1≥5.6k(ATtinyx17数据手册的要求)

令N位为DAC初始分辨率。则:

R2=R1×2(N+1)(最终做些微调可以提供更好的结果)

由于DAC0 OUT上的最小电压约为0.2V,

R3+(R4/2)=5×R1/0.2(如果VDD=E=5V)

R3=0.8×(5×R1/0.2)

R4=R3/2(R4为多圈电位器)

电阻器R5可以轻松使DAC输出符合应用所需的值。

程序代码中可能需要做一些工作来同步DAC0 OUT和Pxn,尽管有些应用可以容忍去同步,如果它不是很大(小于几十微秒)。

注意:运放的输出与DAC0 OUT相比是反相的(因此图1中e0之前有“-”号)。可以通过在输出中添加反相器(运算放大器)或更改代码来解决此问题,这可能是更好的解决方案。

不应期望之前的转化率最大值会保持不变。每添加一位都意味着一个两倍大的电阻以及求和节点中一些添加的电容。

因此,每添加一个扩展位,稳定时间都将不可避免地变长。

为了减少运算放大器反相节点中的寄生电容,电阻器R1、R2、R3和R5应放置在靠近反相输入的位置。

有时为了优化DAC的性能(以补偿放大器),必须将电容器C3(10-40pF)与R5并联。

—Peter Demchenko在立陶宛维尔纽斯大学学习数学,并从事软件开发工作。

(原文刊登于EDN美国版,参考链接:Extending the resolution of a peripheral DAC,由Franklin Zhao编译。)

本文为《电子技术设计》2023年10月刊杂志文章,版权所有,禁止转载。免费杂志订阅申请点击这里。

最前沿的电子设计资讯

最前沿的电子设计资讯