经典脉宽调制器(PWM)所发出的重复序列,包括H个连续高逻辑电平(1),后跟L个连续低逻辑电平(0)。每个高电平和低电平都持续一个时钟周期T=1/F(Hz)。所得到的占空比可定义为H/N,其中N=H+L个时钟周期。N通常是2的幂,但N可以是任何大于0的整数。PWM必须面对的一个挑战是通过滤波使数据流中的动态AC部分实现衰减,同时保留其平均DC值。在整个输出序列范围内,经典PWM的最低频率分量F/N也是最大的,因此最难衰减。幸运的是,这篇设计实例引入了一个简单的技巧,可以缓解这一挑战。

想了解最新的电源管理技术吗?2023年11月2日,由AspenCore举办的IIC国际集成电路展览会暨研讨会之第26届高校电源管理及功率器件论坛邀请到ADI、英诺赛科,必易微、无锡博通、Nordic和村田的技术专家,探讨最新的电源管理和宽禁带功率器件技术。欢迎点击这里报名参加,来和专家面对面交流!

在讨论这个技巧之前,有必要快速回顾一下其他交流能量缓解技术,所有这些技术都像经典技术一样,采用某种计数器作为其驱动引擎。我几年前读过的一种方法涉及N=2M-1个状态的M位伪随机序列生成器,其每个位都连接到数字比较器的一个输入[1]。剩余的输入以数字W表示。当生成器的数量小于W时,比较器输出1;否则,输出0。当对发生器计时时,结果是W个1、N-W个0以及W/N占空比的随机数据流。所得到的“白噪声”频谱性质比传统PWM的F/N主要分量更容易滤除。

一些SAM D Microchip微控制器(MCU)的硬件中内置了更有效的缓解措施[2]。这些PWM修改了8位经典PWM序列的2X个连续周期,以产生长度为2X+8的更长重复序列。这里X=4、5或6。对于K/2X+8的占空比,0≤K<2X+8,每个八位序列至少具有K/2X个1的整数部分。将剩余的K取2X的模个1尽可能均匀地分布在2X八位序列中。结果是经占空比调制的八位序列的长序列,其在生成的最低频率F/2X+8 Hz处和附近具有非常少的频谱能量,其中大部分在F/28处和附近,因此滤波问题得到很大简化。

这些方法的硬件支持并不总是可用。幸运的是,大多数MCU都可以轻松实现上述技巧,其描述如下。一旦N=2、3或4…多达28个(甚至216个)状态计数器驱动PWM的初始设置完成,无需软件干预的“设置(占空比)即不管”的PWM操作就近在咫尺。当占空比确实需要改变时,将所需的H值写入输出比较寄存器(OCR)即可。在大多数情况下,两个具有独立占空比的PWM可用,通常由同一计数器驱动。考虑一下利用这些功能组合可以实现什么目标。

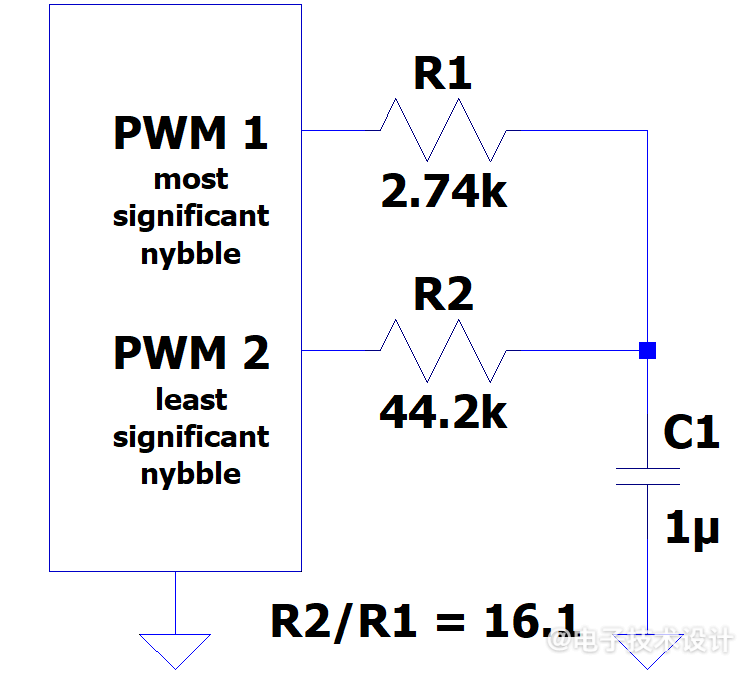

在一个示例中,可以将计数器配置为N=16。PWM的占空比可为1/16、2/16、3/16,一直到15/16。剩余状态将为0/16或16/16。两个PWM输出由两个电阻按1:16的比例串联组合连接。在这两个电阻的连接处,有24×24=28种可能的平均值,就像单个PWM呈现28种不同状态一样。影响交流衰减的最简单的方法是在该结点和地之间连接一个电容器(图1是完整电路的示例。)

图1:实现交流衰减最简单方法的完整电路,其中电容器连接在PWM输出端的两个电阻器的结点与地之间。

但这种技术和传统PWM都可以受益于具有更多数量的电阻器和电容器的更复杂的网络,甚至还可以选择使用运算放大器来缓冲结果。运算放大器还可以实现包含复极点对的滤波器,而不是仅限于实极点,否则实极点是唯一可获得的极点。前一种类型能更有效地最小化滤波器稳定时间和残余交流能量大小的乘积。(早期的设计实例“Optimizing a simple analog filter for any PWM”中已经给出了这样的一个例子。)

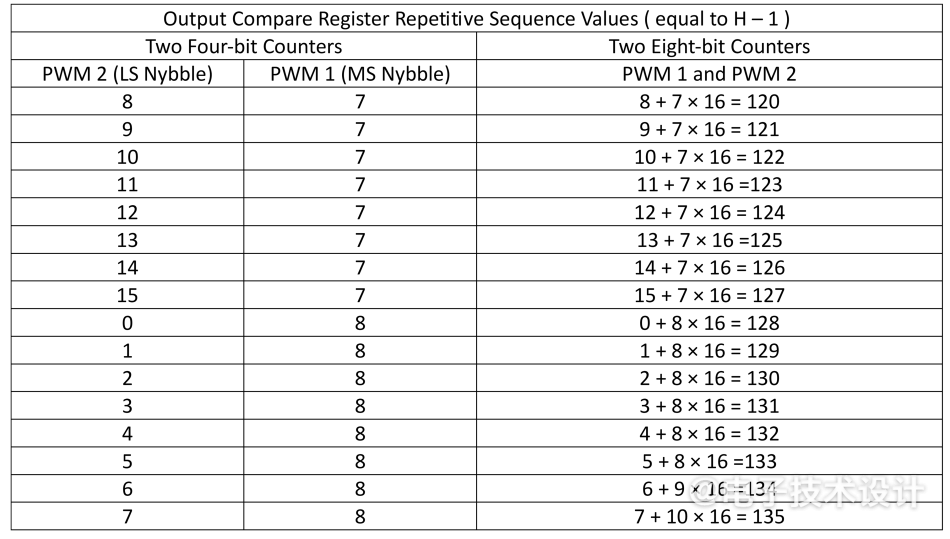

我使用ATmega16 MCU来实现图1电路。尽管可以使用更高的时钟频率,但我将F设置为1MHz。PWM 1和PWM 2配置为以两种不同的模式运行:作为前面所述的具有独立值输出的两个四位单元,以及作为具有相同输出的八位单元。这对于两种操作模式就能保持相同的R-C滤波器时间常数。表1列出了每种模式的OCR重复序列。

表1:四位和八位PWM模式用于生成图2波形的OCR值。

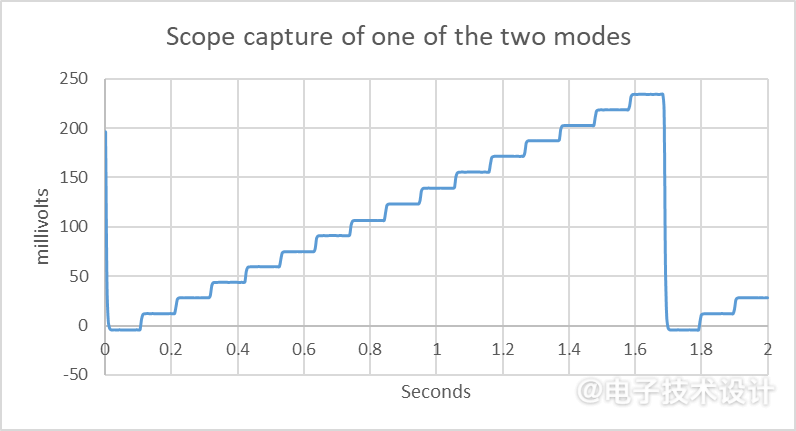

图2给出了两种模式之一的示波器捕获波形;两种模式的屏幕截图无法区分,分辨率约为18mV。必须在R1-R2-C1结点和负直流电压之间连接一个额外的电阻(未显示)。在不影响R1-R2比率的情况下,这会将波形的电压移至接近地的电压,以便示波器可以以高分辨率显示它。

图2:通过对表1中列出的四位和八位PWM模式的OCR进行编程而生成的波形。这两种模式的结果看起来相同,因为示波器会以200ms/div扫描速率平均交流能量。

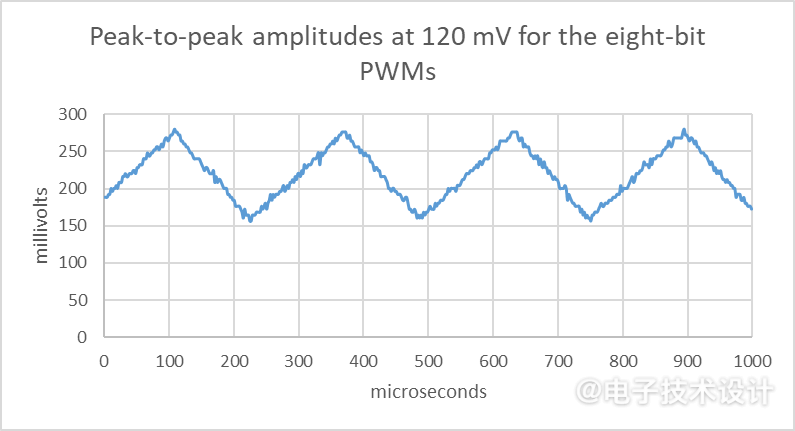

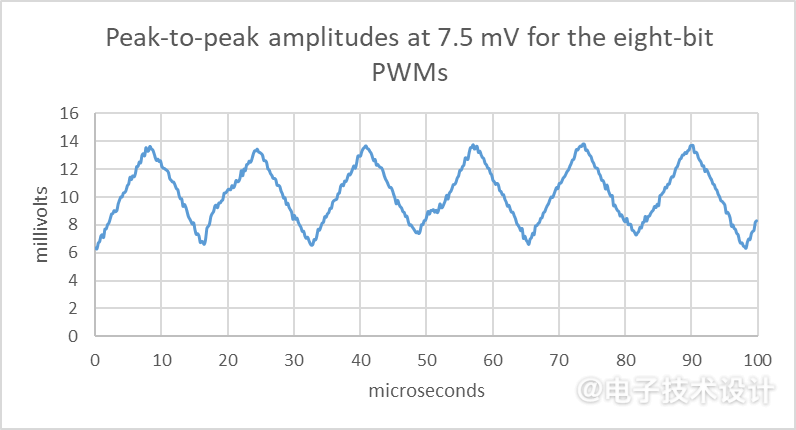

两个四位PWM的频率均为F/16=62.5kHz;八位PWM的频率为F/256=3.90625kHz。该代码大约每100ms更改一次OCR寄存器。在图2的扫描速率下,示波器滤除了PWM交流信号,并将其替换为平均值。在随后的图中,示波器以更快的扫描速率显示了它们的峰峰值幅度。图3显示8位PWM的电压为120mV,而图4显示4位PWM的电压仅为7.5mV。

图3:图1电路中八位PWM电容器两端的交流能量。

图4:图1电路中四位PWM电容器两端的交流能量。四位PWM的周期和幅度比八位PWM小16倍。

两种模式的步进分辨率均为18mV,四位峰峰值噪声在不到半步的情况下接近最佳。所有更多的交流信号衰减都会不必要地增加1ms半步稳定时间。在1/16频率下峰峰值为120mV(6.7步)时,八位PWM实现几乎无法使用。必须将电容器值增加到15μF,将相关的稳定时间增加15倍,才能满足双四位PWM方法的能量衰减性能。

本示例中采用的方法非常强大。通过一对8位PWM与比率为256:1的0.1%电阻互连,(双八位)16位PWM可具有比传统16位单元更容易滤除(容易256倍)的交流输出。小于N=216或28级的PWM分辨率也可以实现,同时减少PWM周期并简化相关的滤波要求。甚至还有带三个或四个PWM的MCU,其输出可以与合适的电阻网络相加。

Christopher Paul在通信行业的多个工程职位上工作了40多年。

(原文刊登于EDN美国版,参考链接:Double up on and ease the filtering requirements for PWMs,由Franklin Zhao编译。)

本文为《电子技术设计》2023年10月刊杂志文章,版权所有,禁止转载。免费杂志订阅申请点击这里。

最前沿的电子设计资讯

最前沿的电子设计资讯