小芯片(Chiplet)标志着半导体创新的新时代,而封装是这一雄心勃勃的设计事业的内在组成部分。然而,虽然小芯片和封装技术齐头并进,重新定义了芯片集成的可能性,但这种技术结合并不是那么简单和直接。

在芯片封装中,裸芯片被封装在带有电气触点的支撑壳中。外壳保护裸芯片免受物理伤害和腐蚀,并将芯片连接到 PCB。这种芯片封装形式已经存在了几十年。

然而,由于摩尔定律的放缓以及单片IC制造成本的不断增加,业界开始采用硅中介层等先进封装技术。先进的封装技术也增加了成本,一般只有高性能计算(HPC)应用的大型芯片才能负担得起。

此外,先进的封装解决方案还增加了设计的复杂性。例如,中介层需要额外的硅片,从而限制了设计人员可以放置在芯片上的空间。此外,硅中介层限制了系统级封装 (SiP) 的整体尺寸,从而降低了晶圆测试覆盖率。这反过来又会影响产量、增加总拥有成本并延长生产周期。

进入小芯片时代,它承诺以更低的功耗实现更小的 SiP 封装。换句话说,与先进封装技术相比,小芯片能够在使用标准封装的同时,通过芯片堆叠缩短传输路径,提高带宽,从而增加整体性能。

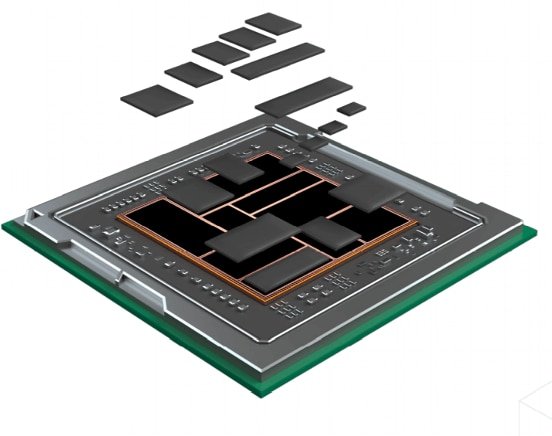

图 1:Chiplet使用高密度基板、硅中介层、桥接器和其他互连方法促进多个硅芯片的单封装集成。(来源:Cadence)

Chiplet将单片 IC 拆分为多个功能块,将功能块重新构建为单独的芯片组,然后在封装级重新组装。但芯片组之间必须通过密集、快速和高带宽的连接进行通信,这就凸显了芯片与封装之间的棘手关系。

在将于11月2-3日举办的2023国际集成电路展览会暨研讨会(IIC Shenzhen)同期,还将举办EDA/IP IC设计论坛,届时来自国内外的知名厂商、领先企业将与现场观众一同分享包含RISC-V在内的行业前沿话题和最新的技术成果,共同探讨行业趋势和未来发展方向,欢迎点击这里报名参加!

Eliyan 首席执行官 Ramin Farjadrad 表示,Chiplet消除了先进封装的缺点和限制。Eliyan 等公司正在展示标准有机封装中的芯片到芯片实施,据 Farjadrad 称,这使得能够创建更大的 SiP 解决方案,从而以相当低的成本和更高的产量实现更高的单位功率性能。

Farjadrad 开发了线束 (BoW) 小芯片系统,该系统后来被开放计算项目 (OCP) 采用作为互连标准。然而,现在业界正在围绕通用Chiplet Interconnect Express (UCIe) 接口进行联合,该接口旨在通过开源设计标准化小芯片之间的芯片间互连。

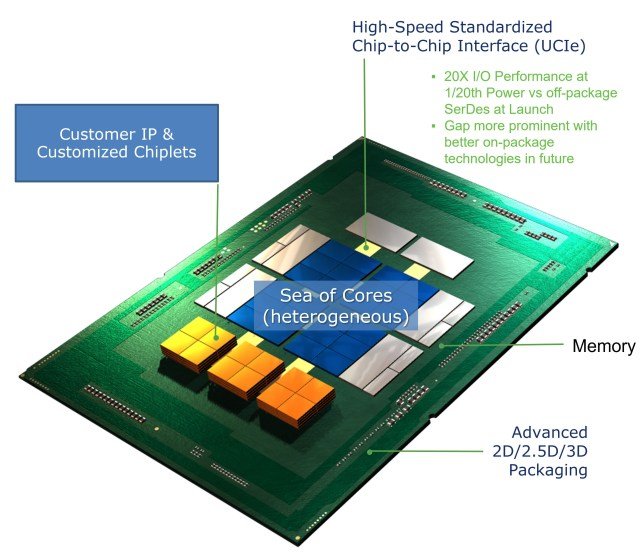

UCIe 联盟正在两大领域开拓小芯片市场:标准 2D 封装技术和更先进的 2.5D 技术,例如晶圆基板上芯片 (CoWoS) 和嵌入式多芯片互连桥 (EMIB)。CoWoS 和 EMIB 等先进封装选项可提供更高的带宽和密度。

这充分证明了封装在Chiplet设计中的关键作用,以及它对Chiplet性能的影响。以英特尔最近在其年度活动"创新2023 "上展示的基于小芯片组的UCIe连接测试芯片为例。该公司在英特尔 3 工艺节点上制造该芯片,并将其与在台积电N3E节点上制造的 Synopsys UCIe IP 小芯片配对。两个小芯片通过英特尔的 EMIB 接口互连。

图 2:小芯片设计可根据特定应用需求采用各种封装技术。(来源:UCI 联盟)

毫不奇怪,半导体行业开始在封装和小芯片交叉领域推出新举措,首先,智原科技(Faraday Technology)推出了2.5D/3D封装服务,号称可以促进多源裸片在chiplet中的无缝集成。总部位于台湾新竹的智原科技正在与晶圆厂和 OSAT 供应商密切合作,确保在提供这些服务的同时满足产能、良率、质量、可靠性和生产进度要求。

其次,西门子 EDA 推出了适用于多芯片架构的设计测试 (DFT) 解决方案,可在单个器件中垂直 (3D IC) 或并排 (2.5D) 连接芯片。Tessent 多芯片软件解决方案可以生成芯片到芯片的互连模式,并使用边界扫描描述语言 (BSDL) 实现封装级测试。

Yole Intelligence 计算和软件解决方案高级分析师 John Lorenz 表示,采用小芯片方法进行 IC 设计的经济性与互连,和封装解决方案的成本和成熟度紧密相关。然而,虽然接口和互连技术备受关注,但封装在小芯片设计中的作用却不太明确。

随着 UCIe 标准的出现,这种情况可能会改变,该标准旨在在封装级别创建通用互连。其目标是为小芯片建立一个充满活力的多供应商生态系统,因此半导体公司可以简单地从其他设计人员那里选择小芯片,并以最少的设计和验证工作将它们嵌入到他们的设计中。

归根结底,小芯片将同时满足标准有机封装和先进封装解决方案。设计工程师必须在设计过程的早期阶段确定其小芯片的最佳封装结构,以及芯片尺寸、基板、凸块间距和数量、功率分析和热仿真。

但有一点是明确的:封装技术与小芯片设计的未来有着内在的联系。在小芯片封装方面,并没有一个万能的解决方案。

在将于11月2-3日举办的2023国际集成电路展览会暨研讨会(IIC Shenzhen)同期,还将举办EDA/IP IC设计论坛,届时来自国内外的知名厂商、领先企业将与现场观众一同分享包含RISC-V在内的行业前沿话题和最新的技术成果,共同探讨行业趋势和未来发展方向,欢迎点击这里报名参加!

原文发表于ASPENCORE旗下EDN姐妹媒体EETimes,参考链接:How the Worlds of Chiplets and Packaging Intertwine;Demi Xia编译

最前沿的电子设计资讯

最前沿的电子设计资讯