相较于传统的硅组件,碳化硅(SiC)功率MOSFET具有以下优点:在给定额定电压下具有较低的通态电阻RDS(ON)、更快的开关速度能带来更低的开关损耗,以及能够在更高的结温下工作。单裸片SiC MOSFET的额定电流被限制在200A左右,因此对于更大电流的应用,可以将分立的裸片并联在一起。在更高的电流水平下并联电源模块是一种更实用的方法,因为每个模块都针对寄生电感和电容的影响进行了优化,而且能够实现更好的可重复性。

使用SiC组件创建并联模块架构的最佳方法存在着一些挑战。由于其快速开关能力,在对模块和栅极驱动器布局时,必须要注意减少寄生效应并确保实现模块之间均匀的电流分配。在静态电流分配方面,组件的RDS(ON)和模块连接电阻起着关键作用。SiC MOSFET在强栅极驱动下,其RDS(ON)具有正温度系数,这可以使电流重新取得均衡,从而使并联变得更容易,因为组件传导的电流越大,温度越高,与较冷的组件相比,其RDS(ON)将会增加。这样可以避免热失控。另一方面,阈值电压(VTH)具有负温度系数,这会导致结温最高的组件提前导通,从而产生更高的开关损耗。

本文重点介绍意法半导体(ST)应用工程师Antonia Lanzafame在APEC大会上的演讲,其中特别关注了VTH均衡对提高SiC MOSFET电源模块开关性能的重要性。

为导通状态RG(ON)和关断状态RG(OFF)选择合适的栅极电阻RG是优化模块的关键部分:

相较于具有较低VTH的模块,具有较高VTH的模块需要有较低的RG(ON) ,才能实现相同的di(ON)/dt和能量损耗。因此,对于具有各种VTH值分布的模块,应该选择特定的RG值来补偿这种影响。

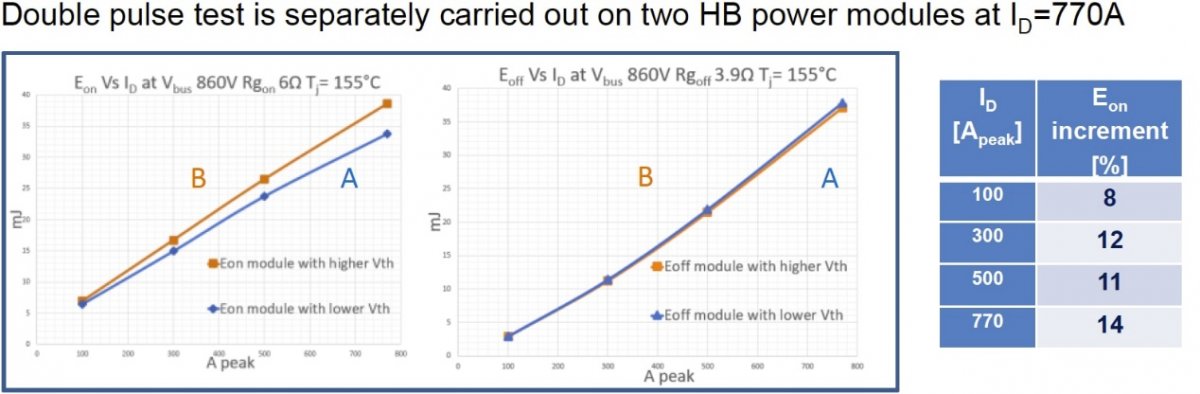

其影响如图1所示。这里比较了两个模块之间的开关损耗,这两个模块在高侧(HS)开关的VTH相差500mV,但使用了相同的RG(ON)。如图所示,VTH较高的模块导通较晚,并且di(ON)/dt较低。因此,它表现出较高的导通开关损耗(EON)。

图1:HS SiC MOSFET的VTH存在500mV差异而RG(ON)相同的两个模块的开关损耗比较。(来源:ST)

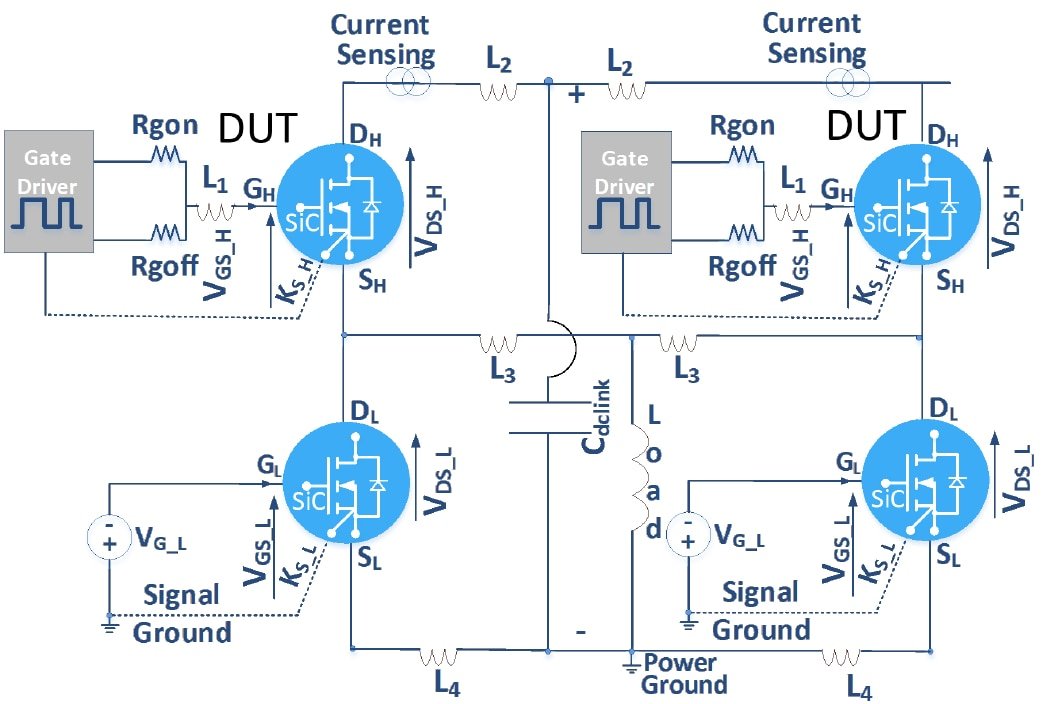

为了研究VTH不匹配对于并联半桥(HB)模块的影响,在此使用了图2所示的电路。直流(DC)总线和负载连接采用对称布局。每个模块使用单独、相同的栅极驱动器,并对来自栅极驱动器的输入信号进行了调整,以确保使HB模块中的HS开关同步导通和关断。模块布局旨在最大限度地减少电源回路、总线和负载连接中的寄生组件。

图2:研究并联HB SiC模块中VTH不匹配的电路原理图。(来源:ST)

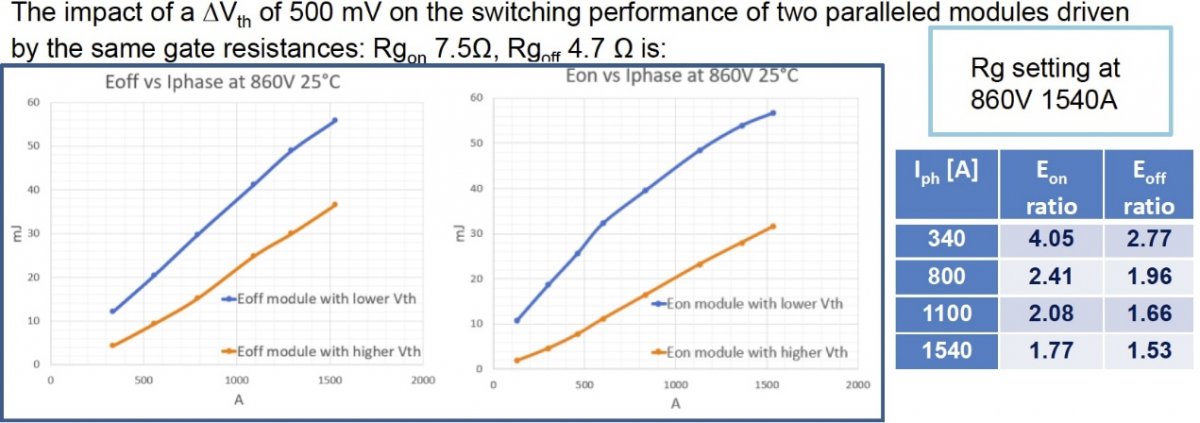

在这些并联模块测试中,所选用的组件在模块之间具有500mV或250mV的已知VTH偏移。图3显示每个模块的EOFF和EON开关损耗,图中所列模块具有相同的RG(ON)和RG(OFF)值,并且模块之间的VTH不匹配为500mV。

图3:两个并联HB SiC模块(VTH不匹配为500mV)的EOFF和EON开关损耗。(来源:ST)

相较于具有较高VTH的模块,具有较低VTH的模块将会更早导通且更晚关断,因此会造成电流分配的严重不均衡。这会导致较低VTH的模块的EOFF和EON开关损耗更高得多,损耗的相对差值比可能大于4,如图3中的表格所示。

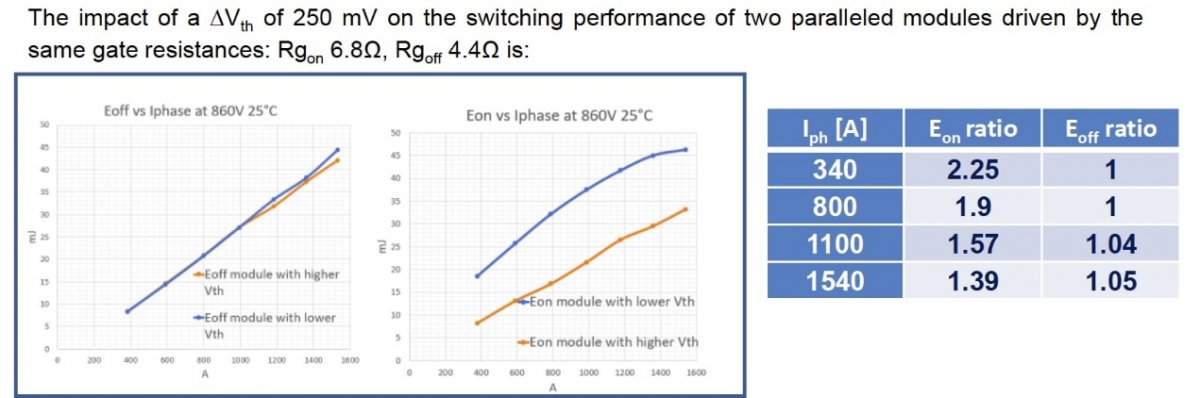

为了比较上述结果,还研究了相对VTH不匹配为250mV的并联模块。如图4所示,相较于具有500mV VTH偏移的模块,其结果大幅改善了。改进电流分配后,可以降低所使用的RG值,同时仍然满足过冲条件下的组件最大电压规格。

图4:两个并联HB SiC模块(VTH不匹配为250mV)的EOFF和EON开关损耗。(来源:ST)

VTH不匹配的影响体现在模块的安全工作区(SOA)的缩减上。较高的不匹配会导致较高的电流不均衡,以及对整个并联模块组件产生较大的热应力。相反地,抑制不匹配所导致的过冲,可能需要使用较高的栅极电阻,从而使开关频率受到限制。

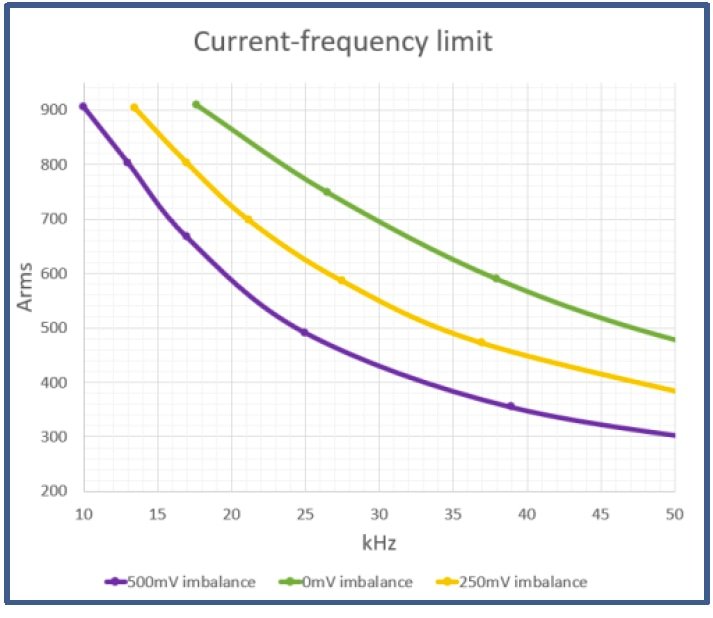

随着开关频率的提高和RG值的降低,即使VTH有微小差异,也会导致较低VTH的模块以较高的di/dt进行开关,从而导致电压过冲超过组件额定值。图5显示并联HB模块在不同VTH不匹配情况下的SOA。将VTH不匹配从500mV降低至250mV,有助于使电流能力提高16%至31% (具体取决于频率)。

图5:两个并联HB SiC模块在各种VTH不匹配情况下的SOA。(来源:ST)

将SiC MOSFET裸片和模块并联连接,需要仔细考虑所使用的栅极电阻,以及整个模块规格可容许的最大VTH不匹配电压。

(原文刊登于EDN姊妹网站Power Electronics News,参考链接:Parallel Operation of SiC Power Modules,由Susan Hong编译。)

最前沿的电子设计资讯

最前沿的电子设计资讯