据EDN电子技术设计引援韩国媒体报道,SK 海力士认为,市场上有可能更“高效”地实施半导体布局,该公司相信他们可以通过下一代HBM4内存来实现这一目标。

据说SK海力士聘请了大量逻辑半导体设计专家,组成半导体设计研究团队,从HBM4开始,挑战在同一个芯片(由正方形片组成圆形晶圆的芯片,每个正方形都集成有电路)上同时实现存储半导体和逻辑半导体的方法。

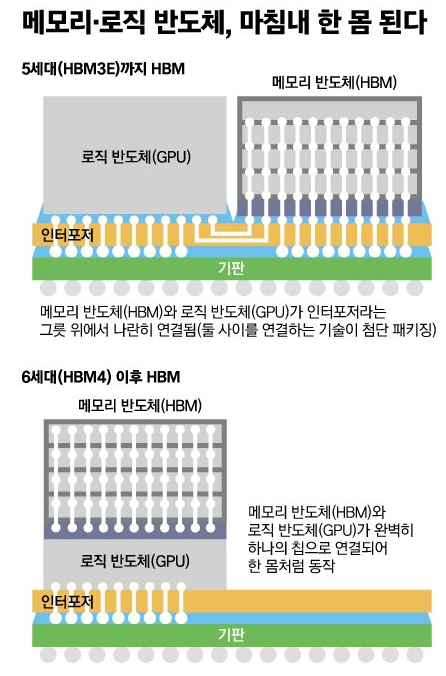

就当前产品而言,HBM等先进存储半导体通过尽可能靠近GPU芯片(逻辑半导体)连接来提高效率。虽然 HBM(即层叠在逻辑芯片顶部的 DRAM 堆栈)放置在逻辑芯片之上,但 GPU 的主要计算功能与 HBM 分离在单独的芯片中,各个计算通过专用芯片分开,从更广泛的角度来看,这确实看起来是一种低效的方法。

CoWoS 等封装技术可以方便地弥合半导体之间的差距,但 “差异”仍然存在。

SK海力士现在打算通过将存储器和逻辑半导体集成到一个单片中来满足这种差异。

然而,从HBM4开始,GPU的主要计算功能预计将转移到具有存储半导体的逻辑芯片上,并与HBM一起实现。

目前,半导体生态系统订单分为芯片设计(无晶圆厂)、寄售生产(代工)和存储器/逻辑。这不仅涉及每个制造过程的复杂设备,而且在大多数情况下,工作必须外包给专门从事其开发阶段的不同公司。

据悉,SK海力士正在与包括NVIDIA在内的多家全球无晶圆厂公司讨论HBM4设计方法。SK海力士和NVIDIA极有可能从一开始就共同设计芯片并委托台积电生产来制造半导体。

最前沿的电子设计资讯

最前沿的电子设计资讯