作为现代科技的基石,半导体已经渗透到各个领域。无论是智能手机、电动汽车,还是物联网、人工智能,都关注半导体的应用。随着科技的持续发展和对高性能、高效能产品需求增长,半导体市场的前景将持续迎来巨大的增长。据台积电预测,到2030年,全球半导体产值将达到1万亿美元。

11月23日,在上海浦东临港新片区,在由临港新片区管委会、上海市经济信息化委指导,由临港集团主办、临港科投与AspenCore承办的“2023中国临港国际半导体大会”上,台积电(中国)有限公司副总经理陈平博士以“半导体制程技术发展趋势”为主题,就工艺技术/制程技术发展以及趋势进行了分享。

陈平博士认为,生成式AI的横空出世成为了划时代颠覆式的应用,重要意义不亚于计算机诞生与互联网诞生,甚至瓦特蒸汽机。他表示,大数据、大模型、大算力是支持生成式AI基础的三大要素,前两个部分是AI科学家的工作,而提供支持大算力的晶体管,则是制造企业的工作。

尽管Chat GPT是去年9月份才出现,至今仅一年多时间就已发生了两次迭代,同时端侧已经有很多应用应运而生,如高通发布的新的骁龙 8 Gen 3 SoC和联发科天玑8300,已经在端侧算力提高到新的高度。陈平博士预测大模型将很快在智能手机,PC,平板端落地。

而在智能汽车应用上,在过去的两年,中国汽车在电气化上面已做出了很大的进展,此外,随着大模型AI的出现,汽车智能化程度预计也会迎来突飞猛进的发展,同时也给半导体工艺提出了挑战。

无论是云端,还是在端侧的应用,生成式AI将对半导体工艺提出了高算力和高能效比的要求。大算力是支撑大模型的一个必要条件,而大算力对于工艺来说就是更高的集成度,在单位面积里集成更多的晶体管。高能效比则是为了降低整体成本,如在数据中心中,目前主要成本是电和冷却,若器件端功耗可降低20-30% ,对整体成本而言影响是巨大的。

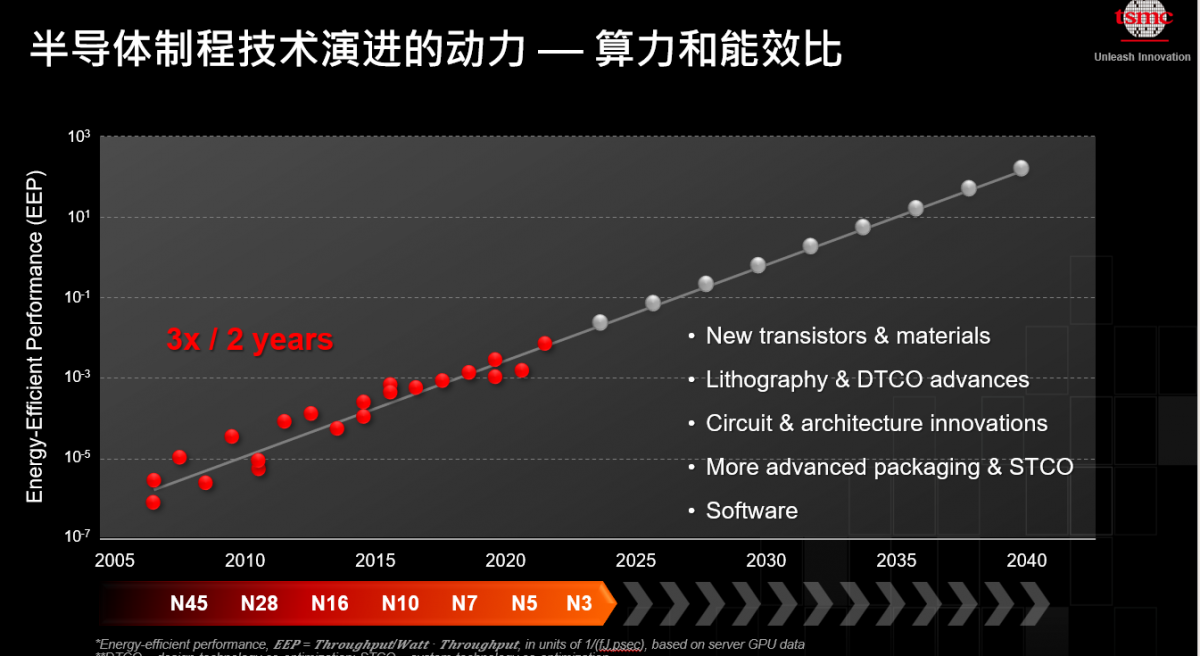

用GPU运算的算力除上单位功耗算力的能效来看,2005年到现在是每两年有3倍的增长。

陈平博士指出,如果我们用能效比去看,其实我们一直在摩尔定律这条曲线上,而且往前还必须沿着这个曲线前进。

那芯片如何才能不断实现高算力和高能效比的提升?陈平博士指出有两大元素,首先是传统工艺制程微缩上继续前行,再者是2.5D、3D整合。他认为这些微缩本身给我们提供了最有效的算力密度和能效比的提升。

而针对Chiplet能否取代先进工艺的争论,陈平博士直言不行“Chiplet只是扩展了芯片,但是改变不了芯片的品质,就是能效比和算力密度,所以我们需要继续提升。现在3纳米已经进入了大规模量产,2纳米看起来也已经呼之欲出了。再继续往下,我们的工艺工程师还在继续往前在努力。”

此外,制程与设计协同优化 (DTCO)成为必要。DTCO的核心就是设计工程师与光刻工程师共同协作,寻找最佳的设计和光刻工艺方案。这个方案要既能满足器件性能的要求,又能在Fab里实现。陈平博士介绍:“从7纳米开始大概有25%的工艺是基于DTCO的,到5纳米的时候就到40%,到3纳米就更多。也就是说,我们在设计和工艺协同下面达到最好的输出,不拘泥于一些很机械的参数。那些说摩尔定律死的人很多是拘泥于摩尔在某一个时代的定义,其实我们对那个已经没有太大的兴趣。”

微缩工艺还能发展多久呢?陈平表示他对人类的智慧和工程师的创造性充满自信。目前制程工艺在FinFET节点上,28纳米是平面结构最后一代,到16纳米,12纳米引用了新的晶体管结构一直用到7纳米,5纳米,3纳米,现在又碰到了新的挑战,陈平表示:“台积电在2纳米上会引入所谓Nanosheet,类似于GAA结构。在2纳米以后现在有一种结构叫CFET,再往后还有很多新的黑科技,所以大家要对半导体科学工作者有信心,就是往前走我们还没有看到尽头在哪里。”

回顾半导体的发展历史,1947年贝尔实验室发明晶体管,1960年德州仪器发明了集成电路,把晶体管和一些小型电路集成在一起,到2010年左右的时候,开始把集成电路集成在一起,发展到3D堆叠和2.5D先进封装技术。

陈平博士表示,随着数字化时代数据量的快速增加,SoC上的微缩已不足以满足系统发展的需要。3D系统的引入将使得在SoC工艺基础上大幅扩展集成度,实现所谓的Chiplet,同时,2.5D和3D工艺可以帮助实现异构集成,让逻辑芯片和存储芯片得以方便地集成在一起。因此,2.5D和3D系统集成已成为先进工艺的有机组成部分。

据介绍,台积电的3D堆叠封装技术有两种,一种是wafer on wafer的堆叠,还有一种是chip on chip的堆叠,chip on chip的堆叠叫SoIC。台积电的平行的整合就是2.5D,其中比较有名的是2012年台推出的CoWoS工艺,还有iPhone里面的info,都是属于2.5D的技术。

CoWoS技术面临的最大挑战是大型模型对计算的高要求。目前,CoWoS把逻辑和存储芯片平行放置在一个中介层上,台积电计划于2025年将中介层的尺寸增加到六个六分之一掩模版,是目前的3.3倍。

而3D堆叠技术提供了更高的集成度,更好的带宽,更好的性能,已可将十几个HBM堆叠在一起。

另外,由于计算的引入,光电器件也成为了热门,陈平表示:“由于计算的结果要通过光学网络传递出去,因此光和电之间的集成整合也是给我们平台提出了一个需要。”

陈平介绍到,目前的计算体系大概分为几个层次。第一个层次是计算单元,比如GPU和DSA,通过3D打印技术整合在一起,这是最底层的计算部分,在这个部分,要实现最好的能效比,不仅涉及到逻辑工艺,还包括供电,如现在最热的概念IBR,也是为了提高能效比。最终的计算需要依靠大数据和大的内存实现,而内存的集成是下一级的集成。最终,还需要进行单个相集成,直接将计算与光学结合。

上述系统非常复杂,需要使用系统架构的共同优化(STCO),这比DTCO更复杂。陈平博士表示:“如果使用先进的工艺和技术加上STCO设计,有可能会降低几个数量级,这是我们在工艺上目前正在努力实现的目标。”

最后,陈平博士总结表示,颠覆式技术的出现使半导体含量持续增加,算力和能效比需求的不断提升驱动制程技术发展,他指出制程技术发展趋势主要有三点:首先是器件微缩和2.5D/3D系统集成并行发展;其次,电学与光学技术的结合,同时提升算力、运力、存力各类产品的性能;最后,DTCO/STCO技术,推动系统、设计、制程的协同发展。

最前沿的电子设计资讯

最前沿的电子设计资讯