每个开放标准如果想被广泛采用,都需要一个强大的生态系统,其中包括测试和验证功能。正如供应商围绕快速发展的计算快速链路(CXL)规范联合起来发布各种产品一样,厂商也纷纷提供工具来帮助确保这些产品可靠运行并相互兼容。

CXL互连基于外围组件快速互联(PCIe)总线标准运行。PCIe总线无处不在、易于理解,这使得CXL测试和验证工作变得更加容易。PCIe还为相当成熟的非易失性快速存储器(NVMe)规范提供了底层基础。

虽然对于像群联电子(Phison Electronics)这样的SSD制造商来说,CXL涉及很多验证,但这与PCIe验证没有什么本质上的不同,群联电子首席技术官Sebastien Jean在接受笔者采访时表示。

大约80%的固件围绕NAND管理,然后大约20%是特定于协议的代码块。“从我们的角度来看,它实际上只是另一种接口。”Jean认为。

采用CXL的过程是弄清楚SSD必须做什么,才能维护内存读写请求。

一旦通过了协议,一切就都与NAND管理有关了,它必须与后端的CXL结合起来。维护PCIe命令需要遵循严格的命令处理顺序,通常是在收到命令时,他指出。“但是,如果遇到足够复杂的拓扑,那么在某些情况下,某些命令也可以优先于其他命令,但这些规则非常严格。”他补充说。

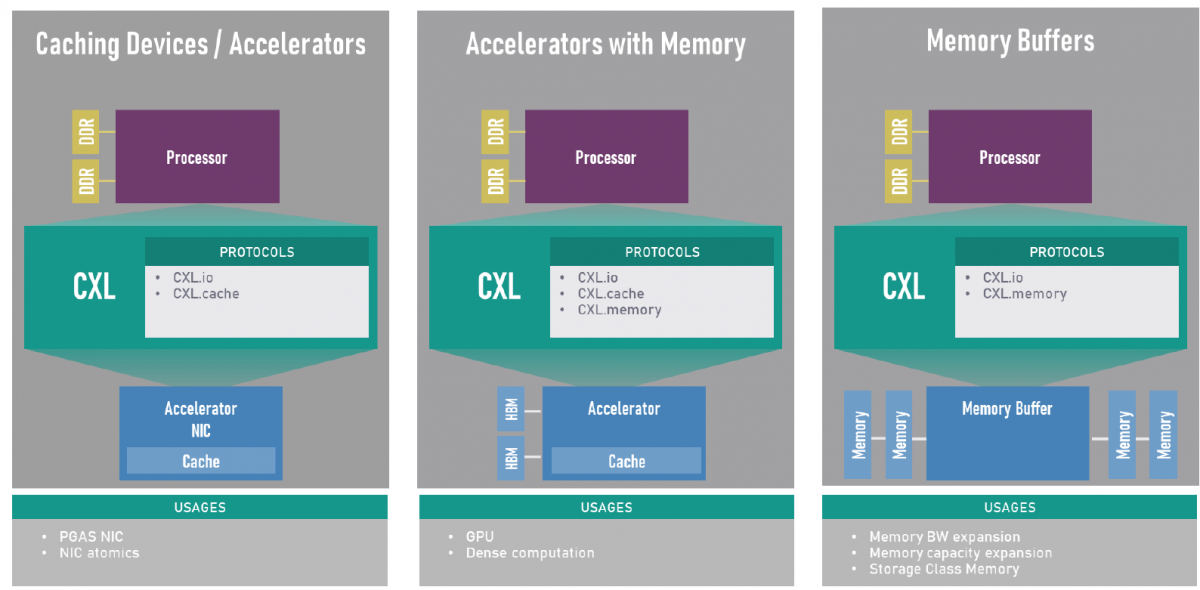

CXL的相同之处在于必须运用协议规则。与其他存储协议增加了很多不必要的复杂性相比,这种协议相对简单(图1)。Jean表示:“CXL协议非常简单。速度非常快。”

PCIe简单而不落俗套,而其普遍性意味着有大量的技术和专业知识,包括测试和验证工具。“PCIe是事实上的互连总线。”Jean表示。他并补充说,CXL本质上是90%的PCIe,外加一些附加功能,而不像人们所认为的那样难以接近和神秘。“这并没有让我们在做的事情变得更复杂。”

图1:即使CXL具有多功能性(包括三个主要用例类别),它也不像其他存储协议那么复杂。(图片来源:CXL联盟)

虽然CXL测试和验证本质上并不复杂,但它仍然是一项企业级的工作。“你必须对它进行更鲁棒的测试,”Jean指出,“必须进行大规模的互操作性测试。”

Rambus公司互连业务部门营销副总裁Mark Orthodoxou表示,在考虑CXL时,NVMe也是一个很好的比较,特别是考虑到它也基于PCIe。但他告诉笔者,CXL也让人回想起早期开发串行连接SCSI(SAS)和串行高级技术附件(SATA)两种接口规范的经历。“从这个意义上说,它比NVMe更让人感觉全新。”

Orthodoxou表示,当NVMe在2011年出现时,针对闪存及其特定要求,分层存储的概念就已经被引入,而内存分层的概念则更为新生。Rambus借鉴了研究SAS、SATA和NVMe的悠久历史,并与CXL联盟的合规工作组分享其专业知识。

正如PCIe特别兴趣小组(SIG)拥有一份跟踪集成商和规范合规性的名单一样,CXL可能会推出类似的内容,并会推出一系列的测试研讨会,用以吸引生态系统中的供应商,包括CPU、内存和控制器制造商以及CXL分析仪和测试设备制造商,Orthodoxou表示。就时间表而言,预计CXL 2.0的大部分资格认证将在今年年底完成。

但这引出了一个问题:鉴于CXL 3.0去年才推出,测试和验证是否能跟得上?

Orthodoxou表示,好消息是标准发展得如此之快,是因为数据中心确实有机会利用CXL提供的内存分层来解决实际问题。“业界有很多声音提出了很多不同的需求和用例,”他指出。但是,他补充说,联盟内部有一些讨论,认为该标准的发展速度要比成员制造芯片和系统的速度快。因此,可能需要在标准制定方面稍微放慢一些。

Orthodoxou认为,虽然CXL测试扎根于PCIe而不会遇到太多成长的烦恼,但其发展速度可能会转化为Rambus在其实验室测试中看到的问题。“在某种程度上,这有待解释。”他指出,“由于工程变更通知单(ECN)被不断添加到标准版本中,因此每次实施都会发生这种功能蔓延。然后新的标准版本引入了看起来对之前版本确实有用的功能。”

出现的一个挑战是混合实施:符合CXL 2.0标准并投入生产的器件可能具有3.0功能,这反映了该规范的高速发展,Orthodoxou表示。混合实施和功能蔓延可能会阻碍互操作性,这突显了在企业级别进行大规模互操作性测试的必要性,特别是因为CXL的价值在于数据中心,而互操作性是数据中心的必备条件。

CXL互操作性是Astera Labs扩展其云规模互操作实验室(Cloud-Scale InterOp Lab)的驱动力,旨在为客户提供强大的互操作性测试,该公司产品管理副副总裁Ahmad Danesh表示。

“当出现新技术时,互操作性对于能够大规模推出某些产品至关重要。”他指出。

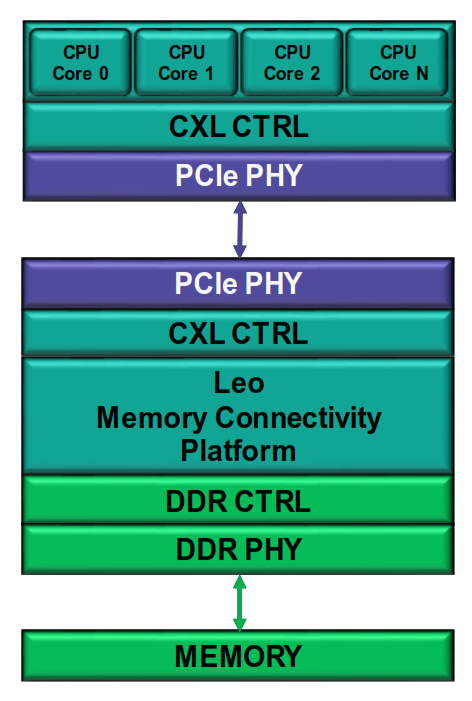

图2:Astera Labs扩展了其互操作实验室功能,将CXL纳入其中,以使其客户能够测试从物理层一直到应用层的所有内容,包括PCIe电气、DDR物理层和DDR控制器。(图片来源:Astera Labs)

该公司拥有自己的CXL内存连接平台,称为Leo,而随着产量的增加,就需要进行大量测试(图2)。Danesh表示,在数据中心,内存是服务器可靠性的核心器件,这在高可用性系统中是不可协商的。

在数据中心环境中实施CXL时,最根本的变化是从CPU到DDR子系统的传统路径的转变,这改变了测试职责的范式,Danesh表示。低延迟、可靠性和安全性都是Leo价值主张的一部分,但关键部分是无缝互操作性。验证互操作性可以加快Astera客户的上市时间,他指出。

作为串行接口,CXL很容易理解,并且与许多供应商一样,Astera研究PCIe和DDR链路已有一段时间了。将它们放在一起对客户来说是新鲜事。“最终,需要有人来做互操作工作。”Danesh表示,“互操作实验室降低了与互操作性相关的风险,使他们能够充满信心地部署CXL。”

Astera客户可以使用自动化实验室测试从物理层一直到应用层的所有内容,包括PCIe电气、DDR物理层和DDR控制器。场景包括注入误差并确保它们得到纠正,Danesh介绍道。除了测试是否符合CXL规范之外,Astera还使用行业标准工具进行完整的系统级测试。他指出,元器件会导致不同的排列。

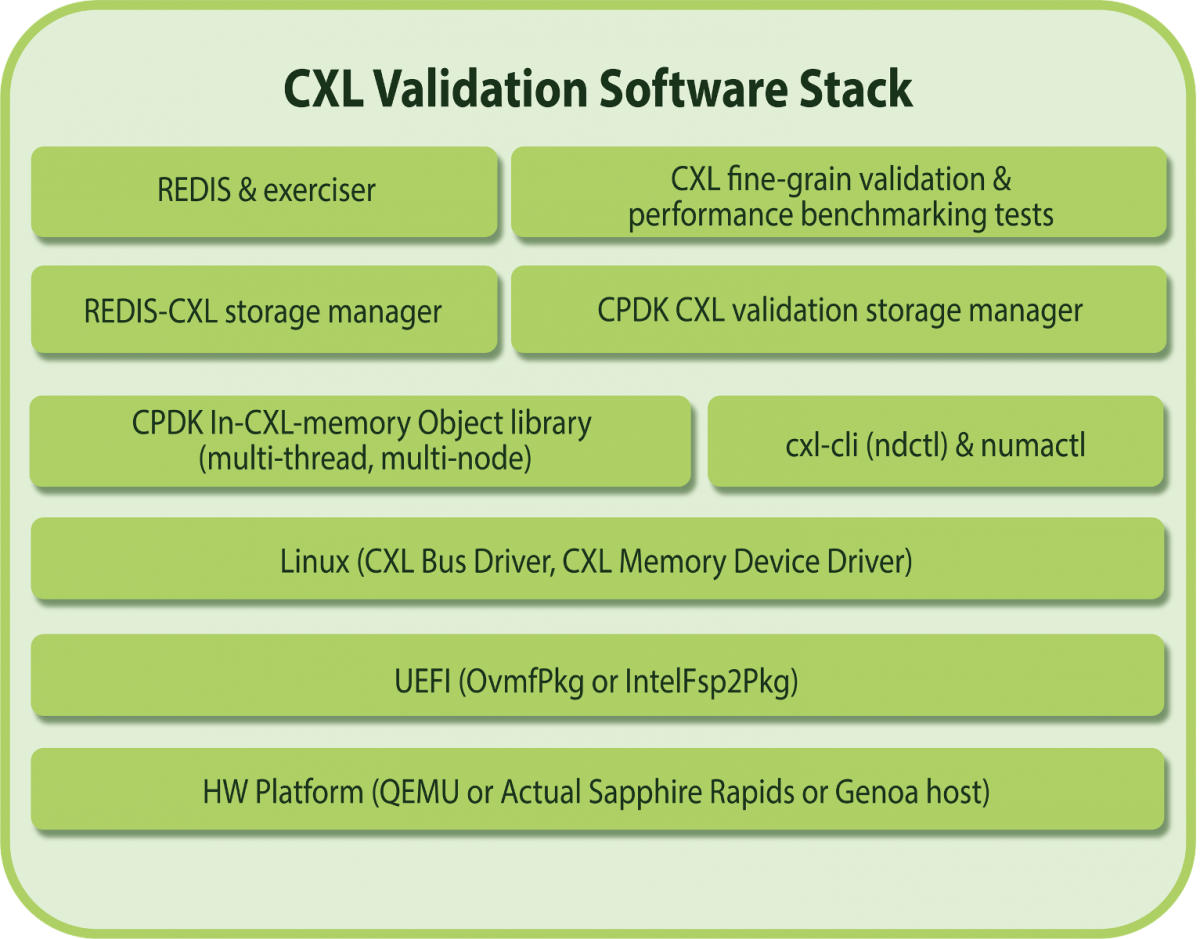

Astera只是提供CXL测试和验证方案的众多供应商之一。Avery Design Systems以其针对各种接口和规范的功能验证产品而闻名。该公司已将CXL添加到其名册中,并提供新的验证套件,以确保系统的互操作性、验证和系统性能基准测试。该套件涵盖了CXL标准从1.1到3.0的所有版本,以及投片前虚拟系统平台和投片后系统平台(图3)。

图3:Avery Design Systems以其功能验证产品而闻名,该公司推出了涵盖CXL标准从1.1到3.0的所有版本的CXL验证套件。(图片来源:Avery Design Systems)

无论测试和验证进行得多么顺利,这都是CXL联盟本身可以纳入规范的潜在反馈,该规范在最终确定之前有一个增量开发过程,CXL联盟技术工作组联合主席兼英特尔内存和I/O技术联合总经理Debendra Das Sharma向笔者表示。

“反馈是通过审查以及投片前和投片后验证持续产生的,因为成员会通过其演变来实施规范。”他表示,“任何需要澄清的反馈,例如解释不同排列的表格或不一致的问题都会得到解决。任何新功能请求都会根据规范的优点和成熟度进行考虑。”

最终规范发布后收到的任何反馈也会被跟踪,而新的功能请求可能会在联盟内部讨论后以ECN或下一个最终规范的形式出现。

“ECN对于之前的最终规范来说是可选的,但对于下一个最终规范可能会成为强制性的,”他补充道。这意味着CXL 3.0之后出现的ECN对于按照CXL 3.0规范设计的器件来说是可选的,但以后可能会成为CXL 4.0器件的强制要求。

Das Sharma表示,尽管CXL规范在相对较短的时间内取得了快速进展,但联盟的合规性章节与规范的其余部分同步发展。“我们有一个相当详细的合规章节,我们会预先考虑清楚。”他介绍说。

这要归功于联盟成员的经验,他们在数十年来在广泛的用途中拥有丰富的产品驱动经验。“我们将这一点纳入规范中,因此合规性测试机制可以跟上规范的快速演变和扩展,这是为了响应生态系统中对CXL解决广泛问题的巨大需求。”Das Sharma总结道。

(原文刊登于EDN姊妹网站EE Times,参考链接:CXL Testing Leverages PCIe Expertise,由Franklin Zhao编译。)

本文为《电子技术设计》2023年11月刊杂志文章,版权所有,禁止转载。免费杂志订阅申请点击这里。

最前沿的电子设计资讯

最前沿的电子设计资讯