最近,佳能宣布推出了一款能够制造尖端芯片的纳米压印设备FPA-1200NZ2C,该设备可以大幅降低半导体制造商的生产成本以及耗电量,为小型半导体制造商提供了一条生产先进芯片的新途径。

纳米压印设备

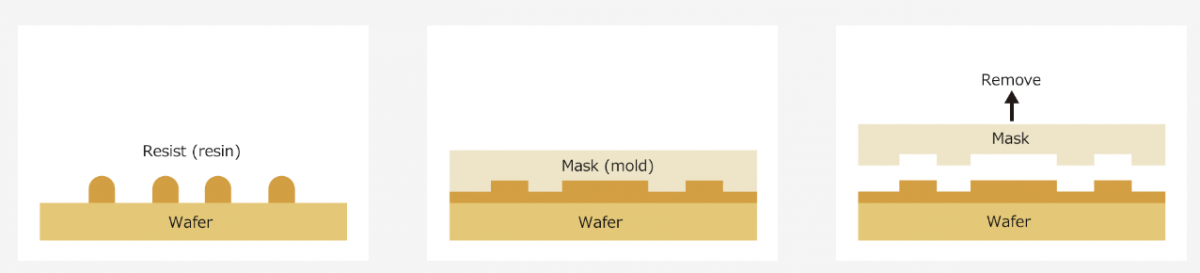

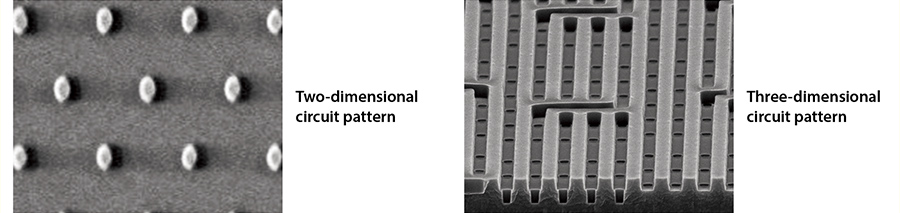

据了解,传统的芯片生产工艺是通过将掩模上的图形投影到硅片上,并使用紫外线照射硅片表面,来使其形成微小结构,而纳米压印技术则不同于传统的光学图像投影原理,使用的是一种类似于印刷的技术,在特定位置通过直接压印形成复杂的2D或3D电路图。具体来说,纳米压印工艺是将带有半导体电路图案的掩模压印在晶圆上,在一个印记内形成复杂的2D或3D电路图案,所以只需不断改进掩模,就可以生产出更小制程的芯片,甚至可以生产出2nm制程的产品。

纳米压印技术生产过程

据介绍,纳米压印设备构造简单,相较于传统刻烧电路的方法,纳米压印的耗电量可降至1/10,设备价格也会便宜很多。佳能估算,根据客户成本不同,单个压印工艺需要的成本可以降至传统设备的一半。

纳米压印技术生成的电路图案

不过距离该项技术实现普及还面临着不少难题需要解决,一方面在压印过程中容易产生叫做粒子的垃圾,这些粒子可能会损坏掩膜,所以需要提高去除微小粒子垃圾的技术,另一方面掩膜作为压印技术的关键,不但要提高掩膜的生产效率、降低生产成本,而且要尽可能地延长掩膜寿命。

据悉,佳能与大日本印刷株式会社以及铠侠控股合作研究纳米压印技术已有近十年时间,现今压印技术量产用途的实用化已有眉目,可以面向客户销售,并有望生产包括闪存、个人计算机DRAM和逻辑IC等各类半导体产品。

最前沿的电子设计资讯

最前沿的电子设计资讯