在1-35kV范围内的中压(MV)配电和电源转换应用中,一些电力电子应用包括用于太阳能等可再生能源系统的并网逆变器和DC/DC转换器、电源管理和中断器件(例如固态断路器)、用于直流微电网1的DC/DC转换器,以及需要双向逆变器的电池储能系统。

这些应用传统上依赖于硅(Si)基器件,例如绝缘栅双极晶体管(IGBT)。碳化硅(SiC)功率器件由于具有更宽的禁带宽度、更低的本征载流子密度、更高的热导率和更高的饱和速度等材料优势,因此与硅器件相比具有许多优点。这些优势包括:在给定额定电压下,具有更低的比导通电阻RDS(on);与硅相比,具有更高的额定电压(例如,SiC MOSFET的电压高达15kV,而Si IGBT的电压仅为6.5kV);在给定RDS(on)下,由于裸片尺寸更小,电容会低得多。将更低的传导和开关损耗、更高的开关频率和更简单的冷却要求等优势结合起来,可以降低电源转换损耗,提高效率、简化转换器拓扑结构、显著提高高温额定值和性能,并减小尺寸、重量和系统成本。

这些中压电网应用中使用的高压(HV,大于3.3kV额定值)SiC器件和模块的封装面临着一些挑战。本文总结了弗吉尼亚理工大学电力电子系统中心(CPES)的Christina DiMarino教授及其团队在高密度、高速10kV SiC电源模块封装方面所做的工作。CPES专注于改善电源处理和配电系统的研究和开发,包括电源转换架构、电力电子器件、建模、电能质量和高密度集成。

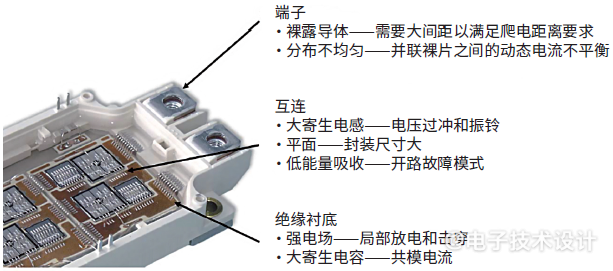

图1显示了上面讨论的一些挑战。

图1:电源模块封装面临的挑战。

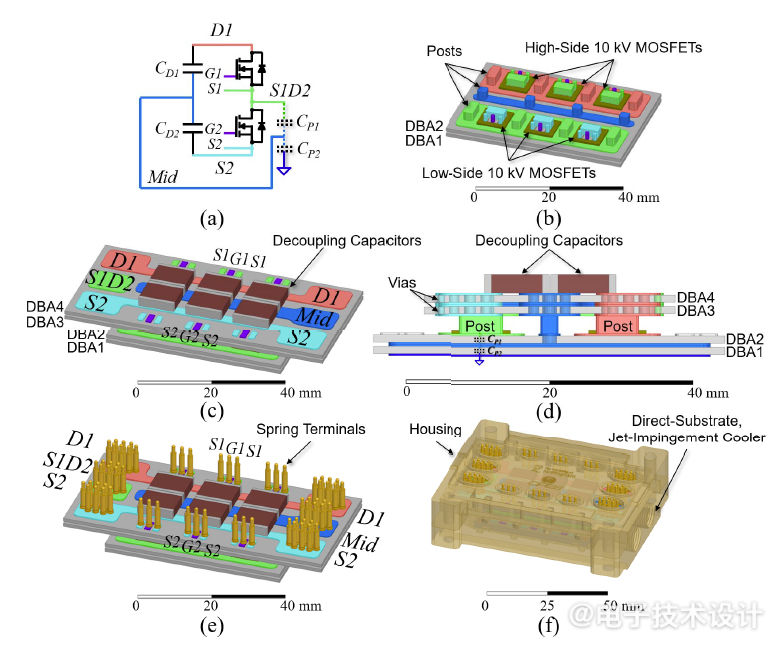

CPES的DiMarino团队为10kV、350mΩ SiC电源模块提出了一种创新的封装解决方案,该模块具有高开关速度、更高的HV性能和更低的CM电流6。还对该提出封装的关键方面进行了实验验证。图2显示了半桥模块的原理图和3D模型。

图2:提出的封装——(a)原理图;(b)底部堆叠衬底,内含六个10kV MOSFET裸片和柱子;(c)顶部堆叠衬底,内嵌去耦电容;(d)侧视图,显示了过孔和PCB;(e)带有弹簧端子的模块;(f)带集成直接衬底冷却器的外壳。

下面将讨论一些主要的设计和装配特点:

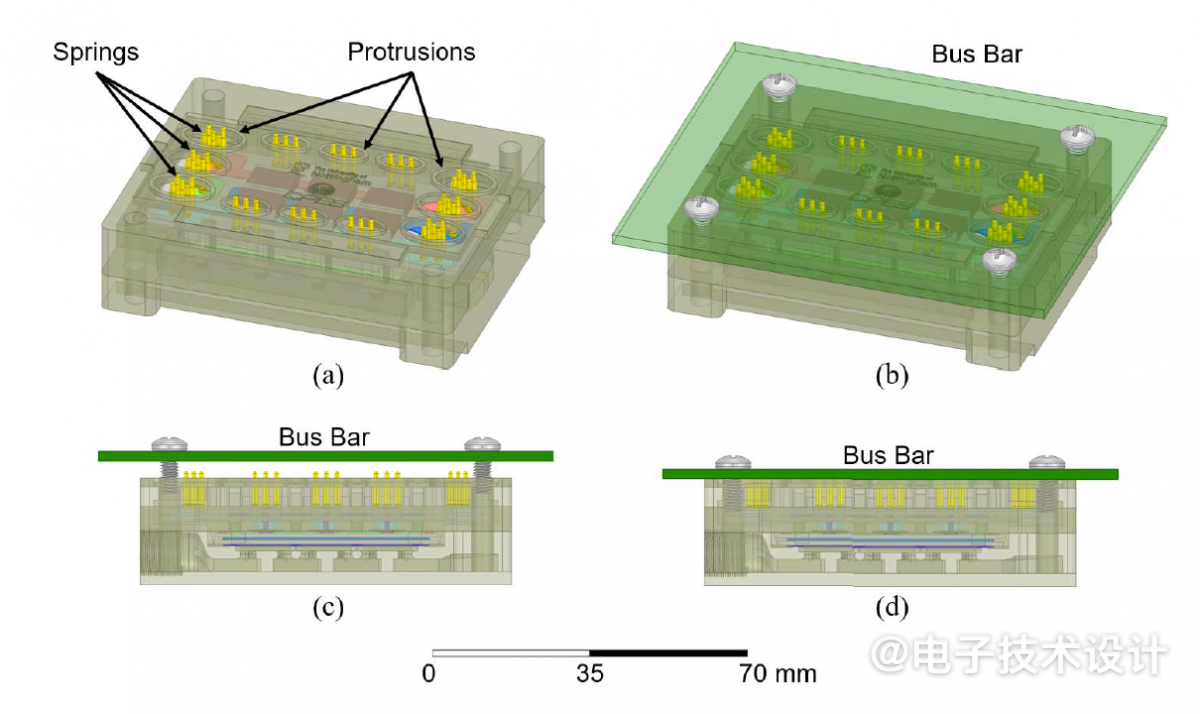

图3:外壳设计——(a)带外壳和盖子的模块;(b)带母线排的模块;(c)模块侧视图;(d)母线排压缩弹簧端子的模块。

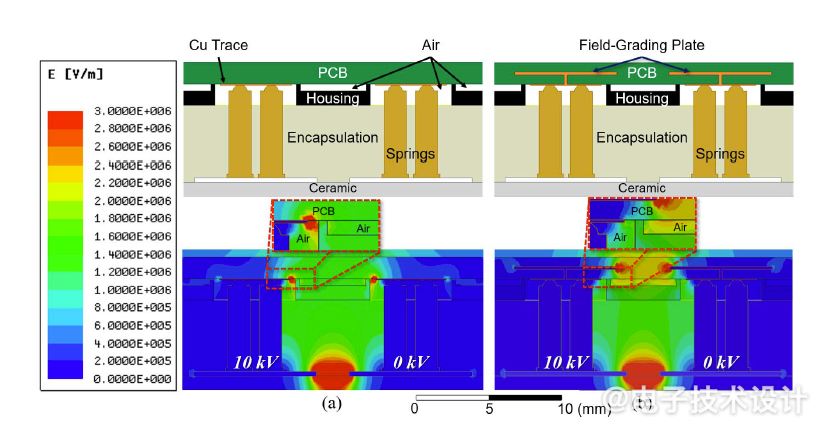

图4:电场分布模拟——(a)母线排PCB内无电场分级板;(b)母线排PCB内有电场分级板。

表1列出了模块原型的工艺步骤和所选材料。

表1:10kV SiC模块选择的封装工艺和材料。

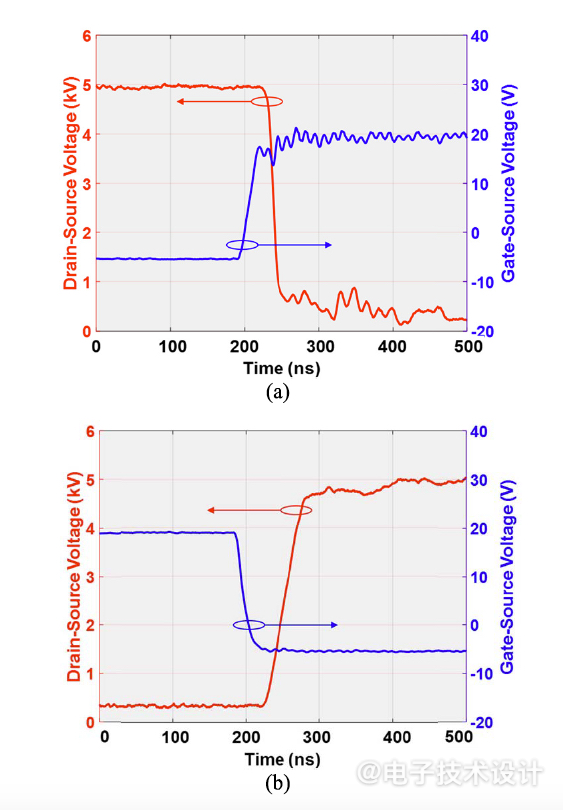

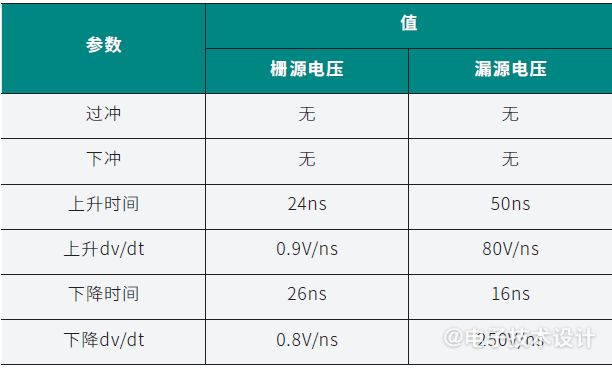

图5显示了使用两个10kV SiC MOSFET进行双脉冲测试时模块的开关性能。测试电压为5kV,电流为20A,导通和关断栅极电阻分别为0.33Ω和0.17Ω。表2列出了该测试的瞬态参数。观察到的过冲和振铃微乎其微,表明栅极回路和源极回路电感较低。这些结果是类似额定SiC MOSFET和IGBT的最快开关速度之一。

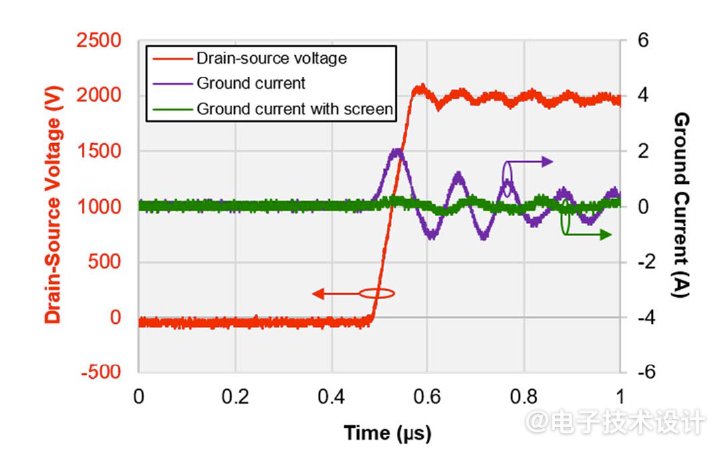

CM屏蔽层的有效性是在地通路中使用带宽为200MHz的RF电流互感器测量的。图6显示了三个并联MOSFET的关断波形。在2kV总线电压下,dv/dt为25V/ns。如图所示,CM屏蔽层将地电流过冲从2A降低至0.2A,验证了其有效性。

图5:10kV模块原型的开关波形。

表2:10kV、350mΩ SiC MOSFET模块原型开关结果。

图6:采用CM屏蔽和不采用CM屏蔽的地电流关断波形对比。

该团队使用50kV、60Hz交流激励源和PD传感器进行PD测试。这些测试是在内部堆叠衬底以及带有内部电场分级的PCB母线排上完成的。为了比较单一衬底与堆叠衬底,他们使用了1mm厚的金属走线之间间隔为2mm的图案化AlN-DBA衬底,其中中间金属的电压为所施加电压的一半。

如表3所示,与单衬底情况相比,当中间金属连接到所施加电压的一半时,堆叠衬底上的PDIV在空气中增加了53%,在封装情况下增加了40%以上。他们还使用PD测试验证了带有内部电场分级板的PCB母线排。如表3所示,母线排在空气中的PDIV值为12.4kV,在母线排上安装了PD虚拟模块后,空气中的PDIV值为11.6kV。

表3:局放测试总结。

原型模块的热特性分析表明,结点到环境的比热阻最低为26mm2·K/W(0.38K/W)11。

DiMarino总结道:“我们CPES为10kV SiC MOSFET提出了一种高密度、高速模块封装,可用于各种中压电源转换和配电应用。我们的封装方法侧重于低寄生效应、减少CM电流、实现高PD电压和降低热阻。这样,我们就能真正利用碳化硅材料的优异特性,在这一电压领域创造出高效的解决方案。”

1Wang, F., and Ji, S. (March 2021). “Benefits of high-voltage SiC-based power electronics in medium-voltage power-distribution grids.” Chinese Journal of Electrical Engineering, Vol. 7, No. 1.

2Haque et al. (1999). “An innovative technique for packaging power electronics building blocks using metal posts interconnected parallel plate structures.” IEEE Transactions on Advanced Packaging, Vol. 22, No. 2, pp. 136–144.

3Hoene, E., Ostmann, A., and Marczok, C. (February 2014). “Packaging Very Fast Switching Semiconductors.” 8th International Conference on Integrated Power Electronics Systems.

4Huber, T., Kleimaier, A., and Kennel, R. (September 2017). “Ultra-low inductive power module design with integrated common mode noise shielding.” 19th European Conference on Power Electronics and Applications.

5Bayer et al. (March 2016). “Enhancing partial discharge inception voltage of DBCs by geometrical variations based on simulations of the electric field strength.” 9th International Conference on Integrated Power Electronics Systems.

6DiMarino et al. (March 2020). “Design and Experimental Validation of a Wire-Bond-Less 10-kV SiC MOSFET Power Module.” IEEE Journal of Emerging and Selected Topics in Power Electronics, Vol. 8, No. 1, pp. 381–394.

7Passmore et al. (2016). “The next generation of high voltage (10 kV) silicon carbide power modules.” IEEE Workshop on Wide Bandgap Power Devices and Applications.

8Hohlfeld et al. (March 2012). “Stacked substrates for high voltage applications.” 7th International Conference on Integrated Power Electronics Systems.

9Domes, D. (May 14, 2013). Semiconductor arrangement. U.S. Patent 8441128B2.

10DiMarino et al. (October 2017). “Design of a novel, high-density, high-speed 10 kV SiC MOSFET module.” 2017 IEEE Energy Conversion Congress and Exposition.

11Mouawad et al. (May 2018). “Development of a highly integrated 10 kV SiC MOSFET power module with a direct jet impingement cooling system.” IEEE 30th International Symposium on Power Semiconductor Devices and ICs.

原文标题:

(原文刊登于EDN姊妹网站Power Electronics News,参考链接:SiC Power Module Packaging Solutions for MV Grid Applications,由Franklin Zhao编译。)

本文为《电子技术设计》2024年3月刊杂志文章,版权所有,禁止转载。免费杂志订阅申请点击这里。

最前沿的电子设计资讯

最前沿的电子设计资讯