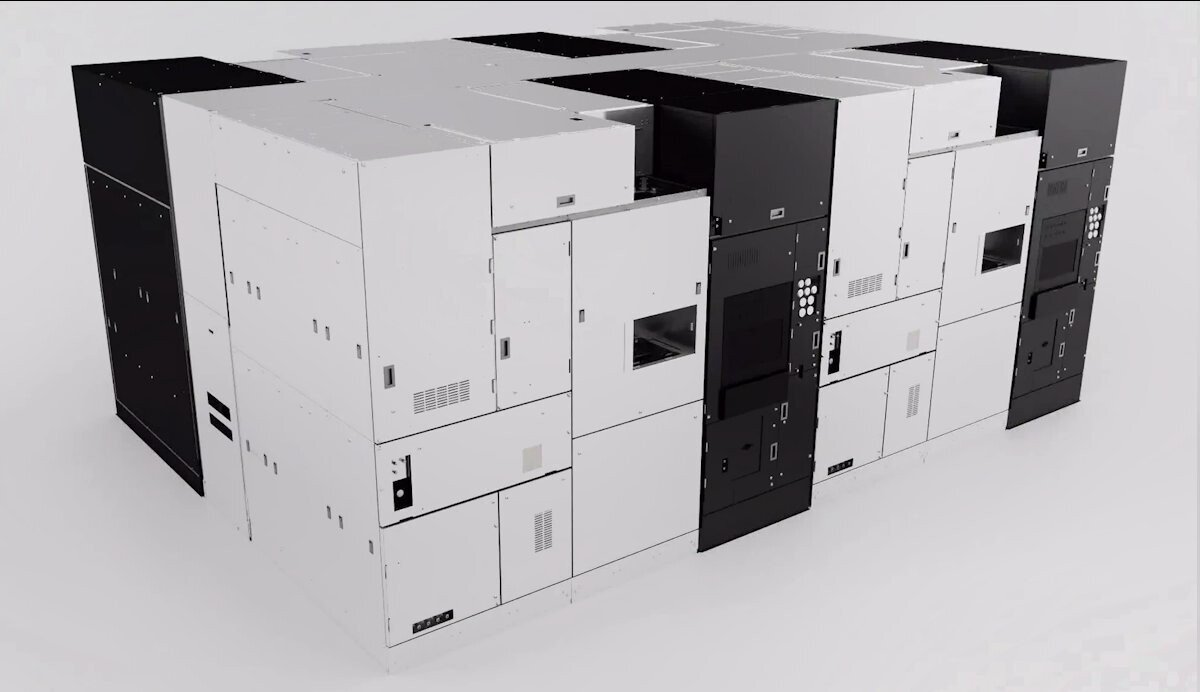

去年10月中旬,佳能公司宣布推出基于纳米压印的FPA-1200NZ2C,佳能表示,这套设备的工作原理和ASML的光刻机不同,并不利用光学图像投影的原理将集成电路的微观结构转移到硅晶圆上,而是更类似于印刷技术,直接通过压印形成图案,可以制造5nm芯片。

佳能最新消息表示,采用纳米压印技术的佳能光刻设备FPA-1200NZ2C目标今年或明年出货,值得一提的是,相较于目前已商用化的EUV光刻技术,尽管纳米压印技术的芯片制造速度要比传统光刻方式慢,但纳米压印技术的制程较为简单,耗电量可压低至EUV技术的10%,并让设备投资降低至仅有EUV设备的40%,它能让佳能压低竞争对手的价格,使尖端芯片生产平民化。

佳能负责纳米压印光刻技术开发的工业部门负责人竹西宏明(Hiroaki Takeishi)说:"我们希望在今年或明年......趁着市场热度开始出货。这是一项非常独特的技术,它将使尖端芯片的生产变得简单而低成本。纳米压印光刻机的半导体节点宽度为 5 纳米,目标是最终达到 2 纳米。"

Takeishi 说,这项技术主要解决了以前的缺陷率问题,但成功与否将取决于能否说服客户将其集成到现有的制造工厂是值得的。

据称,佳能最初专注于用此技术生产 3D NAND 存储器芯片,而不是复杂的处理器。Takeishi表示,佳能的纳米压印技术经过 15 年多的研发,如果能成功实现商业化应用,将能改变竞争格局,使新的竞争者能够以更低的成本生产领先的半导体产品。但是,新机器的缺陷率、集成挑战和地缘政治阻力能否让佳能在与芯片制造巨头的竞争中脱颖而出,还有待观察。

最前沿的电子设计资讯

最前沿的电子设计资讯