代表着数十亿美元市场潜力的芯粒设计运动正在向前推进,关键构建模块已经就位,同时在台积电3nm等先进工艺节点上进行流片。这些多裸片封装器件现在可以在不同的工艺节点中混合和匹配预制或定制的计算、内存和I/O成分,为系统级封装(SiP)成为未来的系统主板铺平道路。

与传统的片上系统(SoC)设计相比,芯粒还有望大大降低成本并提高产量。研究机构Transparency Market Research预测,到2031年,芯粒市场规模将达到470亿美元以上,成为半导体行业增长最快的细分市场之一,2021年至2031年年均复合增长率将超过40%。

以下的一些轶事展示了支持芯粒的硅片平台如何在封装、内存带宽和应用优化IP子系统等领域取得长足进步。

虽然芯粒设计通常与先进的封装技术有关,但一种新的物理层(PHY)解决方案声称已利用标准封装创建了一个多裸片平台。Eliyan公司的NuLink PHY在3nm工艺上实现了64Gbps/凸点的带宽,同时采用了8-2-8堆叠的标准有机/层压封装。

在实际的封装结构中有效组合计算密度和内存带宽,将大幅提高每美元性能和每瓦性能。此外,采用标准有机封装的基于芯粒的系统能够创建更大的SiP解决方案,从而以低得多的成本和系统级功耗实现更高的单位功率性能。

图1:采用标准封装的芯粒可促进其在推理和游戏应用中的使用。(来源:Eliyan)

Eliyan已宣布在3nm节点上流片了这种裸片间连接PHY,预计首款芯片将于2024年第三季度面世。该流片包括一个裸片到裸片PHY和一个适配器层/链路层控制器IP,以促进完整的解决方案。

芯粒通常是高性能计算(HPC)应用的代名词,这些多裸片器件的价格在几十到几百美元不等。YorChip与Siloxit两家公司联手开发了一种数据采集芯片,批量目标价格在1美元以下。

两家公司将利用低成本的裸片间链路、物理不可克隆功能(PUF)安全技术和Δ-Σ模数转换器(ADC)IP来创建成本优化的芯粒。该芯粒旨在开发低成本裸片到裸片封装,比竞争对手节省75%的尺寸。

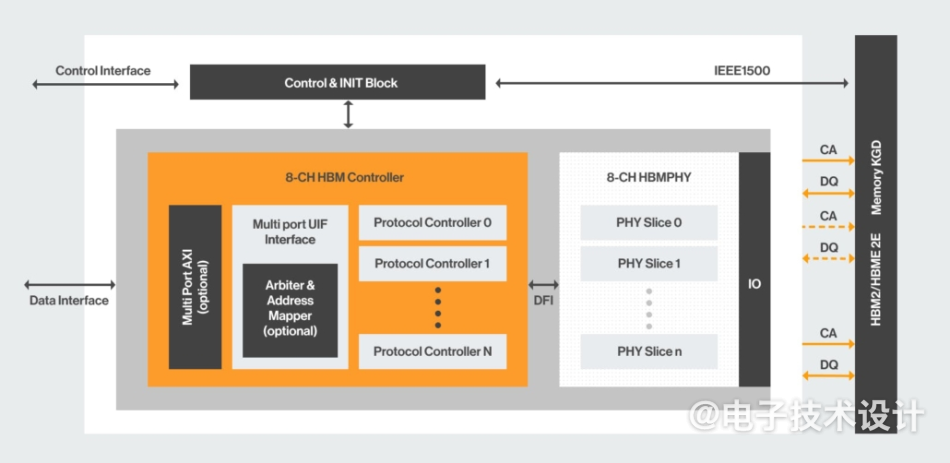

在芯粒设计中,内存带宽是与计算密度和高速I/O并列的主要考虑因素。这使得高带宽内存3(HBM3)PHY成为了生成式人工智能(AI)和云计算等应用中芯粒的关键组成部分。在每瓦内存带宽是关键性能指标的HPC系统中,情况尤其如此。

图2:HBM3内存子系统支持每个数据引脚高达8.4Gbps的数据速率,并具有16个独立通道,每个通道包含64位,总数据宽度为1,024位。(来源:Alphawave Semi)

Alphawave Semi公司推出了一款HBM3 PHY IP,其目标是高达8.6Gbps和16通道的高性能存储器接口。该HBM子系统将HBM PHY与符合JEDEC标准的高可配置HBM控制器集成在一起。它已在台积电的3nm节点上流片,专为超大规模和数据基础设施设计量身定制。

(原文刊登于EDN美国版,参考链接:Chiplets diary: Three anecdotes recount design progress,由Franklin Zhao编译。)

最前沿的电子设计资讯

最前沿的电子设计资讯