在上一期文章中,我们学习了模型级和子电路级的电子元件的导入操作。在本文中,我们将使用QSPICE内置库中的组件进行一些电源电路分析。在简要概述内置库中可用的功率器件后,我们将对基本电源电路进行一些分析,看一看所使用的软件在此类仿真中具有多高的质量。

QSPICE在其首次发布时就包含了一个功率半导体元件库,目前,至少在本文撰写之日,该软件为用户提供了一个内置且易于使用的库,其中包含以下功率器件类别:

在库中选择一些功率器件是设计工作系统的一个很好的起点。这些元器件可用于创建电源、逆变器和稳压器等基本电路。而每当需要特定的组件模型时,您都可以从外部文件导入它。如果你想使用默认库中没有的元件,这将非常有用。

对于本文中的示例,将使用QSPICE库中已存在的SiC FET UF3C120400K3S。该器件采用TO-247-3L封装,具有超低栅极电荷和出色的反向恢复特性,非常适合开关电感负载和所有需要标准驱动的应用。根据其官方数据表(请用户仔细阅读此文档),以下是一些最有用和最重要的参数,设计人员必须了解这些参数才能进行连贯且无差错的设计:

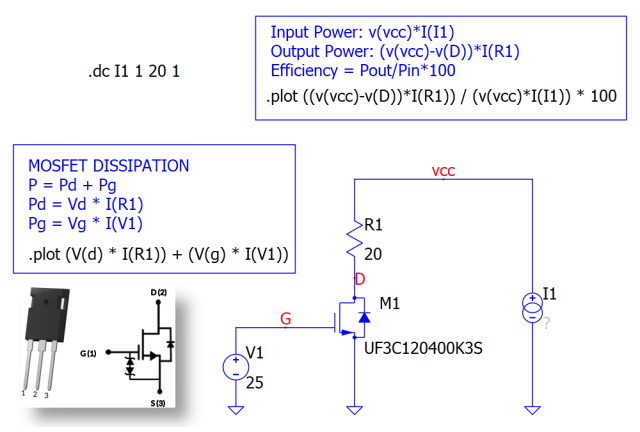

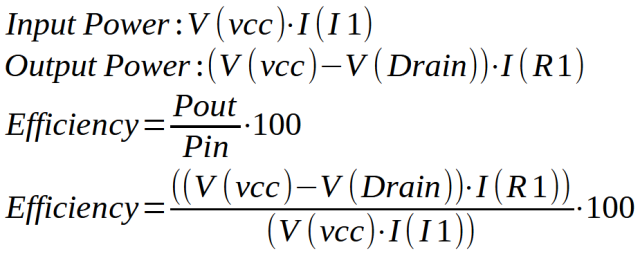

图1显示了一个为20Ω电阻负载(R1)供电的测试电路。该方案由电流发生器(I1)、驱动栅极的电压发生器(V1)和型号为UF3C120400K3S的M1器件组成。栅极始终通电,因此,FET始终导通。该仿真通过SPICE指令检查电源电流在1A到20A之间的电路的连续性:

.dc I1 1 20 1

并通过“.plot”指令显示相关的波形图。

图1:PWM发生器的电路图

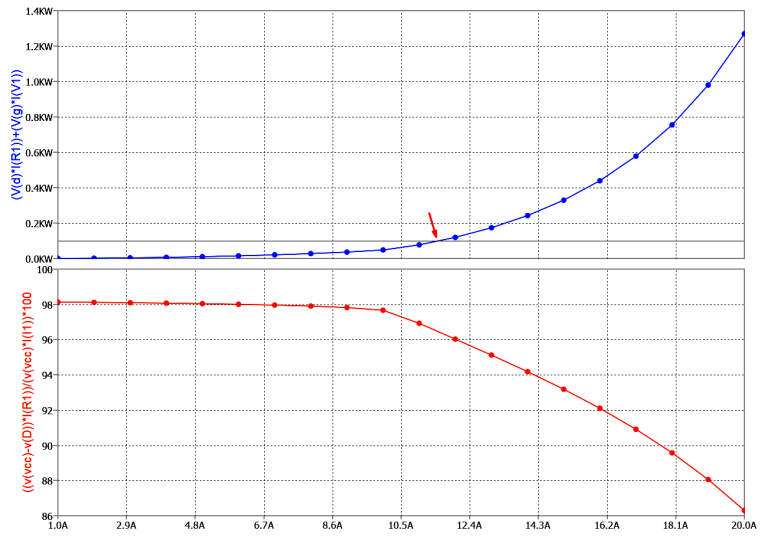

图2所示的图形突出显示了电路的两个重要参数:

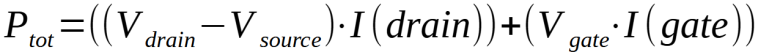

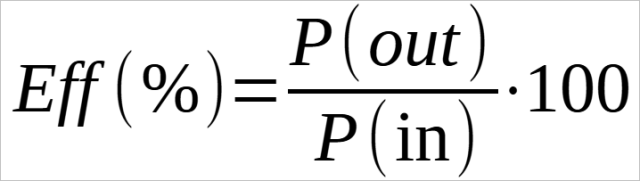

相对于顶部的第一张图,UF3C120400K3S SiC FET的功耗是通过改变其漏极上的电流来显示的。仿真特意包含了比组件本身可以承受的高得多的功耗。幸运的是,这可以在仿真中实现。SiC FET的功耗计算如下:

实际上,仅考虑漏极电压和漏极电流的乘积,因为栅极电流无关紧要,只有纳安量级。请记住,FET允许的最大功率为100W,在仿真中故意超出该值,是为了分析过载情况下电路的行为。这有助于发现潜在的电路可靠性或安全性问题。相对于下图,电路的效率根据以下通用公式确定:

尤其是:

从效率图(下图红色部分)可以看出,制造商认可的整个功率范围内的平均效率约为98%,这是一个非常出色的效率。但如果FET消耗的功率开始超过100W(相关数据表中规定的限制),系统的效率就会开始急剧下降,达到不再是最佳且危险的值。在这种情况下,器件还可能因发热而损坏。

图2:FET功耗(上)和系统效率(下)图

PWM发生器产生的数字信号由一系列幅度相等但宽度可变的脉冲组成。脉冲宽度(即占空比)决定了等效仿真信号的强度。它可用于控制各种设备的功率输出,例如电动机、LED、灯具、镇流器等。通过适当调整高电平信号(Ton)和低电平信号(Toff)的持续时间,可以轻松调整PWM信号的占空比。占空比越高,相当于模拟信号越强。需要注意的是,决定对负载的影响的不是信号的频率,而是有效脉冲的持续时间。

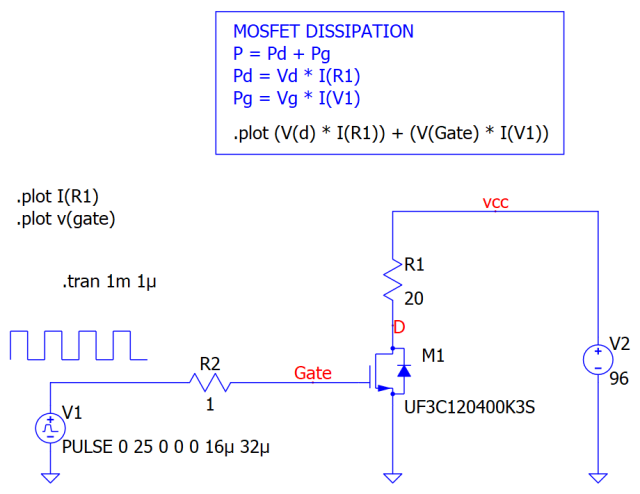

因此,在相同的占空比下,频率不同的两个信号会产生相同的效果。下面的示例(电路图见图3)涉及一个为电阻负载供电的PWM发生系统的仿真。V1发生器以约30kHz的频率发出占空比为50%的PWM信号,幅度(导通状态)为25V,适合驱动SiC FET的栅极。系统电源为96V,负载为20Ω。

图3:为电阻负载供电的PWM发生系统的电路图

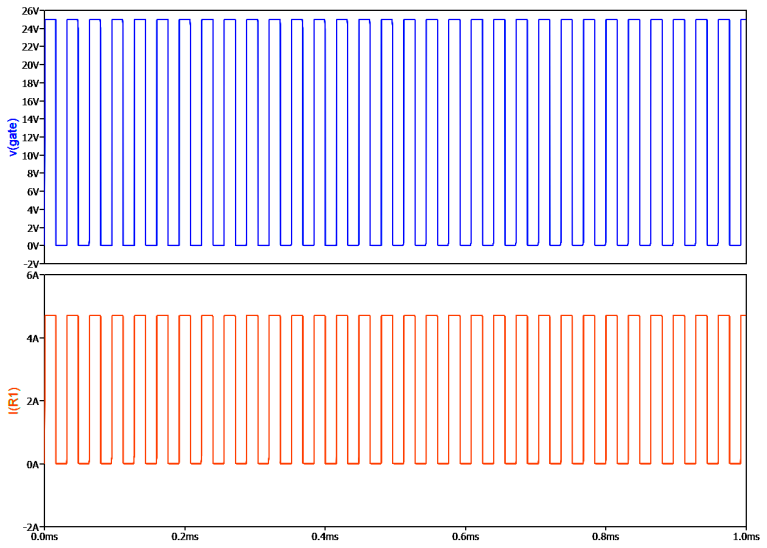

因此,PWM发生器会生成一个脉冲信号,ON状态在时间上相当于OFF状态,持续时间为16μs。观察图4中的信号图,乍一看,系统似乎是完美的,没有任何问题,并且其运行是最佳的。事实上,栅极电压(顶部)和负载电流(底部)的变化趋势非常平稳,没有明显的问题。

图4:负载电流图并未凸显出电路中存在的问题

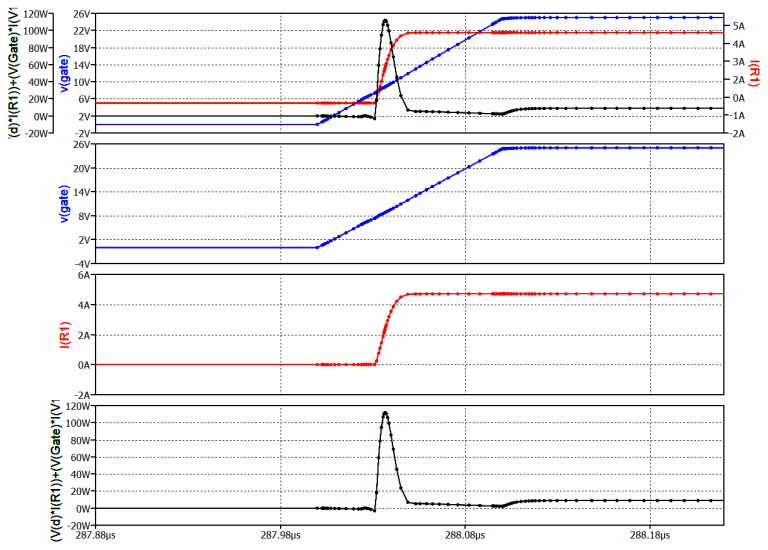

然而,必须注意的是,电子元件,尤其是开关元件,具有非理想特性,例如非零压降和非瞬时开关转换。这些特性会限制组件的运行,尤其是在高速或高能量水平下。只需查看SiC FET的功耗图,并放大信号上升沿或下降沿上的图,就能发现第一个问题。图5显示了上升沿对应的图形,显示的图线如下:

转变时间非常短,约为数十纳秒,但在这种情况下,FET呈线性状态,其开关是渐进的而不是立即的。因此,存在一个电流和电压同时为正的瞬态区,会产生致命的开关损耗。欧姆定律也证实了这一事实。现今,此类损耗是不可避免的,并且如前所述,发生在开关上升沿和下降沿。然而,有许多硬件和软件技术可以将其降低到可接受的水平。开关损耗虽然持续时间极短,但会对电压、电流和功率信号的平均值造成影响,并在射频级产生干扰。

图5:在器件的OFF-ON和ON-OFF转换过程中会出现重要的开关损耗

借助QSPICE,电力电子元件的仿真非常高效,最重要的是,不会出现其他仿真器常见的操作问题。它是一个有价值的工具,可以帮助设计人员创建更可靠、更安全的系统,而无需使用任何实际组件。通过这种方式,可以减少开发时间和成本,同时也降低了项目失败的风险。仿真可用于研究过载条件或通过改变几个参数来测试不同的开关操作速度。

(原文刊登于EDN姊妹网站Power Electronics News,参考链接:QSPICE: Power Circuit Analysis (Part 8),由Ricardo Xie编译。)

最前沿的电子设计资讯

最前沿的电子设计资讯